1

Изобретение относится к области импульсной техники и может использоваться в радиоэлектронных устройствах для регулируемой задержки случайной последовательности прямоугольных импульсов.

Известны устройства задержки импульсов, содержащие распределитель импульсов, ждущий генератор временных интервалов, состоящий из первой цепочки последовательно включенных k + п ячеек задержки, и блок логики, состоящий из дешифратора, к которому подключены выходы триггеров, к одним входам которых через логические схемы «ИЛИ подключены выходы второй цепочки последовательно включенных ячеек задержки, кроме первой и предпоследней.

Цель изобретения - повышение точности воспроизведения временных параметров случайной последовательности импульсов при увеличении значения задержки и расширение частотного диапазона.

Это достигается тем, что в предлагаемом устройстве выходы распределителя подключены к входам нечетных ячеек задержки первой цепочки задержки, выходы которых и выходы распределителя через логические схемы «И подключены к вторым входам триггеров, входы четных ячеек задержки первой цепочки подключены через логические схемы «И к выходам триггеров, а выход второй цепочки

задержки подключен к входу распределителя импульсов.

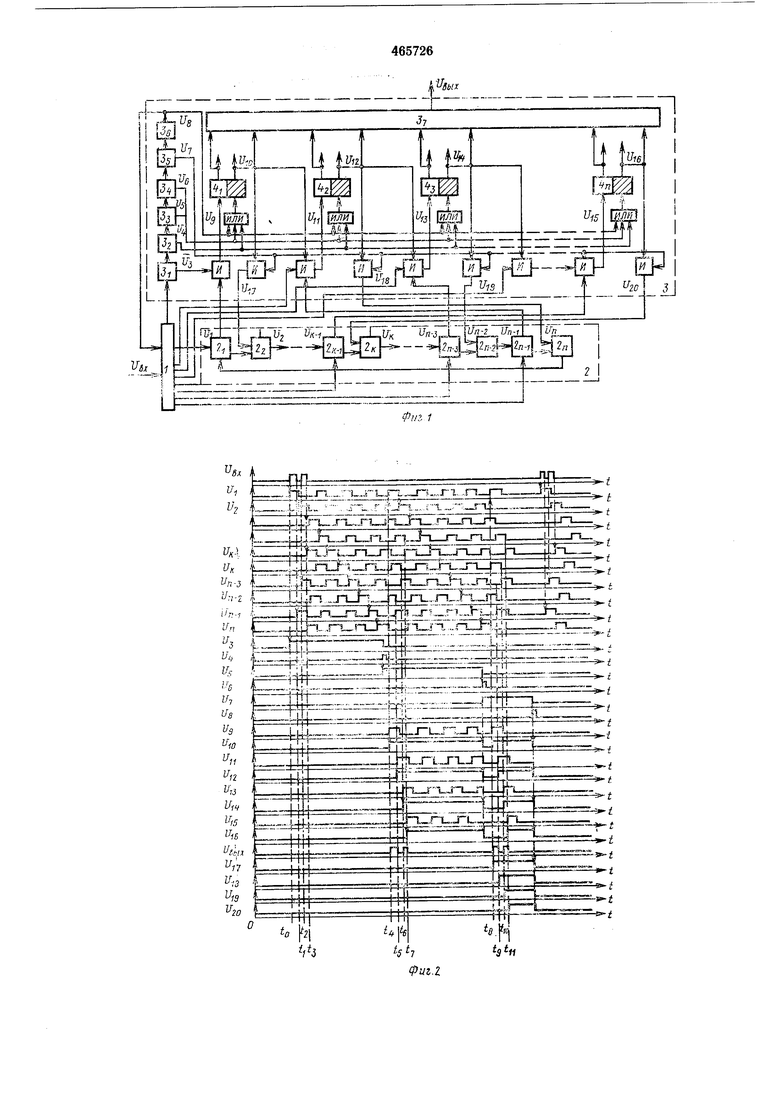

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - временные диаграммы напряжений в соответствующих точках устройства.

Устройство задержки импульсов состоит из распределителя импульсов 1, например счетчика импульсов с дешифратором, ждущего геператора 2 временных интервалов, образованного кольцевой схемой последовательно соединенных ячеек задержки 2i - 2„ (например, одновибраторов), и блока логики 3, состоящего, например, из ячеек задержки 3i - З, дешифратора 3, триггеров 4|-4„ с раздельным входом, логических схем «И, «ИЛИ.

Устройство работает следующим образом. Случайная последовательность прямоугольных импульсов поступает на вход распределителя импульсов 1, который распределяет перепады напряжений, соответствующие временным параметрам входной импульсной последовательности по входам ячеек задержки 2, 2fc-i, . . ., 2п-з, ждущего генератора 2 временных интервалов (см. фиг. 2; ячейка задержки 2i запускается от переднего фронта первого импульса, ячейка задержкц 2n- - от заднего фронта первого импульса, ячейка задержки 2п-з - от переднего фронта второго

импульса и т. д.). Ждущий генератор 2 временных интервалов входит в режим генерации (каждая последующая ячейка задержки запускается от заднего фронта импульса, сформированного предыдущей ячейкой задержки, см. фиг. 2).

От переднего фронта первого импульса последовательно запускаются ячейки задержки 3i - 3с блока логики 3 (диаграммы напряжений С/3- Us.}. Ячейка задержки 3i (инверсный вход СУз совместно с ячейкой задержки 2i ждущего генератора 2 временных интервалов посредством логической схемы «И формируют сигналы запуска триггера 4i (диаграммы напряжений С/ь Us, Ug). Запуск каждого следующего триггера происходит от сигналов предыдущего триггера и выходных сигналов ячеек задержки ждущего генератора 2 временных интервалов и распределителя импульсов 1, объединенных посредством логических схем «И (диаграммы напряжений UK, - f/ie).

На всех выходах распределителя импульсов 1, соединенных с логическими схемами «И, кроме выхода, соответствующего числу зафиксированных перепадов напряжений входной импульсной последовательности, присутствует логическая «1. Ячейки задержки Зг - Зе посредством логических схем «И, «ИЛИ формируют сигналы установки в исходное состояние триггеров (диаграммы напряжений U, Ue, Us) и распределителя импульсов (диаграмма Us).

Сигналы с выходов триггеров совместно с выходными сигналами ячейки ЗБ посредством логических схем «И формируют сигналы запрета (диаграммы напряжений Ui -С/2о), осуществляющие срыв генерации и подготовку ячеек задержки ждущего генератора 2 временных интервалов к приему очередной импульсной последовательности. Кроме того, выходные сигналы триггеров поступают в дещифратор Зт, формирующий выходные сигналы С/выхВремя задержки определяется задержкой в блоке логики 3 и может регулироваться количеством периодов, генерируемых ждущим генератором временных интервалов; количеством временных ячеек задержки п; длительностью импульсов, формируемых ячейками задержки ждущего генератора. Кроме того, возможна многократная задержка импульсов. Для нормальной работы устройства необходимо правильно выбрать временные параметры ячеек задержки (время восстановления при их разработке) или количество ячеек задержки.

При правильном выборе временных параметров время восстановления не зависит от временных параметров входной импульсной последовательности, и, следовательно, минимальная длительность задерживаемых импульсов (максимальная частота следования импульсов в задерживаемой последовательности) ограничена только частотными свойствами используемых элементов.

Предмет изобретения

Устройство задержки импульсов, содержащее распределитель импульсов, ждущий генератор временных интервалов, состоящий из первой цепочки последовательно включенных k + п ячеек задержки, и блок логики, состоящий из дешифратора, к которому подключены выходы триггеров, к одним входам которых через логические схемы «ИЛИ подключены выходы второй цепочки последовательно включенных ячеек задержки, кроме первой и предпоследней, отличающееся тем, что, с целью повыщения точности воспроизведения

временных параметров случайной последовательности импульсов при увеличении значения задержки и расширения частотного диапазона, выходы распределителя подключены к входам нечетных ячеек задержки первой цепочки

задержки, выходы которых и выходы распределителя через логические схемы «И подключены к вторым входам триггеров, входы четных ячеек задержки первой цепочки подключены через логические схемы «И к выходам

триггеров, а выход второ цепочки задержки подключен к входу распределителя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки импульсов | 1975 |

|

SU560330A1 |

| Устройство формирования и регенерации временных интервалов | 1974 |

|

SU507919A1 |

| Формирователь временного интервала | 1974 |

|

SU680159A2 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ГЕОМЕТРИЧЕСКИХ НЕРОВНОСТЕЙ КОЛЕСНЫХ ПАР ПОДВИЖНОГО СОСТАВА12 | 1973 |

|

SU384711A1 |

| Временной дискриминатор | 1975 |

|

SU566338A1 |

| Формирователь временного интервала | 1973 |

|

SU457175A1 |

| Преобразователь телевизионного стандарта | 1980 |

|

SU1238267A1 |

| Формирователь временного интервала | 1974 |

|

SU496669A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство для передачи многочастотных сигналов | 1983 |

|

SU1107328A1 |

Авторы

Даты

1975-03-30—Публикация

1973-01-26—Подача