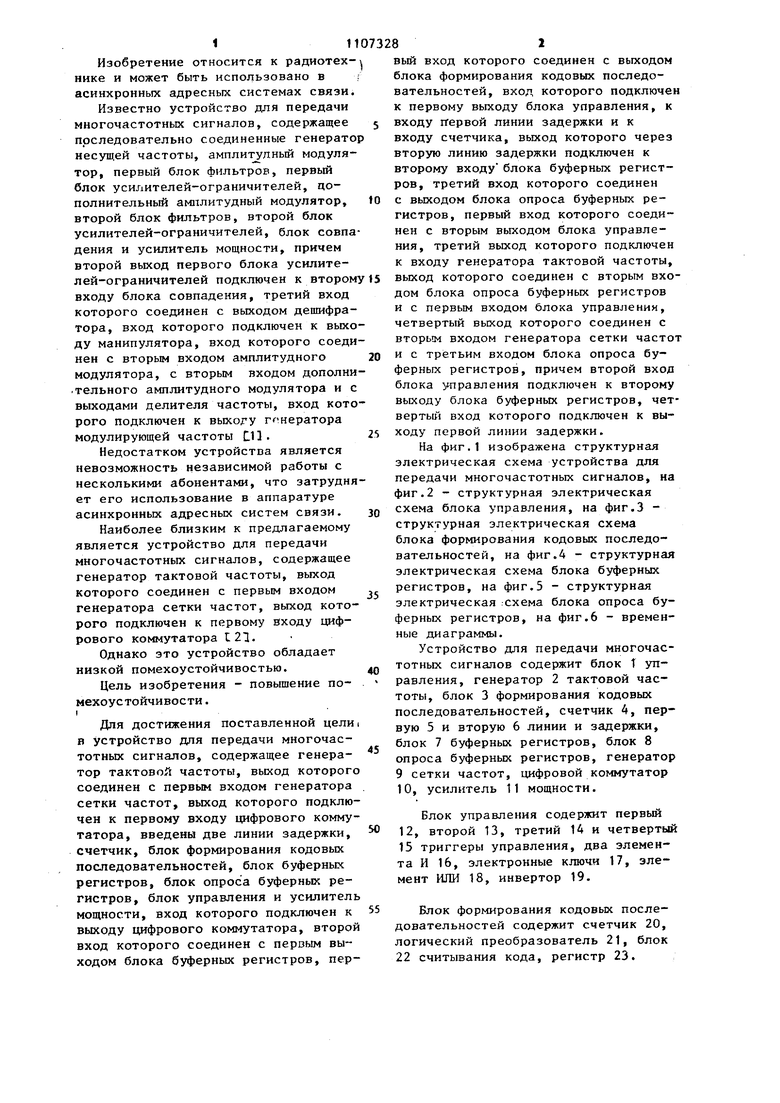

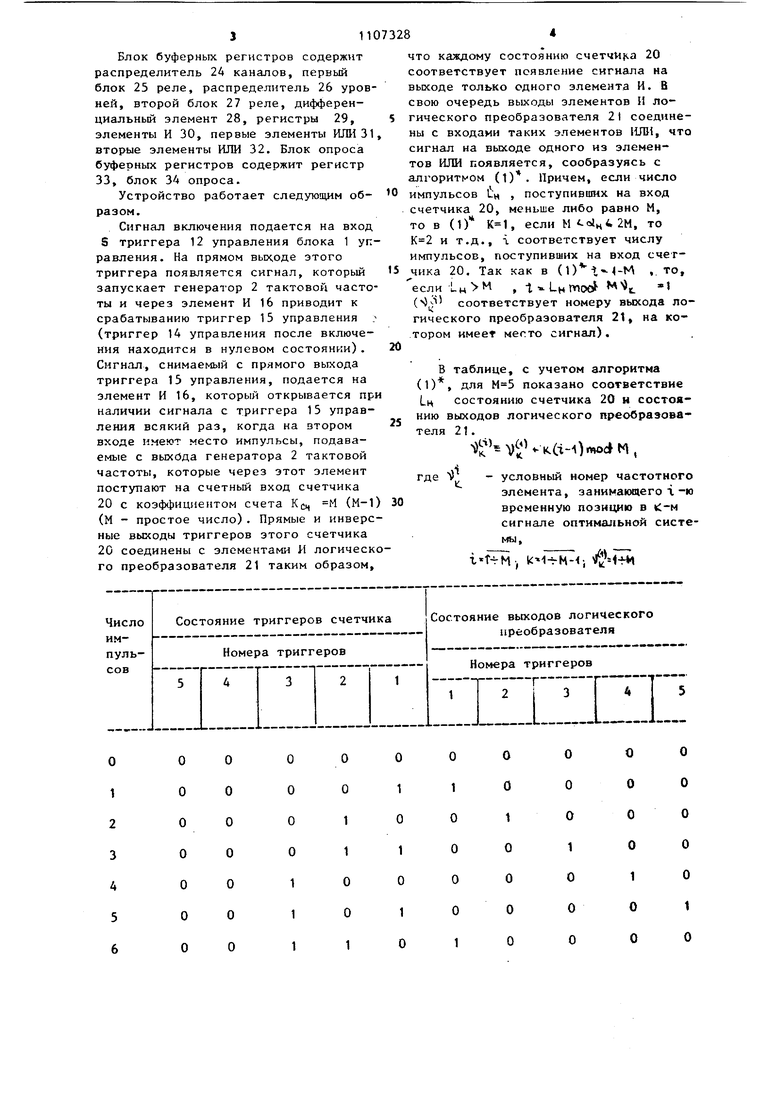

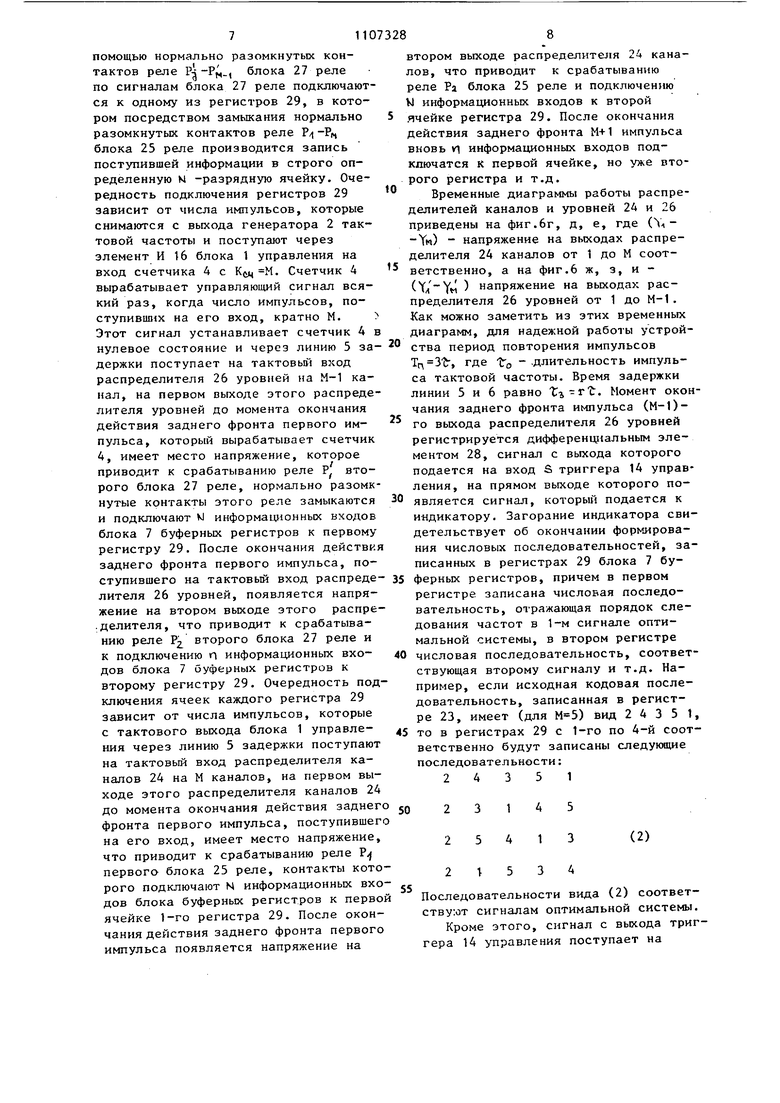

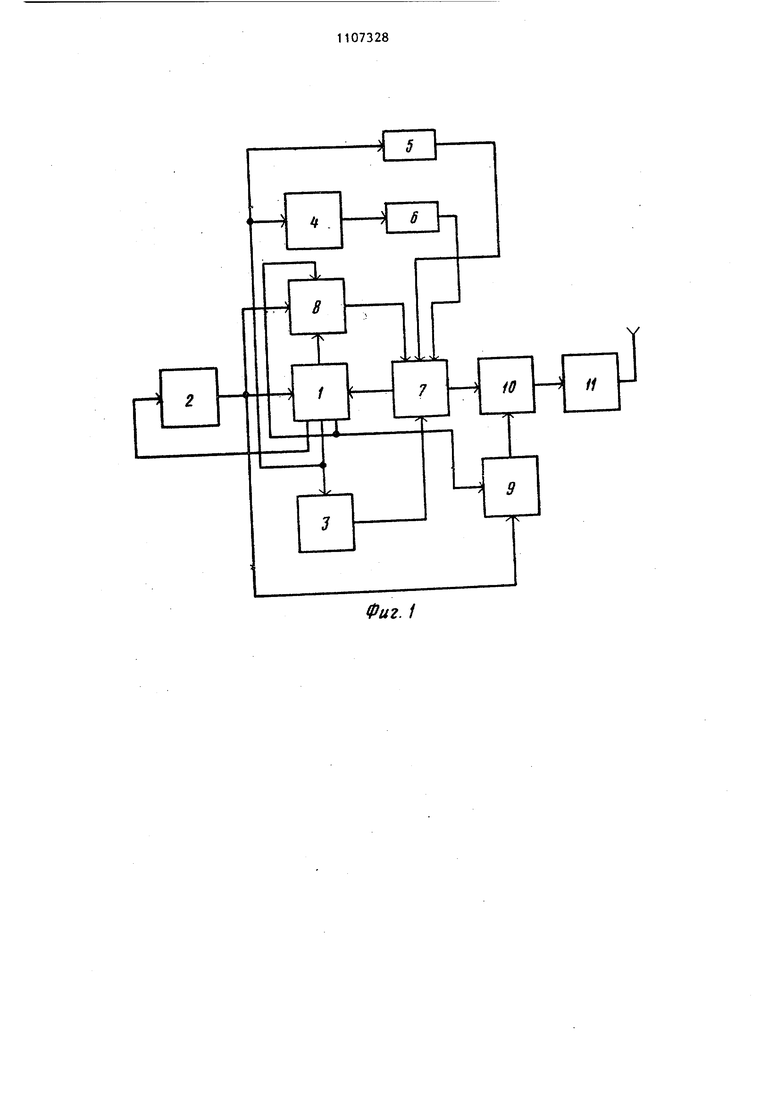

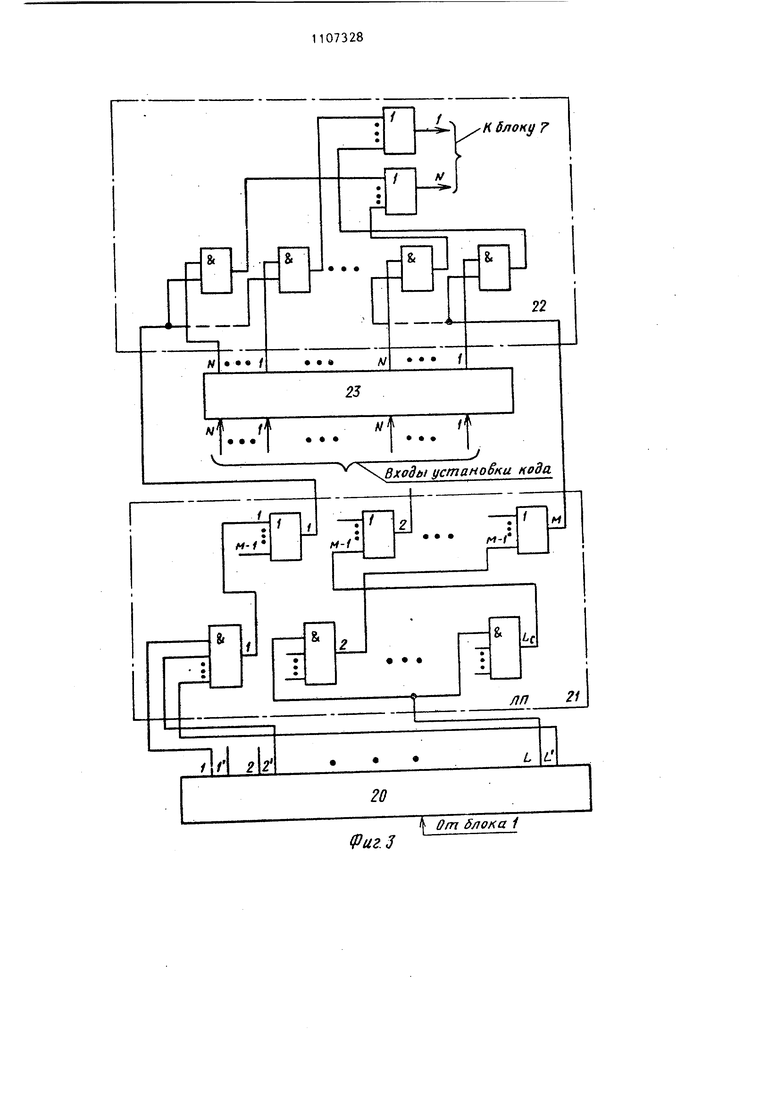

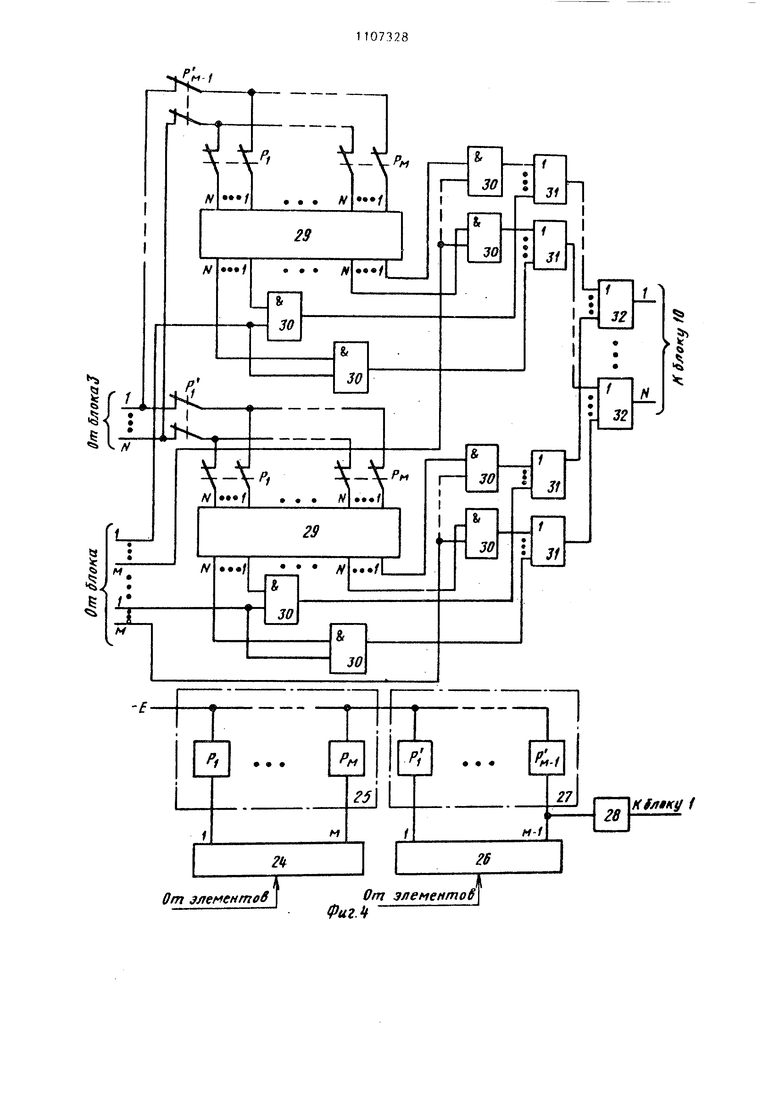

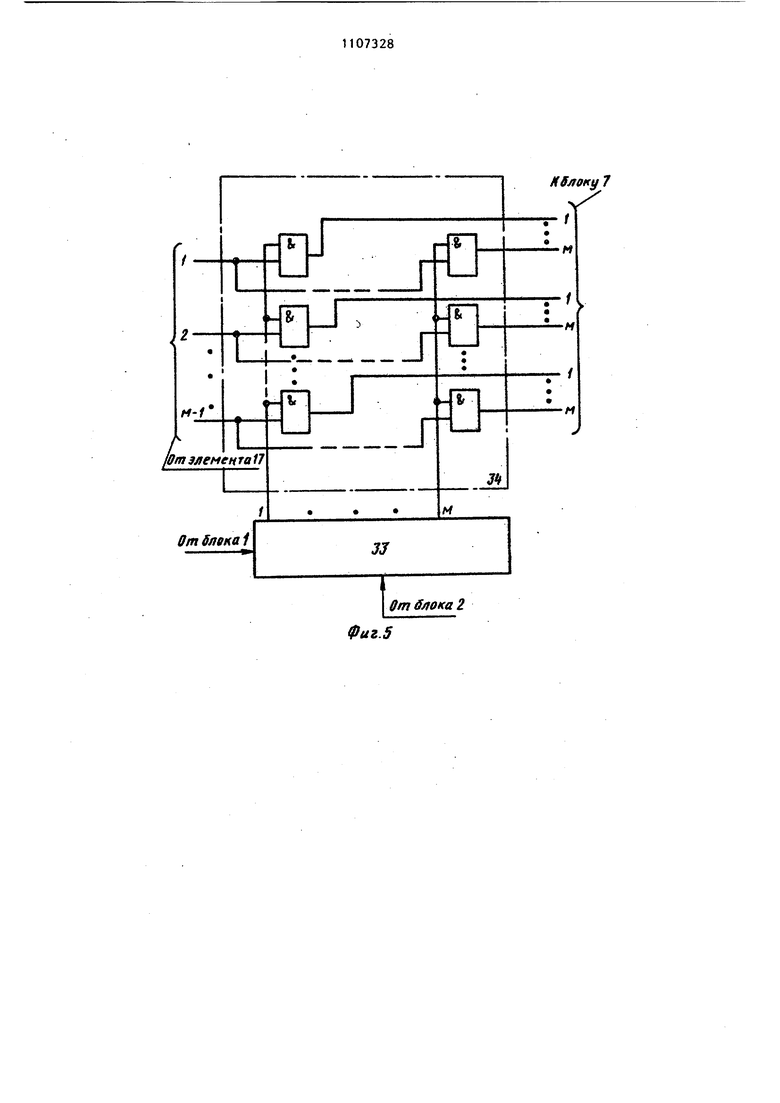

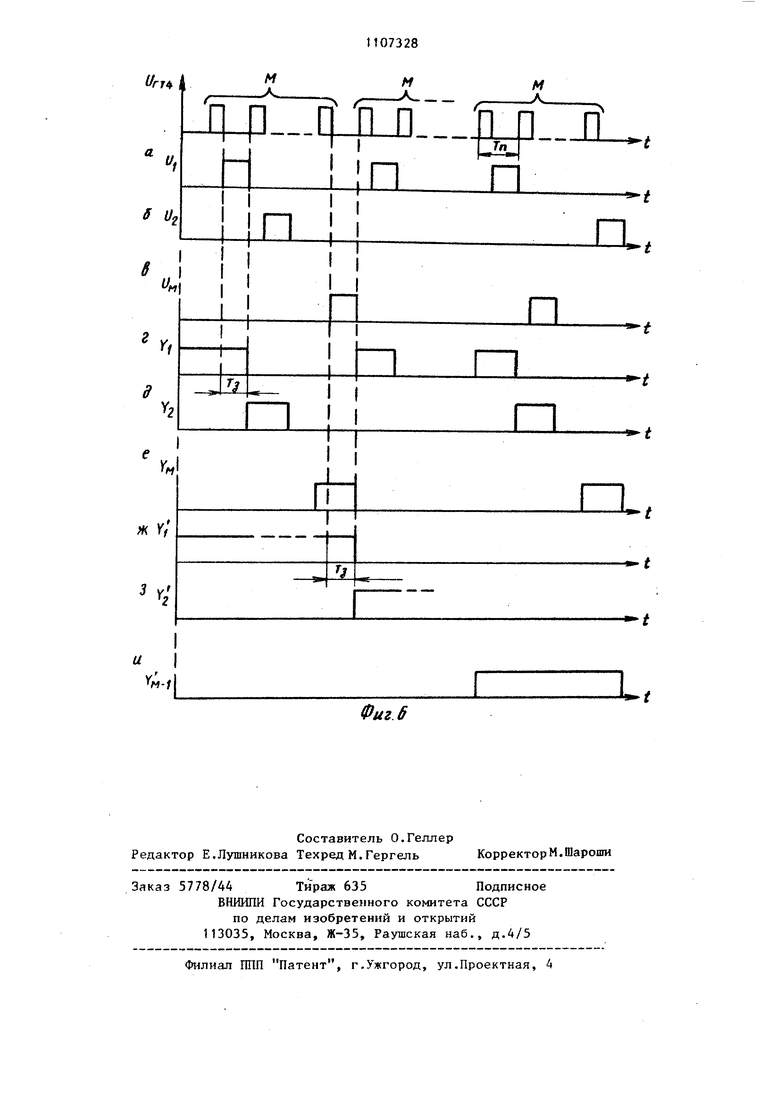

Изобретение относится к радиотехнике и может быть использовано в асинхронных адресных системах связи Известно устройство для передачи многочастотных сигналов, содержащее последовательно соединенные генерато несущей частоты, амплитудный модуля тор, первый блок фильтров, первый блок усилителей-ограничителей, дополнительный амплитудный модулятор, второй блок фильтров, второй блок усилителей-ограничителей, блок совпа дения и усилитель мощности, причем второй выход первого блока усилителей-ограничителей подключен к втором входу блока совпадения, третий вход которого соединен с выходом дешифратора, вход которого подключен к выхо ду манипулятора, вход которого соеди нен с вторым входом амплитудного модулятора, с вторым входом дополни .тельного амплитудного модулятора и с выходами делителя частоты, вход кото рого подключен к выхогу генератора модулирующей частоты СИ. Недостатком устройства является невозможность независимой работы с несколькими абонентами, что затрудня ет его использование в аппаратуре асинхронных адресных систем связи. Наиболее близким к предлагаемому является устройство для передачи многочастотных сигналов, содержащее генератор тактовой частоты, выход которого соединен с первым входом генератора сетки частот, выход которого подключен к первому входу цифрового коммутатора t21. Однако это устройство обладает низкой помехоустойчивостью. Цель изобретения - повышение помехоустойчивости. I Для достижения поставленной цели в устройство для передачи многочастотных сигналов, содержащее генератор тактовой частоты, выход которого соединен с первым входом генератора сетки частот, выход которого подключен к первому входу цифрового коммутатора, введены две линии задержки, счетчик, блок формирования кодовых последовательностей, блок буферных регистров, блок опроса буферных регистров, блок управления и усилитель мощности, вход которого подключен к выходу цифрового коммутатора, второй вход которого соединен с первым выходом блока буферных регистров, первый вход которого соединен с выходом блока формирования кодовых последовательностей, вход которого подключен к первому выходу блока управления, к входу первой линии задержки и к входу счетчика, выход которого через вторую линию задержки подключен к второму входублока буферньк регистров, третий вход которого соединен с выходом блока опроса буферных регистров, первый вход которого соединен с вторым выходом блока управления, третий выход которого подключен к входу генератора тактовой частоты, выход которого соединен с вторым входом блока опроса буферных регистров и с первьм входом блока управления, четвертый выход которого соединен с вторым входом генератора сетки частот и с третьим входом блока опроса буферных регистров, причем второй вход блока управления подключен к второму выходу блока буферных регистров, четвертый вход которого подключен к выходу первой линии задержки. На фиг.1 изображена структурная электрическая схема устройства для передачи многочастотных сигналов, на фиг.2 - структурная электрическая схема блока управления, на фиг.З структурная электрическая схема блока формирования кодовых последовательностей, на фиг.4 - структурная электрическая схема блока буферных регистров, на фиг.З - структурная электрическая схема блока опроса буферных регистров, на фиг.6 - временные диаграммы. Устройство для передачи многочастотных сигналов содержит блок Т управления, генератор 2 тактовой частоты, блок 3 формирования кодовых последовательностей, счетчик 4, первую 5 и вторую 6 линии и задержки, блок 7 буферных регистров, блок 8 опроса буферных регистров, генератор 9 сетки частот, цифровой коммутатор 10, усилитель 11 мощности. Блок управления содержит первый 12, второй 13, третий 14 и четвертый 15 триггеры управления, два элемента И 16, электронные ключи 17, элемент ИЛИ 18, инвертор 19. Блок формирования кодовых послеовательностей содержит счетчик 20, огический преобразователь 21, блок 22 считывания кода, регистр 23. 311 Блок буферных регистров содержит распределитель 24 каналов, первый блок 25 реле, распределитель 26 уров ней, второй блок 27 реле, дифференциальный элемент 28, регистры 29, элементы И 30, первые элементы ИЛИ 31 вторые элементы ИЛИ 32. Блок опроса буферных регистров содержит регистр 33, блок 3/4 опроса. Устройство работает следую цим образом. Сигнал включения подается на вход S триггера 12 управления блока 1 уп равления. На прямом выходе этого триггера появляется сигнал, который запускает генератор 2 тактовой часто ты и через элемент И 16 приводит к срабатыванию триггер 15 управления (триггер 14 управления после включения находится в нулевом состоянии). Сигнал, снимаемый с прямого выхода триггера 15 управления, подается на элемент И 16, который открывается пр наличии сигнала с триггера 15 управления всякий раз, когда на втором входе имеют место импульсы, подаваемые с выхсЗда генератора 2 тактовой частоты, которые через этот элемент поступают на счетньм вход счетчика 20 с коэффициентом счета М (М-1 (М - простое число). Прямые и инверс ные выходы триггеров этого счетчика 20 соединены с элементами И логическ го преобразователя 21 таким образом. что каждому состоянию счетчика 20 соответствует появление сигнала на выходе только одного элемента И. В свою очередь выходы элементов И логического преобразователя 21 соединены с входами таких элементов ИЛИ, что сигнал на выходе одного из элементов ИЛИ появляется, сообразуясь с алгоритмом (1). Причем, если число импульсов lln , поступивших на вход счетчика 20, меньше либо равно М, то в (1) , если , то и т.д., т. соответствует числу импульсов, поступивших на вход счетчнка 20. Так как в (О l 4- . то, если , t LnmtX t -1 С, соответствует номеру выхода логического преобразователя 21, на котором имеет мег.тчэ сигнал). В таблице, с учетом алгоритма (1), для показано соответствие LH состоянию счетчика 20 и состоянию выходов логического преобразователя 21. (i-l), где - условный номер частотного элемента, занимающего i-ю временную позицию в -м сигнале оптимальной системы, . K I-rH-i) lt Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1319305A1 |

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1354437A1 |

| Устройство для передачи многочастотных сигналов | 1987 |

|

SU1406817A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Приемник многочастотных сигналов | 1991 |

|

SU1775874A1 |

| Устройство синхронизации адаптивной системы связи | 1977 |

|

SU738184A2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| Устройство для сигнализации с индикацией местоположения аварийного объекта | 1982 |

|

SU1121689A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ МНОГОЧАСТОТНЫХ СИГНАЛОВ, содержащее генератор тактовой частоты, выход которого соединен с первым входом генератора сетки частот, выход которого подключен к первому входу цифрового коммутатора, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены две линии задержки, счетчик, блок формирования кодовых последовательностей, блок буферных регистров, блок опроса буферных регистров, блок управления и усилитель мощности, вход которого подключен к выходу цифрового коммутатора, второй вход которого соединен с первым выходом блока буферных регистров, первый вход которого соединен с выходом блока формирования кодовых последовательностей, вход которого подключен к первому выходу блока управления, к входу первой линии задержки и к входу счетчика, выход которого через вторую линию задержки подключен к второму входу блока буферных регистров, третий вход которого соединен с выходом опроса буферных регистров, первый вход которого соединен с вторым выходом блока управления, третий выход которого подключен к входу генератора г тактовой частоты, выход которого сое(Л динен с вторым входом блока опроса буферных регистров и с первьм входом блока управления, четвертый выход которого соединен с вторым входом генератора сетки частот и с третьим входом блока опроса буферных регистров, причем второй вход блока управления подключен к второму выходу блока буферных регистров, четвертый вход ко-, торого подключен к выходу первой линии падержки.

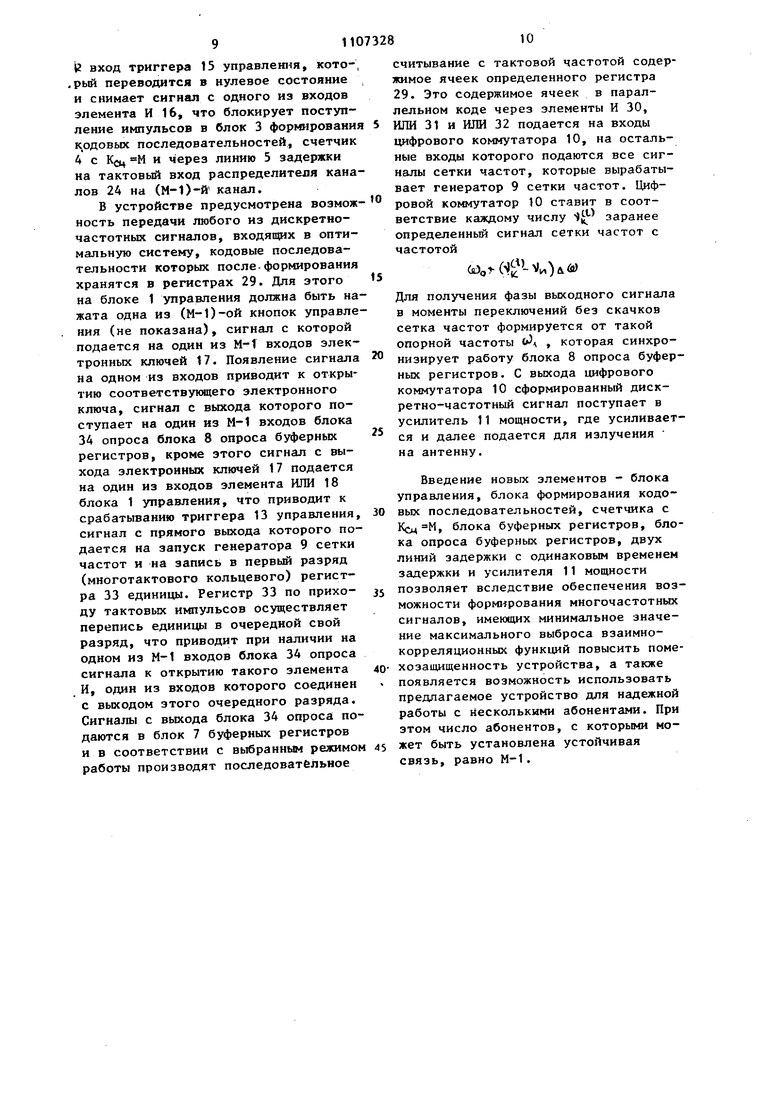

Диаграмма временной работы логического преобразователя 21 в зависимости от поступления тактовых импуль сов V,vi л вход счетчика через блок 1 управления приведена иа фиг.6 где а,сГ и &/u, напряжение на первом, втором и М-ом выходе логического преобразователя 21 соответственно. Сигналы, снимаемые с выходов логи ческого преобразователя 21, подаются в блок 22 считывания кода, который считьшает содержимое ячеек регистра 23, причем сигнал, поступающий с 1-го выхода логического преобразователя 21, считывает содержи юе первой ячейки регистра 23, сигнал с второго выхода - содержимое второй ячейки и т.д. В каждой ячейке регистра 23 может быть записано в двоичном коде одно из десятичных чисел от 1 до М, при этом в двух произвольно выбранньэс ячейках не допускается запись одинаковых чисел, а порядок записи чисел во все ячейки регистра 23 произвольный. Например, при в ячейки регистра 23, расположенные в порядке возрастания, могут быть записаны числа 2,3,5,4,1. Запись чисел в регистр 29 осуществляется от ключей начальной установки. После считывания содержимое ячейки регистра 23 через блок 22 считывания кода в параллельном коде подается на N информационных входов блока 7 буферных регистров. Эти входы с помощью нормально разомкнутых контактов реле Рч-Р., блока 27 реле по сигналам блока 27 реле подключают ся к одному из регистров 29, в котором посредством замыкания нормально разомкнутых контактов реле блока 25 реле производится запись поступившей информации в строго определенную N -разрядную ячейку. Очередность подключения регистров 29 зависит от числа импульсов, которые снимаются с выхода генератора 2 тактовой частоты и поступают через элемент И 16 блока 1 управления на вход счетчика 4 с М. Счетчик 4 вырабатывает управляющий сигнал всякий раз, когда число импульсов, поступивших на его вход, кратно М. Этот сигнал устанавливает счетчик 4 нулевое состояние и через линию 5 за держки поступает на тактовый вход распределителя 26 уровней на М-1 канал, на первом выходе этого распреде лителя уровней до момента окончания действия заднего фронта первого импульса, который вырабатывает счетчик 4, имеет место напряжение, которое приводит к срабатыванию реле р второго блока 27 реле, нормально разомк нутые контакты этого реле замыкаются и подключают W информадаонньк входов блока 7 буферных регистров к первому регистру 29. После окончания действи заднего фронта первого импульса, поступившего на тактовьй вход распреде лителя 26 уровней, появляется напряжение на втором выходе этого распре.делителя, что приводит к срабатыванию реле Р второго блока 27 реле и к подключению п информационных входов блока 7 буферных регистров к второму регистру 29. Очередность подключения ячеек каждого регистра 29 зависит от числа импульсов, которые с тактового выхода блока 1 управления через линию 5 задержки поступают на тактовый вход распределителя каналов 24 на М каналов, на первом выходе этого распределителя каналов 24 до момента окончания действия заднего фронта первого импульса, поступившего на его вход, имеет место напряжение, что приводит к срабатыванию реле Р первого блока 25 реле, контакты которого подключают N информационных вхо- jj дов блока буферных регистров к первой ячейке 1-го регистра 29. После окончания действия заднего фронта первого импульса появляется напряжение на втором выходе распределителя 24 каналов, что приводит к срабатыванию реле Ра блока 25 реле и подключению VI информационных входов к второй ячейке регистра 29. После окончания действия заднего фронта М+1 импульса вновь VI информационных входов подключатся к первой ячейке, но уже второго регистра и т.д. Временные диаграммы работы распределителей каналов и уровней 24 и 26 приведены на фиг.бг, д, е, где () напряжение на выходах распределителя 24 каналов от 1 до М соответственно, а на фиг.6 ж, 3, и напряжение на выходах распределителя 26 уровней от 1 до М-1. Как можно заметить из этих временных диаграмм, для надежной работы устройства период повторения импульсов , где fo .длительность импульса тактовой частоты. Время задержки линии 5 и 6 равно Момент окончания заднего фронта импульса (М-1)го выхода распределителя 26 уровней регистрируется дифференц11альным элементом 28, сигнал с выхода которого подается на вход S триггера 14 управления, на прямом выходе которого появляется сигнал, который подается к индикатору. Загорание индикатора свидетельствует об окончании формирования числовых последовательностей, записанных в регистрах 29 блока 7 буферных регистров, причем в первом регистре записана числовая последовательность, отражающая порядок следования частот в 1-м сигнале оптимальной системы, в втором регистре числовая последовательность, соответствующая второму сигналу и т.д. Например, если исходная кодовая последовательность, записанная в регистре 23, имеет (для ) вид 243 5 1, то в регистрах 29 с 1-го по 4-й соответственно будут записаны следующие последовательности: Последовательности вида (2) соответству:от сигналам оптимальной системы. Кроме этого, сигнал с выхода триггера 14 управления поступает на

12 ВХОД триггера 15 управлет1я, кото.рый переводится в нулевое состояние и снимает сигнал с одного из входов элемента И 16, что блокирует поступление импульсов в блок 3 формировани крдовых последовательностей, счетчик 4 с М и через линию 5 задержки на тактовый вход распределителя каналов 2А на (М-1)-й канал.

В устройстве предусмотрена возмож ность передачи любого из дискретночастотных сигналов, входящих в оптимальную систему, кодовые последовательности которых после-формирования хранятся в регистрах 29. Для этого на блоке 1 управления должна быть нажата одна из (М-1)-ой кнопок управления (не показана), сигнал с которой подается на один из М-Т входов электронных ключей 17. Появление сигнала на одном из входов приводит к открытию соответствуимцего электронного ключа, сигнал с выхода которого поступает на один из М-1 входов блока 34 опроса блока 8 опроса буферных регистров, кроме этого сигнал с выхода электронных ключей 17 подается на один из входов элемента ИЛИ 18 блока 1 управления, что приводит к срабатыванию триггера 13 управления, сигнал с прямого выхода которого подается на запуск генератора 9 сетки частот и на запись в первый разряд (многотактового кольцевого) регистра 33 единицы. Регистр 33 по приходу тактовых импульсов осуществляет перепись единицы в очередной свой разряд, что приводит при наличии на одном из М-1 входов блока 34 опроса сигнала к открытию такого элемента И, один из входов которого соединен с выходом этого очередного разряда. Сигнатпз с выхода блока 34 опроса подаются в блок 7 буферных регистров ив соответствии с выбранным режимом работы производят последовательное

считывание с тактовой частотой содержимое ячеек определенного регистра 29. Это содержимое ячеек в параллельном коде через элементы И 30, ИЛИ 31 и ИЛИ 32 подается на входы цифрового коммутатора 10, на остальные входы которого подаются все сигналы сетки частот, которые вырабатывает генератор 9 сетки частот. Цифровой коммутатор 10 ставит в соответствие каждому числу заранее определенный сигнал сетки частот с частотой

(1й,)лб1)

Для получения фазы выходного сигнала в моменты переключений беэ скачков сетка частот формируется от такой опорной частоты , которая синхронизирует работу блока В опроса буферных регистров. С выхода цифрового коммутатора 10 сформированный дискретно-частотный сигнал поступает в усилитель 11 мощности, где усиливается и далее подается для излучения на антенну.

Введение новых элементов - блока управления, блока формирования кодовых последовательностей, счетчика с , блока буферных регистров, блока опроса буферных регистров, двух линий задержки с одинаковым временем задержки и усилителя 11 мощности позволяет вследствие обеспечения возможности формирования многочастотных сигналов, имеющих минимальное значение максимального выброса взаимнокорреляционных функций повысить помехозащищенность устройства, а также появляется возможность использовать предлагаемое устройство для надежной работы с несколькими абонентами. При зтом число абонентов, с которыми может быть установлена устойчивая связь, равно М-1.

К элементу 35

Н индикатору

i/

R

/4

Л /Я

V

К блокам

От элемента 28

фиг. 2

От блока Z

/

К. блоку 7

V

N /

А/тffА/ /t

вхедл/ установки кода.

м

м-Г

&

&

&

с

У7/7 /

L

От 5лока 1

(Риг.3

I

L

/

r-i- 32

l-n

H

м

/4

/77 элег ентов Фиг.

f7

Kf/itKy i

tf

W-/

26

0m элемемтоё

К блоку 7

y-t

&

fi

Т

:

Н-1

/ffmMeMfnra17

От блвка 1

4f

i

М

0т блока 2

Фиг.5

Фиг 6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для передачи многочастотных сигналов без разрыва фазы | 1975 |

|

SU559443A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Тузов Г.И | |||

| Статистическая теория приема сложных сигналов | |||

| М., Советское радио, 1977, с.66,-69 (прототип). | |||

Авторы

Даты

1984-08-07—Публикация

1983-05-20—Подача