1

Изобретение относится к области автоматического контроля работоспособности электронных устройств, в частности оно может использоваться для поиска отказов в устройствах с релейными сигналами неисправностей.

Известно устройство, содержащее генератор тактовых импульсов, регистр сдвига, реле времени, логические схемы и электронный коммутатор, содержащий счетчик, шифратор, ключи и схему «ИЛИ, и позволяющее при наличии сигнала неисправности осуществлять последовательно во времени поиск неисправного блока путем поочередного опроса состояний датчиков - сигнализаторов неисправностей контролируемых блоков объекта контроля с фиксацией кода адреса неисправности.

Недостатки устройства заключаются в малом его быстродействии, зависимости времени отыскания неисправного блока от его порядкового номера среди контролируемых блоков, отсутствии информации о кратковременных отказах, то есть сбоях, недостаточной разрешающей способности по отношению к кратковременным отказам, продолжительность которых меньше времени, необходимого коммутатору устройства на отыскание источника этого сбоя.

Цель изобретения заключается в повышении быстродействия и расширении функциональных возможностей устройства.

Поставленная цель достигается тем, что устройство содержит триггеры, нулевыми входами соответственно подключенные к выходам электронных ключей, вторые входы которых подключены к выходу реле времени; элементы временной задержки, выходами соответственно подключенные к единичным входам триггеров; двухвходовые схемы «ИЛИ, последовательно соединенные между собой так, что выход предыдущей схемы «ИЛИ подключен к первому входу последующей, схемы «Запрет, прямыми входами соответственно подключенные к нулевым выходам триггеров, исключая первый триггер, и ко вторым входам двухвходовых схем формирователь, входом подключенный к выходу многовходовой схемы «ИЛИ, а выходом - ко входу реле времени.

Устройство также содержит шифратор адреса, выходами подключенный ко вторым поразрядным входам регистра сдвига, одним из входов - непосредственно к нулевому выходу первого триггера, к запрещающему входу первой схемы «Запрет и к первому входу первой двухвходовой схемы другими входами - к входам элементов задержки и выходам схем «Запрет, запрещающие входы которых, кроме первой схемы, подключены к выходам двухвходовых схем «ИЛИ.

Таким образом, положительный эффект достигается введением элементов памяти, логических элементоь и функциональной связи между ними, позволяющей сократить время цикла до величины, необходимой для онроса состояний датчиков-сигнализаторов неисправностей и кодирования адресов только отказавших блоков объекта контроля, а следовательно, повысить быстродействие, а также и фиксировать отказы любой длительности.

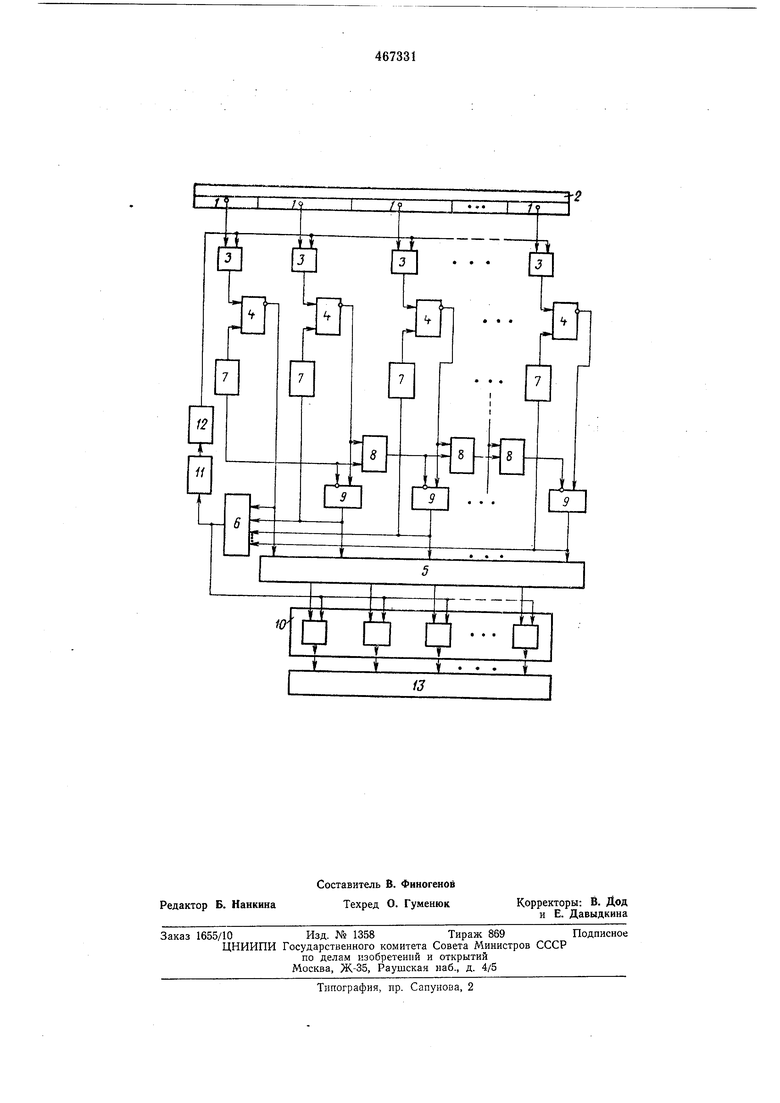

На чертеже изображена схема предлагаемого устройства для автоматического поиска неисцравностей.

Выходные шины 1 датчиков релейных сигналов неисправностей блоков объекта контроля 2 подключены к первым входам электронных ключей 3, выходами соответственно подключенных к нулевым входам триггеров 4.

Триггеры 4 как элементы двоичной памяти используются для фиксации моментов возникновения сигналов неисправностей от соответствующих датчиков.

Нулевые выходы триггеров 4, кроме первого, нулевым выходом подключенного к первому входу шифратора адреса 5, к одному из входов схемы «ИЛИ 6 и через элемент 7 временной задержки к своему единичному входу, соответственно подсоединяются ко вторым входам двухвходовых схем «ИЛИ 8 и к прямым входам схем «Запрет 9, выходы которых подключены к соответствующим входам шифратора 5, схемы «ИЛИ 6 и через элементы 7 временных задержек - к единичным входам соответствующих триггеров 4.

Шифратор 5 предназначен для представления кодом адресов блоков, датчики которых генерируют сигналы неисправностей.

Схема «ИЛИ 6 служит для выработки интегрального сигнала неисправности.

Элементы 7 необходимы для формирования кодирующих импульсов определенной длительности, а также для возвращения соответствующих триггеров 4 в исходное состояние.

Логические двухвходовые схемы «ИЛИ 8, схемы «Запрет 9 используются как элементы функциональной связи между цепями фиксации отказов, каждая из которых состоит из электронного ключа 3, триггера 4, элемента 7 временной задержки и схемы «Запрет 9, за исключением первой цепи, в которой элемент «Запрет отсутствует.

Двухвходовые схемы «ИЛИ 8 последовательно соединены между собой так, что выход предыдущей схемы «ИЛИ 8 соединен со вторым входом последующей, причем выходы всех схем «ИЛИ 8 соответственно подключены к запрещающим входам схем «Запрет 9.

Первые поразрядные входы регистра сдвига 10 соединены с выходом схемы «ИЛИ 6, а также через формирователь 11 - со входом схемы реле времени 12, выходом подсоединенной ко вторым входам ключей 3, а вторые входы регистра 10 соответственно подключены к выходам шифратора 5.

Формирователь 11 предназначается для формирования импульса от заднего фронта

суммарного импульса, равного или кратного длительности кодирующего импульса.

Выходы регистра сдвига 10 соответственно соединяются со входами блока индикации 13. Блок индикации 13 используется в целях как индицирования результатов поиска, а также для классификации отказов на устойчивые и неустойчивые, определения и выдачи частости их появления.

Устройство работает следующим образом.

При отсутствии сигналов неисправностей триггеры 4 находятся в нулевом состоянии, а электронные ключи 3 и схемы «Запрет 9 открыты.

При отказе одного, двух и более блоков объекта контроля 2, например блоков с порядковыми номерами i, t-f 3, J-t-8, соответствующие им сигналы релейного типа по выходным шинам 1 от датчиков через электронные

ключи 3 подаются на нулевые входы соответствующих триггеров 4. Как видно из чертел а, наличие функциональной связи между элементами цепей фиксации сигналов неисправностей приведет к тому, что элементы «Запрет 9 последующих цепей после цепи, в которой зафиксирован сигнал неисправности от t-ro блока с наименьшим порядковым номером среди отказавших, закрываются за счет подачи потенциала на запрещающие входы

их через схемы «ИЛИ 8 с выходов триггеров 4, перешедших в единичное состояние.

Тем самым обеспечивается возможность подачи только на один вход шифратора адреса

5 кодирующего потенциала, длительность которого определяется параметрами элемента задержки 7. Кроме того, сигнал со схемы «ИЛИ 6 подается на первые входы регистра сдвига 10, разрешая запись кода адреса неисправности 1-го блока. С выхода регистра сдвига 10 код адреса неисправного г-го блока подается в блок индикации 13 для индицирования результата поиска, для записи в память блока индикации для последующей классификации отказов на устойчивые и неустойчивые и определение частости их появления.

После истечения определенного времени триггер 4 t-той цепи возвращается в исходное нулевое состояние, тем самым снимается воздействие с запрещающих входов схем «Запрет 9 последующих цепей, начиная с t-той по (г-|-3)-ю цепь включительно, и создает ;я возможность определения адреса следующего неисправного блока, номер которого стал наименьшим среди неопрошенных, то есть (г+3)-го блока.

Единичный потенциал с выхода триггера 4 (-|-3)-й цепи подается через схему «Запрет

9 той же цепи на соответствующий вход шифратора 5. Через время, равное длительности кодирования, триггер 4 (1+3)-й цепи .импульсом с выхода схемы «Запрет 9 через элемент 7 временной задержки возвращается в исходное состояние.

Далее процесс кодирования и фиксации кода адреса неисправных (гЧ-З)-х и (t+8)-x блоков аналогичен вышеописанному.

По окончании цикла определения адресов неисправных блоков, то есть переключения триггера (i+8) -и цепи в нулевое состояние и при условии, что все остальные триггеры также находятся в исходном состоянии, формирователь 11 импульсом запускает реле времени 12, которое кратковременно закрывает электронные ключи 3 всех цепей фиксации отказов. По истечении времени возбужденного состояния реле ключи открываются и триггеры 4 соответствующих цепей вновь зафиксируют наличие сигналов неисправности, тем самым начинается очередной цикл определения адресности отказавших блоков.

Предмет изобретения

Устройство для автоматического поиска неисправностей, содер:жащее электронные ключи, первыми входами соединенные с датчиками, многовходовую схему «ИЛИ, выходом соединенную с первыми поразрядными входами

регистра сдвига, и реле времени, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит триггеры, нулевыми входами подключенные к выходам 5 электронных ключей, вторые входы которых подключены к выходу реле времени, элементы временной задержки, выходами подключенные к единичным входам триггеров, последовательно соединенные двухвходовые схемы

0 «ИЛИ, схемы «Запрет, сигнальными входами подключенные к нулевым выходам триггеров и ко вторым входам двухвходовых схем «ИЛИ, формирователь, входом подключенный к выходу многовходовой схемы «ИЛИ,

5 а выходом - ко входу реле времени, и шифратор адреса, выходы которого подключены ко вторым поразрядным входам регистра сдвига, один из входов - к нулевому выходу первого триггера, к запрещающему входу перО вой схемы «Запрет и к первому входу двухвходовой схемы «ИЛИ, другие входы - к соответствующим входам элементов задержки и выходам схем «Запрет, запрещающие входы которых подключены к выходам двухвхо5 довых схем «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска неисправностей | 1982 |

|

SU1059550A1 |

| Устройство для контроля электрических цепей | 1985 |

|

SU1270729A1 |

| Устройство для ввода информации | 1983 |

|

SU1151945A1 |

| Устройство для диагностики систем управления | 1978 |

|

SU771620A1 |

| Многоканальное устройство для контроля параметров | 1978 |

|

SU911539A2 |

| Устройство для поиска неисправностей | 1978 |

|

SU744478A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для защиты от изменения заданной скорости вращения электропривода постоянного тока | 1985 |

|

SU1377957A1 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

Авторы

Даты

1975-04-15—Публикация

1972-07-06—Подача