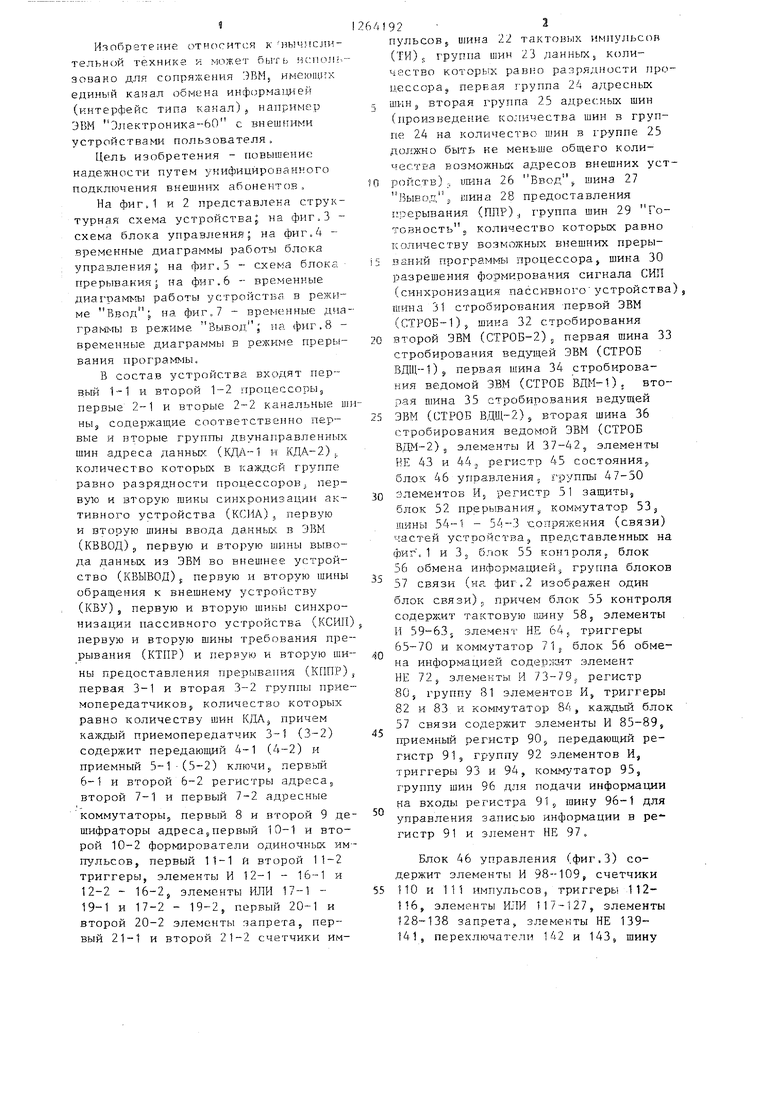

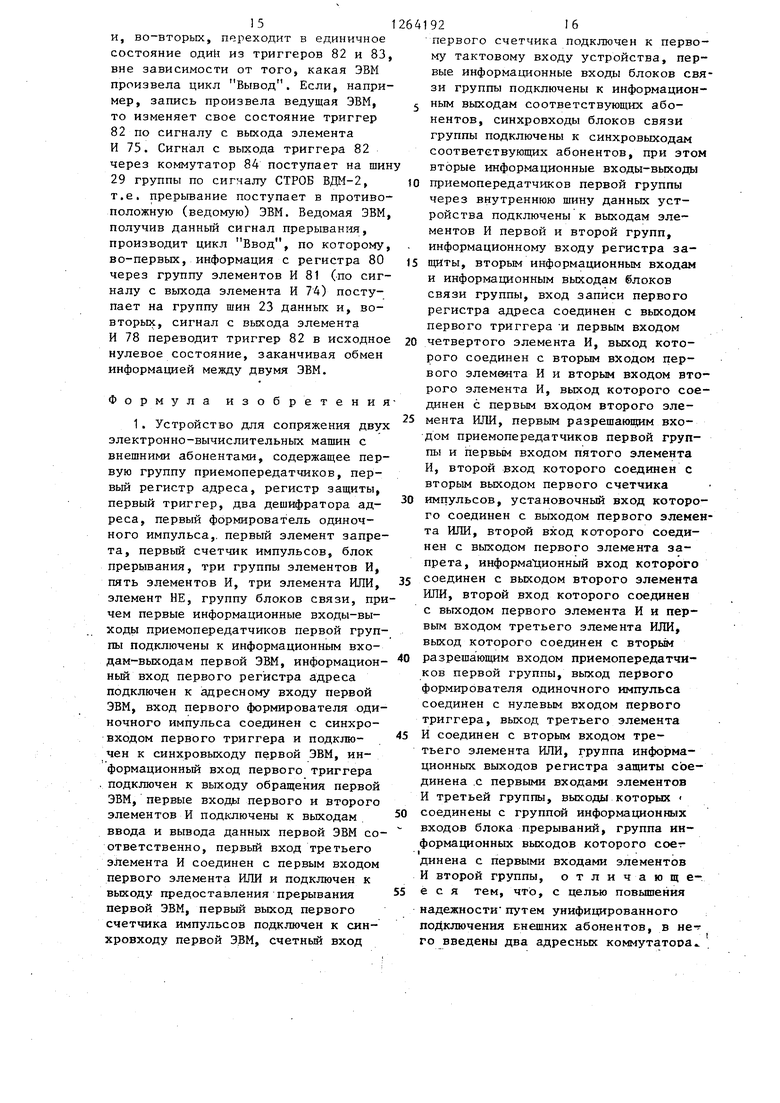

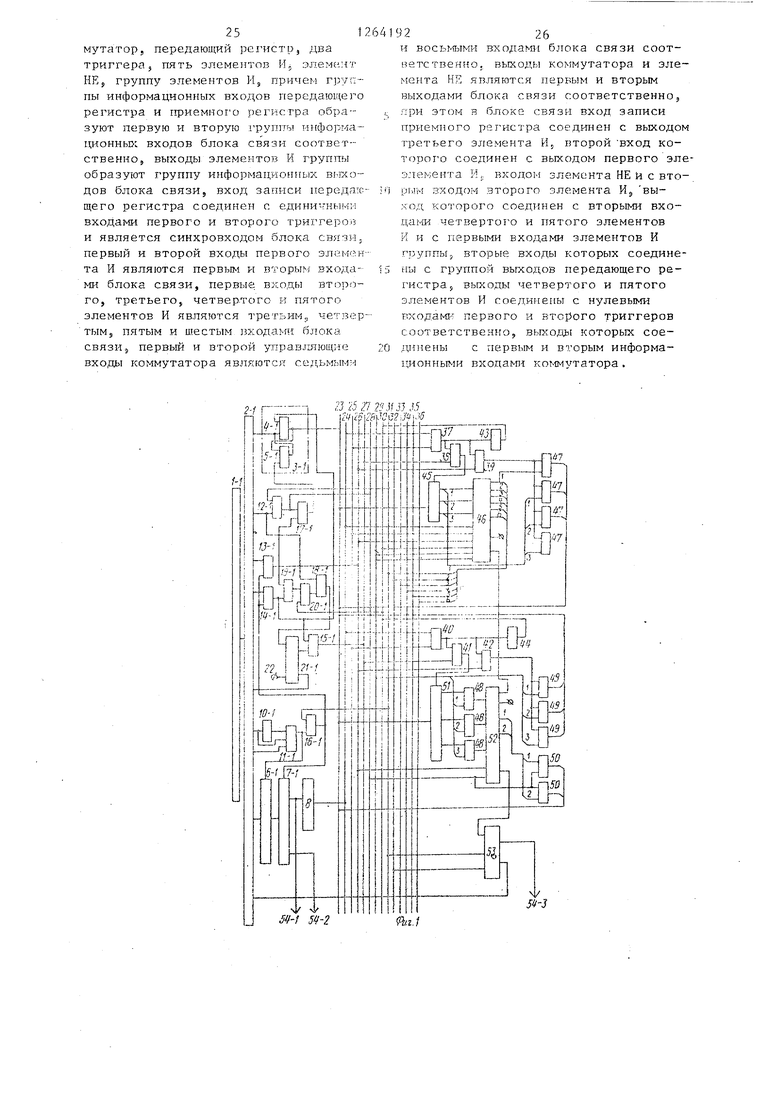

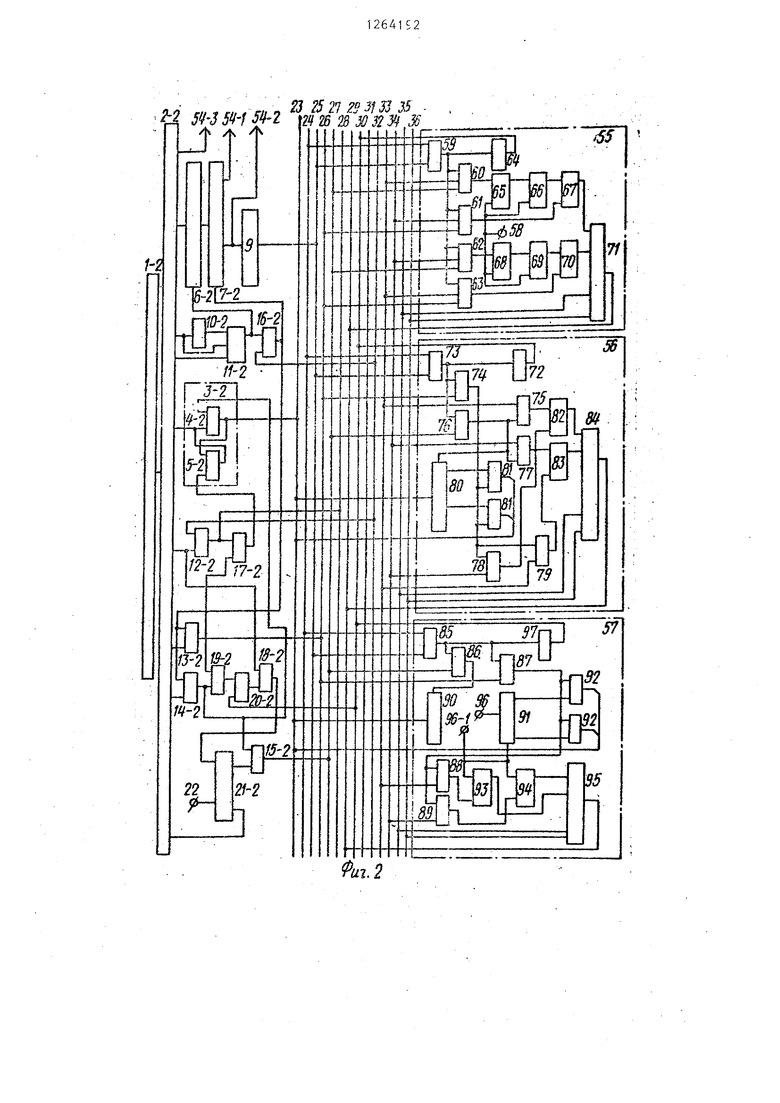

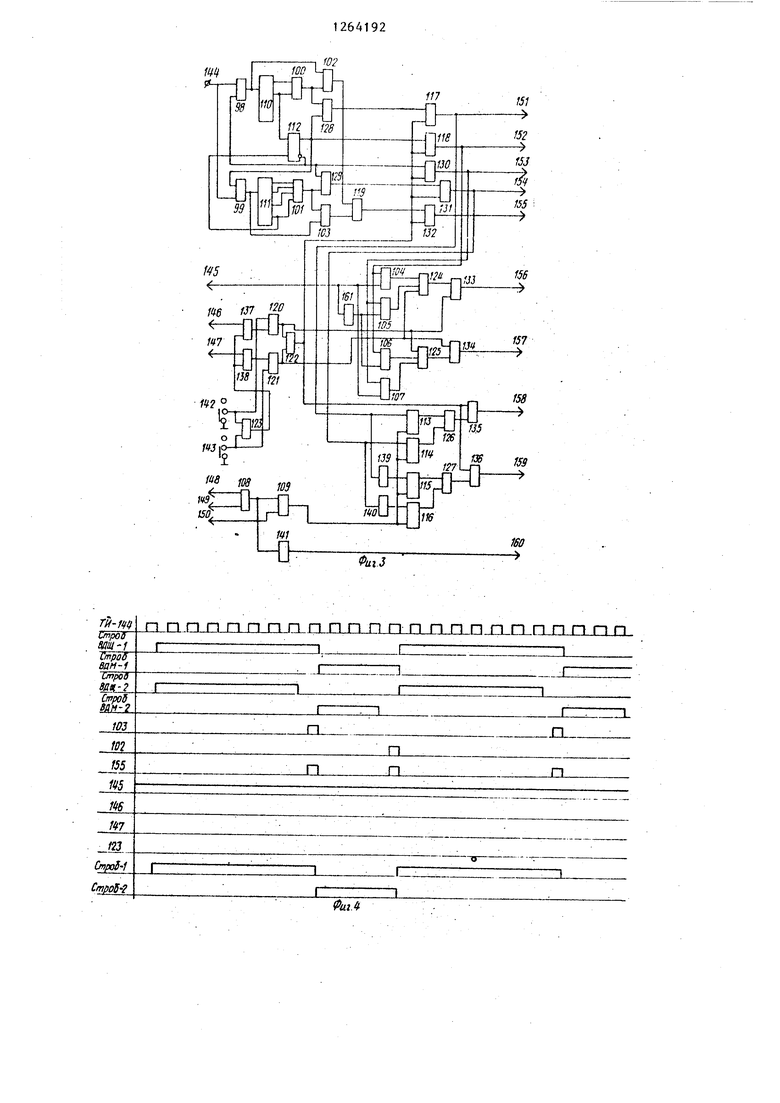

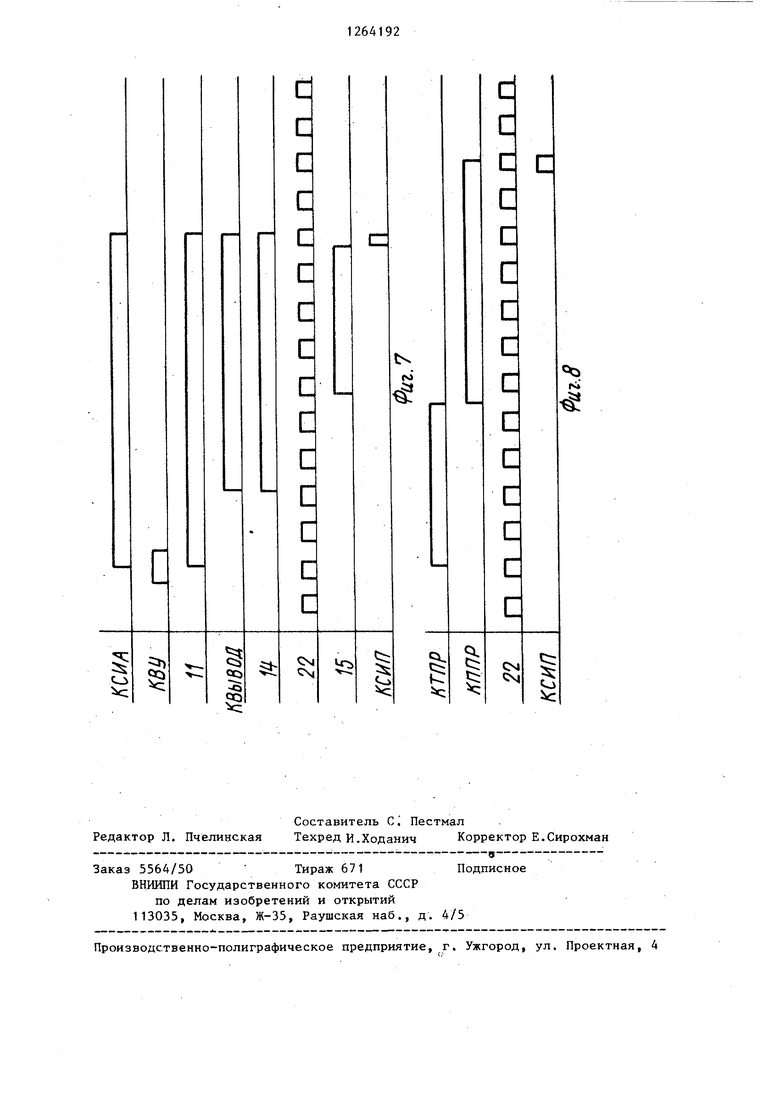

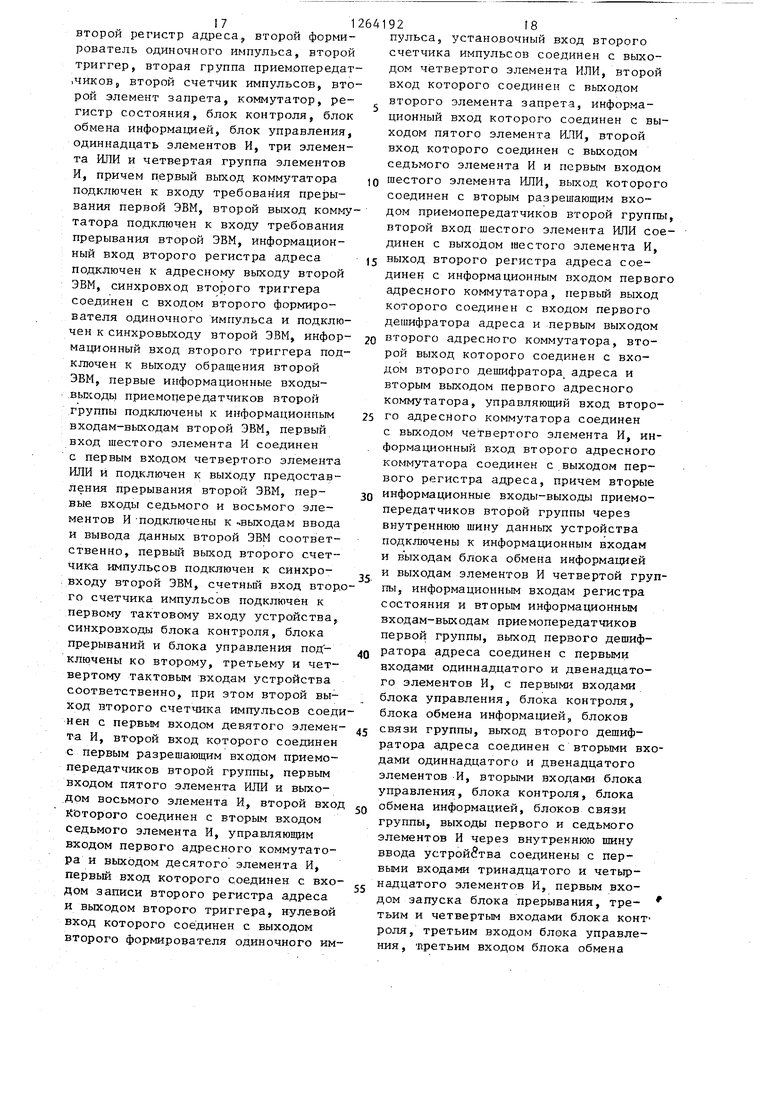

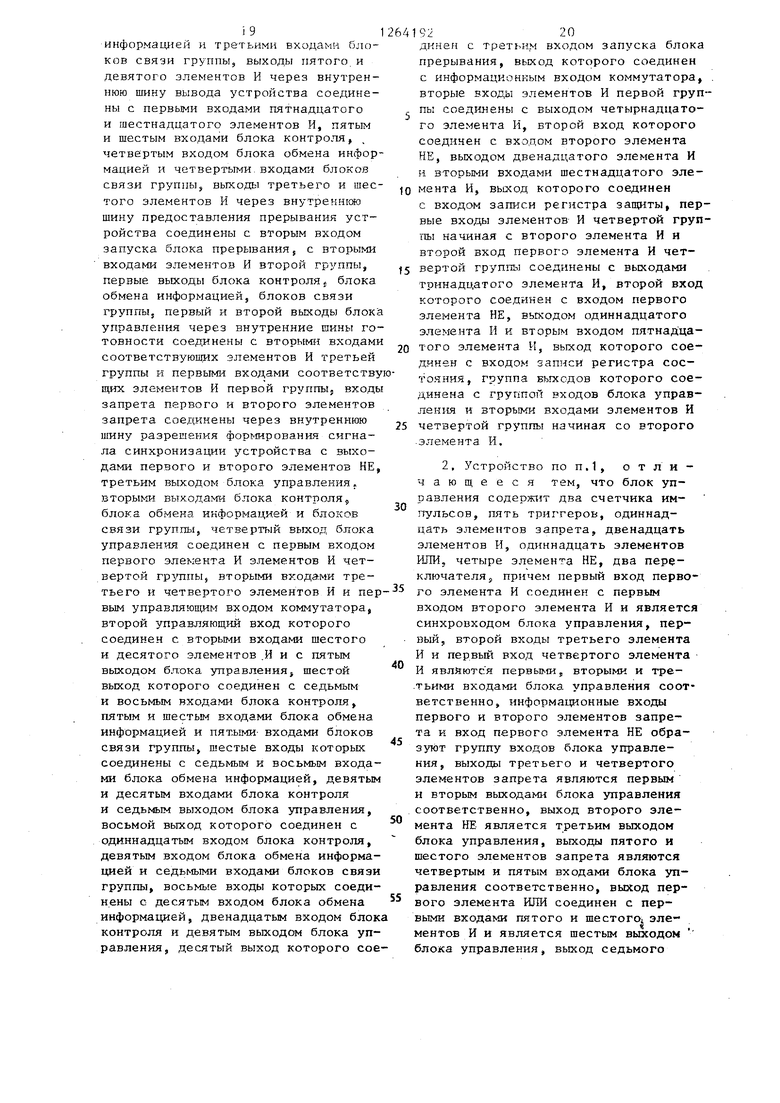

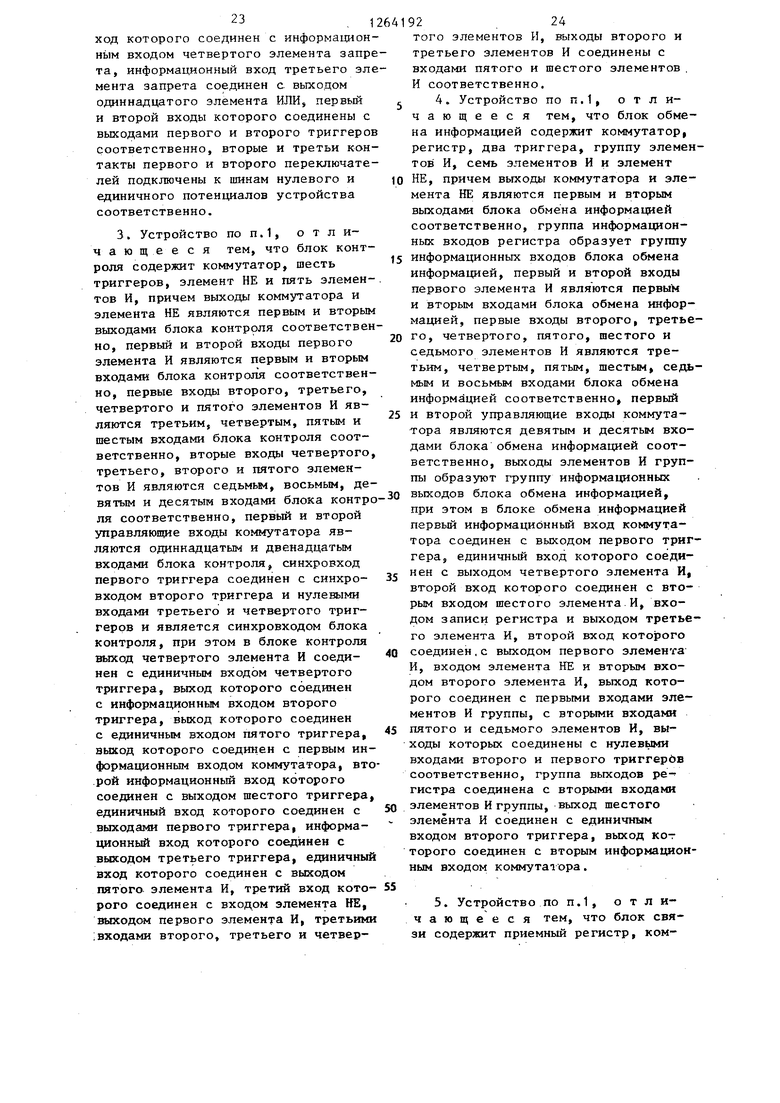

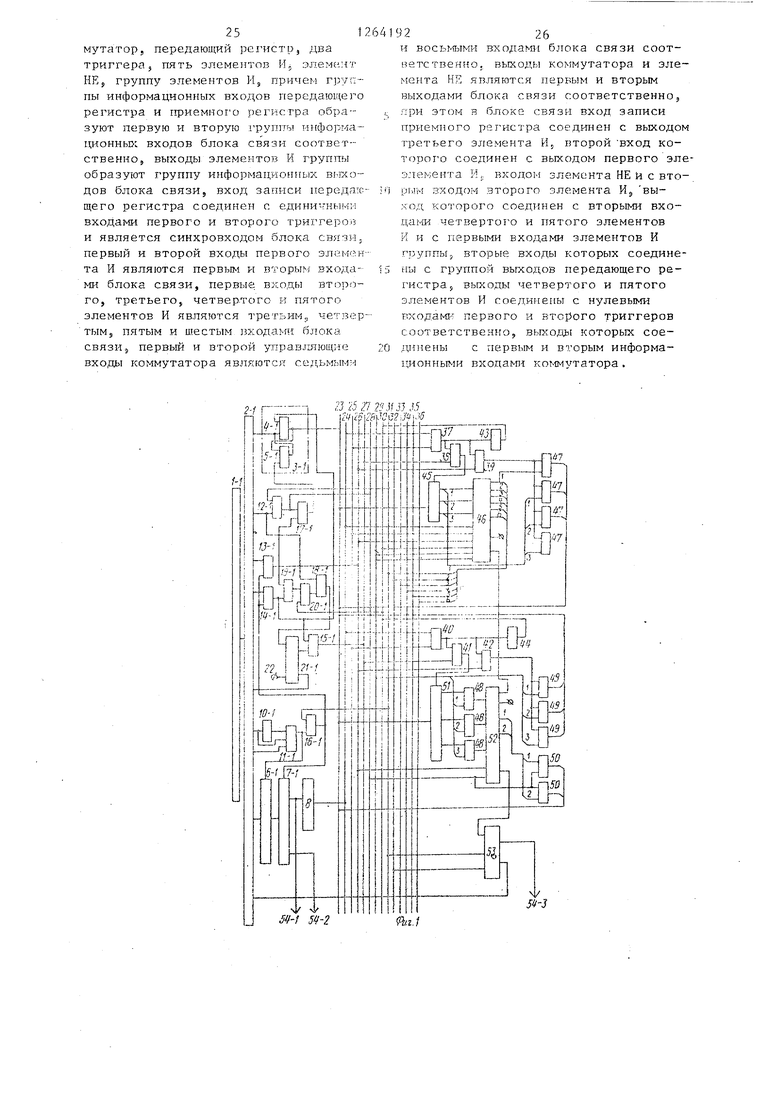

Изобретение отнс)сит1;я к вычислительной технике и может быть исшоль эовано для сопряжения ЭВМ, имеющих единь Й канал обмена инфирма ией (интерфейс типа канал) ,, например ЭВМ Электроника--60 с внешними устройствами пользователя . Цель изобретения - повышение надежности путем унифицированного подключения внешних абонентов. На фиг.1 и 2 представлена струк турная схема устройства; на фиг.З схема блока управ1 ения; на фиг. 4 временные диаграммы работы блока управленияJ на фиг.5 - схема блока прерывания; на фиг, 6 - временные диaгpaм шl работы устройства в режи ме на фиг.7 - временные ди граммы в режиме Вывод яа (|)иг . 8 временные диаграммы в режиме преры вания программы. В состав устройства входят первьгй 1-1 и второй 1-2 процессорЫд первые 2-1 и вторые 2-2 канальные ны содержащие соответстЕ;е)П1о первые и вторые rpynnbi двунаправленных шин адреса данных (КЛА--1 и КДА-2) ,, количество которых в кащсй группе равно разрядности процессоров, первую и вторую шины синхронизации активного устройства (КСИА) первую и вторую шины ввода данных в 2)ВМ (КВВОД)5 первую и вторую шины вывода данных из ЭВМ во внешнее устройство (КВЫВОД) J, первую и вторую шинь обращения к внешнему устройству (КВУ), первую и вторую шикы синхронизации пассивного устройства (КСИП первую и вторую шины требования пре рывания (КТПР) и первую и вторую ши ны предоставления прерывания (КППР первая 3-1 и вторая 3-2 группы при мопередатчиков j количество которых равно количеству шин КДА причем каждый приемопередатчик 3-1 (3-2) содержит передающий А-1 (4-2) и приемный 5-1 -(5-2) ключи,, первый 6-1 и второй 6-2 регистры адресаg второй 7-1 и первый 7-2 адресные коммутаторы, первый 8 и второй 9 де шифраторы адреса5первый 10-1 и второй 10-2 формирователи одиночных им пульсов, первый 11-1 и второй 11-2 триггеры, элементы И 12-1 - 16-1 и 12-2 - 16-2 элементы ИЛИ 17-1 19-1 и 17-2 - 19-25 первый 20-1 и второй 20-2 элементы запрета, первый 21-1 и второй 21-2 счетчики импульсов 5 шина 22 тактовых им11у;изсов (ТИ)5 группа шин 23 данных количество которых равно разрядности проадресныхцессора перкая группа шинэ вторая группа 25 адресных шин (произведение количества шин в группе 24 на количество шин в группе 25 должно быть не меньше общего количества возможньж адресов внешних устишна 26 Ввод „ шина 27 роист в) ;, Вывод,, шина 28 предоставления ;рерывания (ППР) ,, группа шин 29 Готовность, количество которых равно количеству возможных внешних прерываний програм1угь1 процессора, шина 30 разрешения формирования сигнала СИП (синхронизация пассивногоустройства), шина 31 стробирования первой ЭВМ (СТРОБ-), шика 32 стробирования второй ЭВМ (СТРОБ-2) ,. первая шина 33 стробирования ведущей ЭВМ (СТРОБ ВДЩ-) первая шина 34 стробирования ведомой ЭВМ (СТРОБ ВДМ-1), вторая шина 35 стробирования ведущей ЭВМ (СТРОБ ВДЩ-2)5 вторая шина 36 стробирования ведомой ЭВМ (СТРОБ ВДМ-2)5 элементы И 37-42, элементы НЕ 43 и 44 J регистр 45 состояния,, блок 46 управления 5 группьЕ 47-50 элементов Hj регистр 51 защиты, блок 52 прерывания,; коммутатор 535 шины 54-- - 54-3 сопряжения (связи) частей устройства, представленных на фиг. 1 и 3. блок 55 контроля, блок 56обмена информацией, группа блоков 57связи (на фиг,2 изображен один блок связи)р причем блок 55 контроля содержит тактовую пину 58, элементы II 59-63; элемент НЕ 64, триггеры 65-70 и коммутатор 71j блок 56 обмена информацией содерлонт элемент НЕ 72J элементы И регистр 80, группу 81 элементов И, триггеры 82 и 83 и коммутатор 84, каждый блок 57 связи содержит элементы И 85-89, приемный регистр 90 передающий регистр 91, группу 92 элементов И, триггеры 93 и 94, коммутатор 95, группу шин 96 для подачи информации на входы регистра 91, шину 96-1 для управления записью информации в ре гистр 91 и элемент НЕ 97, Блок 46 управления (фиг.З) содержит элементы И 98--109, счетчики 110 и 111 импульсовJ триггеры 112116, элементы ИЛИ 117-127, элементы 128-138 запрета, элементы НЕ 139141, переключатели 142 и 143, шину

144 ТИ, входные шины 145-150, выходные шины 151-160 и элемент НЕ 161.

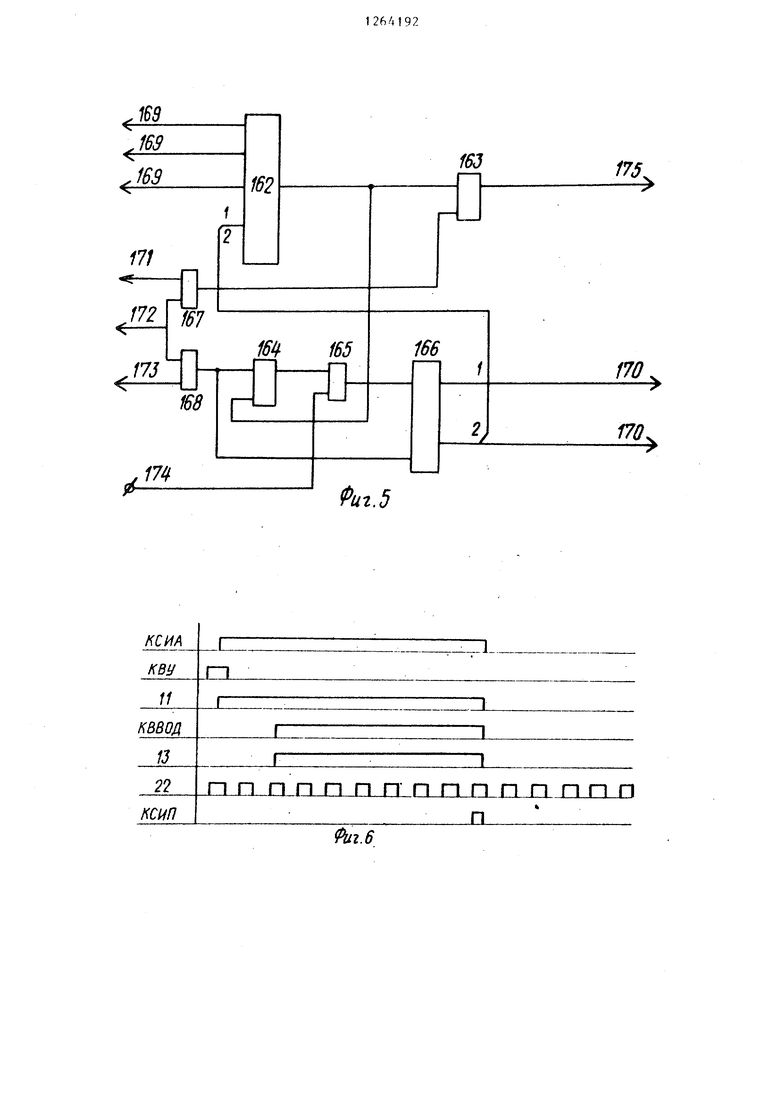

Блок 52 прерывания (фиг.5) содержит коммутатор 162, триггеры 163 и 164, элемент И 165, счетчик 166 импульсов, элементы ИЖ 167 и 168, группу 169 входных шин, группу 170 выходных шин, входные управляющие шины 171-173, тактовую шину 174 и выход11ую шину 175.

Количество адресных дешифраторов 8 и 9 и количество групп адресных шин 24 и 25 может быть больше: увеличение их количества ведет к сокращению общего количества адресных шин 15 во всех группах, но увеличивает количество входов у таких элементов И, как, например, 37,40,59, 73 и 85 Устройство для сопряжения работае следующим образом. Выходы элементов, например коммутаторов 7-1 и 7-2 или групп И 47-50 элементов, элементотз НЕ 43,44, 64, 72 и 92, могут быть объединены в результате того, что в качестве элементов, выходы которых объединяются применяются, например, ключи с откры тым, коллекторным выходом и общей нагрузкой, или специальные шинные усилители с тремя состояниями: 1 О, Обрыв. Количество блоков 57 рграничено только количеством возможных адресов в ЭВМ и нагрузочной способностью передатчиков (выходных усилителей). Для увеличения коэффициента разветвления по выходу передатчиков в качестве входных элементов приемников (регистров 90) можно применить КМОП-ключи, например микросхемы 176ПУЗ, оторые обладают большим входным сопротивлением и одновременно могут выполнять роль входных фильтров, повьш1ая помехоустойчивость обмена информации. Блок 57 может содержать не все элементы изображенные на фиг.2, однако в его составе имеются выполняющие дополнительные функции элементы, которые непосредртйенно не участвуют в пррцессе обмена информацией, например исполнительные механизмы, индикаторы, реле, клавиатура, цифропечатающие устройства и т.д., и поэтому не изображены на фиг.. 2. Количество блоков 56 обмена информацией также может быть больше, чем изображено на фиг.2. В качестве формирователей 10-1 и 10-2

импульсов могут быть использованы любые формирователи, в том числе и дифференцирующие цепи.

В устройстве используется горячее резервирование двух ЭВМ (первой и второй), для чего процессоры 1-1 и 1-2 через канальные шины 2-1 и 2-2 и устройство сопряжения подключены к одним и тем же внешним устройствам.

Каждая из-двух ЭВМ может быть как ведущей, так и ведомой. Это определяется по величине потенциала на шине 145: единичный уровень свидеТельствует о том, что первая ЭВМ ведущая, вторая - ведомая,при нулевом уровне ведущей является вторая ЭВМ, а ведомой - первая. Номер ЭВМ определяется по величине потенциала на первом выходе блока 46 (шина 156), который через первый элемент И 47 из группы может считываться любой ЭВМ. Номер ЭВМ задается конструктивно и не может быть изменен программными средствами (в отличие от потенциала на шине 145). Различие в работе ведущей и ведомой ЭВМ в данном устройстве состоит в следующем: ведущая ЭВМ выпол-. няет все действия по обмену информацией с внешними устройствами, т.е. производит операции Ввод и Вывод ; ведомая ЭВМ только отслеживает все действия ведущей ЭВМ, т.е. она выполняет операции Ввод из внешних устройств, но не может выполнить операцию Вывод во внешнее устройство. Для обмена информацией между двумя ЭВМ, например для того, чтобы ведомая. ЭЪМ отслеживала какую именно информацию и в какое именно внешнее устройство записывает ведущая ЭВМ в цикле Вывод, имеется один (или несколько) блок 56 обмена информацией, в которьй операцию Вывод может производить как ведущая, так и ведомая ЭВМ. Все прерывания программы от внешних устройств поступают.в обе ЭВМ, для чего в каждом блоке 57 имеются два триггера 93 и 94. Для контроля работоспособности первой и второй ЭВМ служит блок 55 онтроля, с помощью которого первая ВМ контролирует работоспособность торой ЭВМ, а вторая - работоспособость первой. Для этого каждая ЭВМ ериодично, не реже определенного

31

кнтервакз производит операции Вывод Б блок 55 контро,Г1Я, Очсугсчл ие опера ;;ии Вывод однсй из 3Bii з тачение определенного нремени вызывает и дозтой ЭВМ П1: ерыпание програь мы Товр она получает информацию о неисправности. Для повышения дссTOBefii-iocTH контроля операции Вь1Бод можно производить после проведения определенных тестовыг;; программ Б ка)и,ой ЭВМэ проверяющих WK работу, а также после получения сигнала прерывания о неисправности I другая для подтверждения этого npo:i;вести обмен информации с неисправной ЭВМ через блок 56 обмена. Получив подтверждение о .неисправности исправная ЭВМ может во-первьж„ через внешнее устройство подать сигяал на соответств поший индикатор для оператора, во-вторых,, если, она была ведомой; перевести неисправную ЭВМ в зедоь Ю;, а сама стать ведуш,еЙ5 в-третьих, отключить неисправную ЭВй от участия 3 обмене информацией с внешниьФ устройствами Третий вариант, до сравнению с вторьс -Ц яв.пяется более предпочтительны -,., поскольку неисправная ЭВМ может мешать работе исправной,

В устройстве предусмотрено в основном для проведения профилактических и наладочных работ ручное отключение любой из ЭВМ от участия з об-мене информадией, Д.л.я этого в составе блока 46 управления имеются переключатели 142 и 143. Для отключения шобой из ЭВМ достаточно перевести соответствующий переключагехсь в единичное состояние.

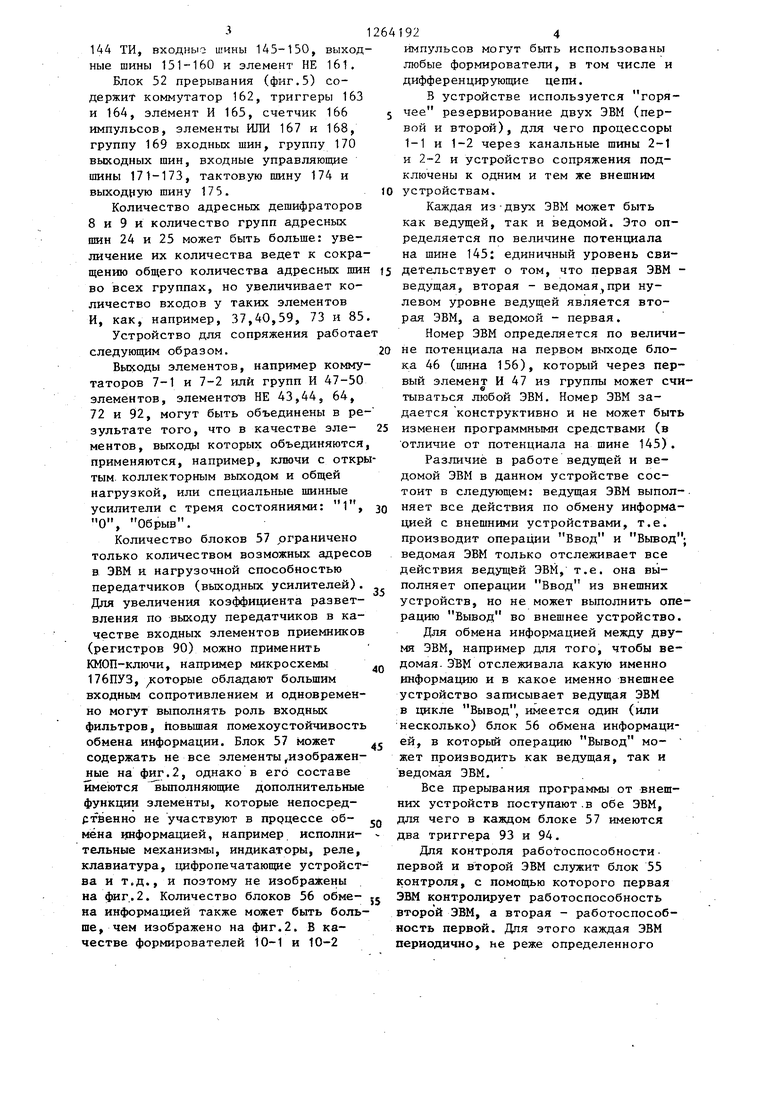

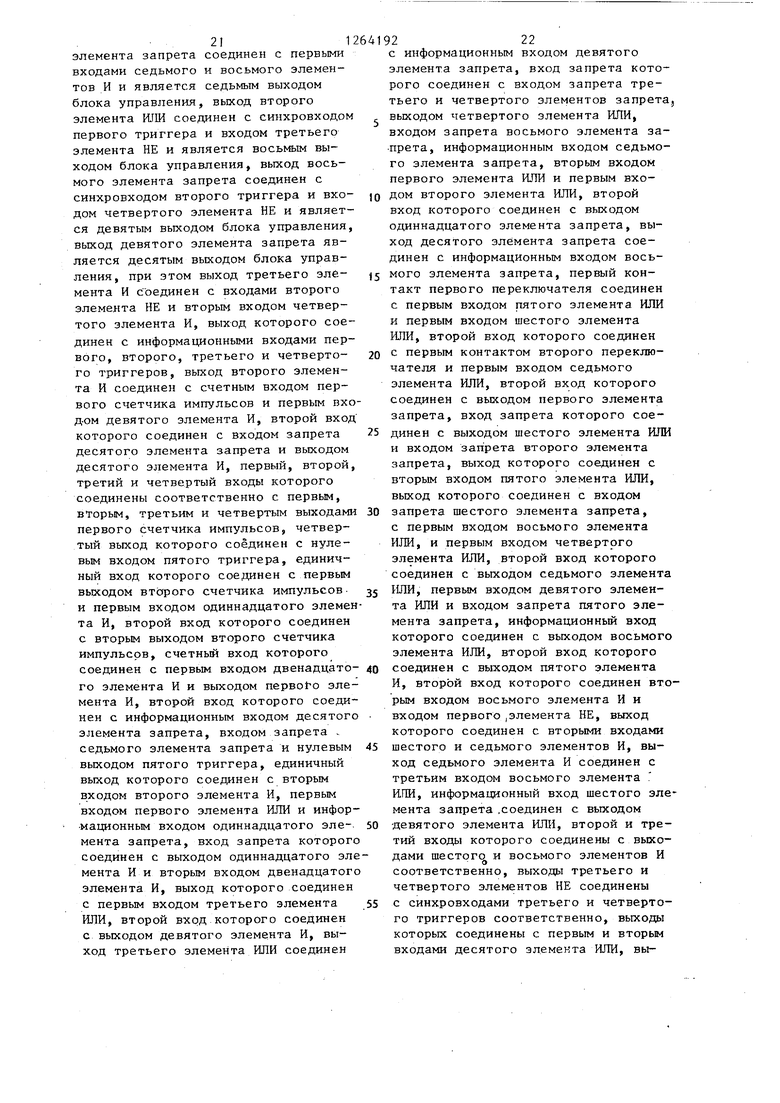

Для обмена информацией с внешними устройстБам; ведуЕ;,ей и ведомой ЭВМ выделяются кванты времени которые (1 ормируются Б блоке 46, Временные диаграммы его работы представлены на фиг.4 В течение интервала времени СТРОБ ВДЩ-1 разрептается обмен информаци с внешншчм устройствами ведущей ЭВМ в течение интервала времени СТРОБ ВДМ-1 -- обмен киформа ции с внешними устройствами ведомой ЭВМ, В течение интервала времени ояределяемого сигналом СТРОБ ВД1Ц-2 разрешаются прерьшания от внешних устройств в ведущую ЭВМ, в течение интервала СТРОБ ВДМ-2 - прерывания от внешних устройств в ведомую ЭВМ. В течение отрезка времени меж,п,у

92

окончанием сигнала СТРОБ ВДЩ-2 и

ijii строи В1Щ-1 ве1аниемдущая ЭВМ ii.ojiXria успеоь ооработать сигнал прерьшанияJ которьй может (оступитъ то-ГНС S i-iOMejir окончания сигнала СТРОЕ ВДЩ-2 (аналогично для ведомой ЭВМ) , С:1гнал СТРОБ-1 опреде.пяет яремЯ; в течение которого разрешен fMihje;- ;::мф:::ркиишей для первой .ISM L. .i;a; Di уст.;ойсгвамИз а поc.i- :;;i;7y СТРОБ--2 с BHetuimi-su устройг.тБак:г может обиен-гааться информа.цлей Аорая ЭВМ. Д.пителькости интер-тлоБ времекк: для ведущей ЭВМ должны tciTb значительно больше чем дли- 1е.пьтшсгк соо петстдуодргн: сигналов , ведомой ЭВМ, Интерзаль зремени должны быть дост.аточнс1 малыми. порядка десятков миллисекунд а В этом слу-; е создается иллзозия работы только одной ведущей ЭВМ (ведомая ЭВМ «фактически нз мешает рэ,боте ведущей

Расскотриь болек. пздробно работу устройсгва Б режима;: - Ввод,; Вывод и прерывания программы. Допустим что первая ЭВМ ;- ведуша.я и все операции происходят Б моменты BpeMeHHj которые находятся внутри сигналов СТРОБ В,ЦЩ-1 и СТРОЯ , т„е, обмен информацг ей происходит между перяой ведущей ЭВМ и 6.поком 57 «

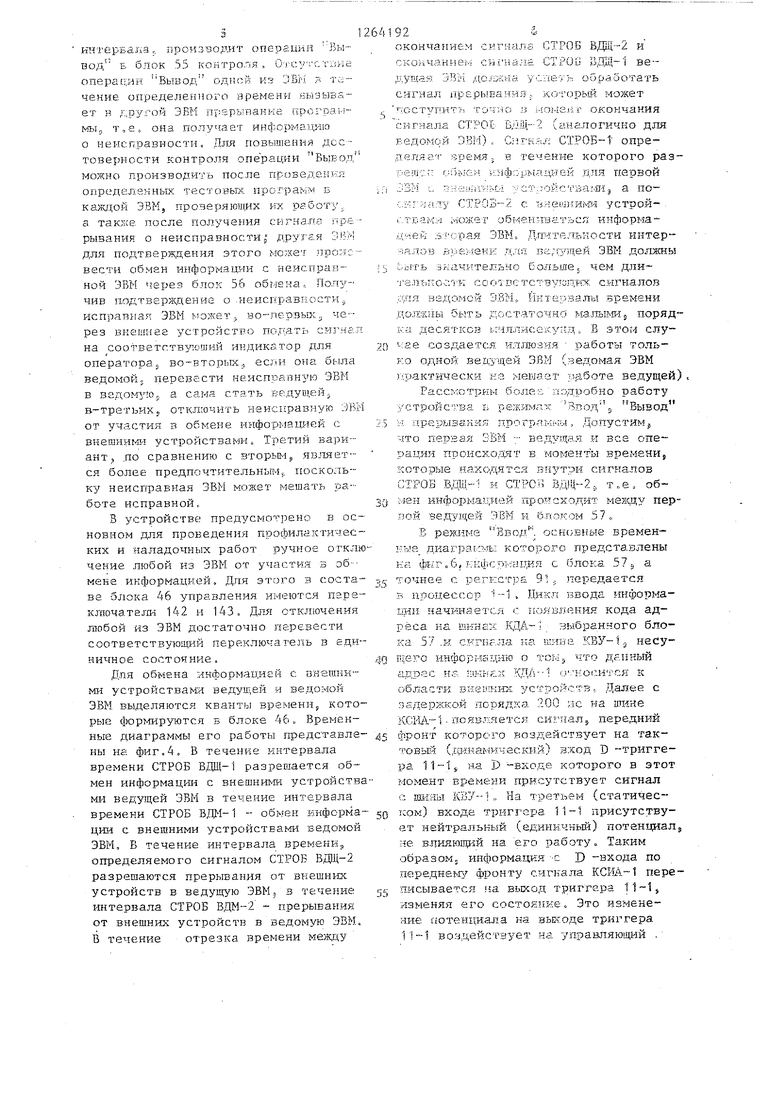

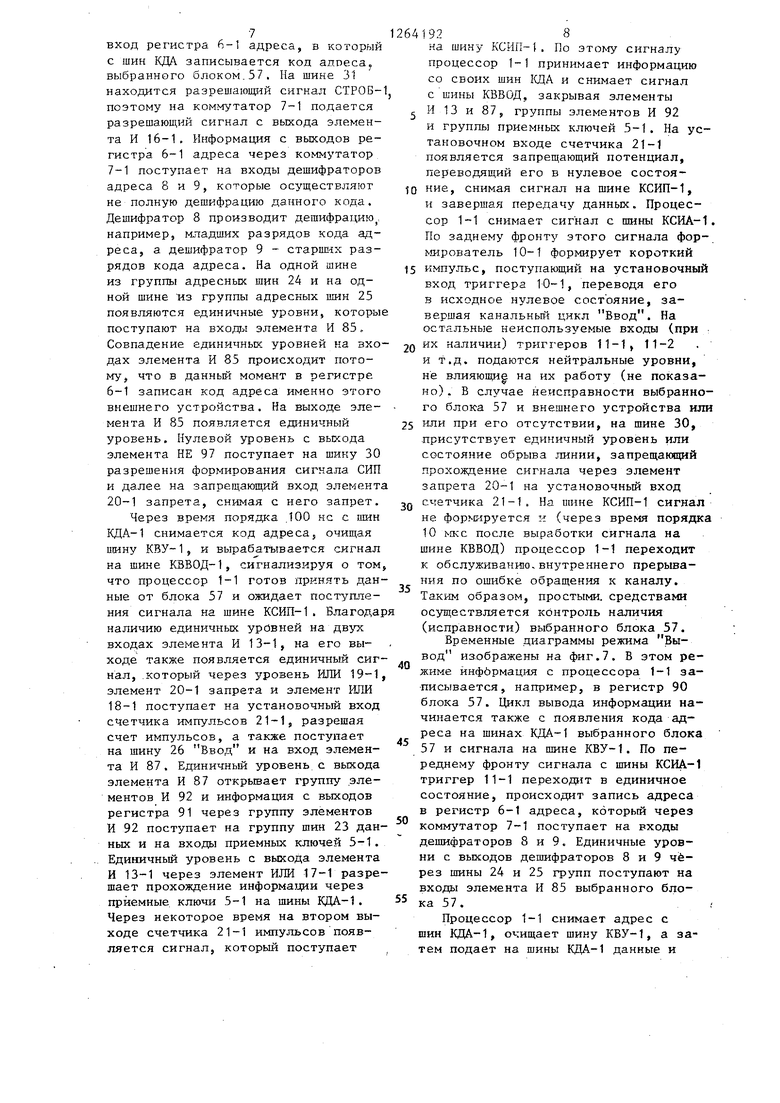

Е режиме Ввод. осн{)вные временKijve диаграл. которого представлены ка фкг .6, кнфсрьяишя с блока 57, а точнее с регистра 91. передается .3 процессор --1, Цик..п ввода информаБни начинаетс.я с noKBJjeHHH кода адреса на шинаа: КДА- выбранного блока 57 ,к скгнр.ла на шине КВУ-1, несуluerc инфорнацию о том, что данный адрес Но. iUKHK.x КДЛ--1 ri/косигся к области внеиших устройств, Далее с задержкой порядка 200 ис на шине КСИА-1 - появляется сил-нал, передний фронт которсго воздействует на так- товьп4 (динамический) вход D -триггера. 11-1s на J) -входе которого в этот момент времени присутствует сигнал с. ншны , На третьем (статическом) входе триггера 11-1 присутствует нейтральный (единичный) потенциал не в. на его работу. Таким образом, информация -с D -входа по переднем:, фронту сигнала КСИА-1 переП41с,ывается га выход триггера 11-Ц изменяя его еостояние. Это изменение потенциала на аькоде триггера 11-1 воз.цей.ствует на управляющий . 7 вход регистра 6-1 адреса, в который с шин КДА записывается код адреса, выбранного блоком.57, На шине 31 находится разрешающий сигнал СТРОБпоэтому на коммутатор 7-1 подается разрешающий сигнал с выхода элемента И 16-1. Информация с выходов регистра 6-1 адреса через коммутатор 7-1 поступает на входы дешифраторов адреса 8 и 9, которые осуществляют не полную дешифрацию данного кода. Дешифратор 8 производит дешифрацию, например, младших разрядов кода адреса, а дешифратор 9 - старших разрядов кода адреса. На одной шине из группы адресных шин 24 и на одной шине из группы адресных шин 25 появляются единичные уровни, которы поступают на входы элемента И 85. Совпадение единичных уровней на вхо дах элемента И 85 происходит потому, что в данньм момент в регистре 6-1 записан код адреса именно этого внешнего устройства. На выходе элемента И 85 появляется единичный уровень. Нулевой уровень с выхода элемента НЕ 97 поступает на шину 30 разрешения формирования сигнала СИП и далее на запрещающий вход элемент 20-1 запрета, снимая с него запрет. Через время порядка .100 не с шин КДА-1 снимается код адреса, очищая иину КВУ-1, и вырабатывается сигнал на шине КВВОД-1, сигнализируя о том что процессор 1-1 готов принять дан ные от блока 57 и ожидает поступления сигнала на шине КСИП-1. Благодар наличию единичных уровней на двух входах элемента И 13-1, на его выходе также появляется единичный сигнал, .который через уровень ИЛИ 19-1 элемент 20-1 запрета и элемент ШМ 18-1 поступает на установочный вход счетчика импульсов 21-1, разрешая счет импульсов, а также поступает на шину 26 Ввод и на вход элемента И 87 . Единичный уровень с выхода элемента И 87 открьшает группу элементов И 92 и информация с выходов регистра 91 через группу элементов И 92 поступает на группу шин 23 данных и на входы приемных ключей 5-1. Единичный уровень с выхоДа элемента И 13-1 через элемент ИЛИ 17-1 разрешает прохождение информации через приемные ключи 5-1 на шины КДА-1. Через некоторое время на втором выходе счетчика 21-1 импульсов появляется сигнал, который поступает 192 на шину КСИП-|. По этоьгу сигналу процессор 1-1 принимает информацию со своих шин КДА и снимает сигнал с шины КВВОД, закрывая элементы И 13 и 87, группы элементов И 92 и группы приемных ключей 5-1. На установочном входе счетчика 21-1 появляется запрещающий потенциал, переводящий его в нулевое состояние, снимая сигнал на шине КСИП-1, и завершая передачу данных. Процессор 1-1 снимает сигнал с шины КСИА-1. По заднему фронту этого сигнала формирователь 10-1 формирует короткий импульс, поступающий на установочный вход триггера 10-1, переводя его в исходное нулевое состояние, завершая канальный цикл Ввод. На остальные неиспользуемые входы (при : их наличии) триггеров 11-1, 11-2 и т.д. подаются нейтральные уровни, не влияющи на их работу (не показано). В случае неисправности выбранного блока 57 и внешнего устройства или или при его отсутствии, на шине 30, присутствует единичный уровень или состояние обрыва линии, запрещающий прохождение сигнала через элемент запрета 20-1 на установочный вход счетчика 21-1, На шине КСИП-1 сигнал не фop иpyeтcя и (через время порядка 10 МКС после выработки сигнала на шине КВВОД) процессор 1-1 переходит к обслуживанию,внутреннего прерывания по ошибке обращения к каналу. Таким образом, простыми, средствами осуществляется контроль наличия (исправности) выбранного блока 57. Временные диаграммы режима Вывод изображены на фиг.7. В этом режиме информация с процессора 1-1 записывается, например, в регистр 90 блока 57. Цикл вывода информации начинается также с появления кода адреса на шинах КДА-1 выбранного блока 57 и сигнала на шине КВУ-1. По переднему фронту сигнала с шины КСИА-1 триггер 11-1 переходит в единичное состояние, происходит запись адреса в регистр 6-1 адреса, который через коммутатор 7-1 поступает на входы дешифраторов 8 и 9. Единичные уровни с выходов дешифраторов 8 и 9 через шины 24 и 25 групп поступают на входы элемента И 85 выбранного блока 5 7 .; Процессор 1-1 снимает адрес с шин КДА-1, очищает шину КВУ-1, а затем подает на шины КДА-1 данные и

9

(,с задержкой, порядка 100 не) вырабатывает сигнал на шине КВЫВОД, который через элемент И 14-1 элемент ИЛИ 19-1, элемент запрета 20-1 и элемент ИЛИ 18-1 поступает на установочный вход счетчика 21-1, разрешая счет импульсов. Одновременно этот сигнал с выхода элемента И 14поступает на входы передающих ключе 4-1 разрешая прохождение информации с шин КДА-1 через группу ключей 4-1 на группу шин 23 данных. Через определенное время, регулируемое коэффициентом пересчета счетчика 21-1, на его первом выходе появляется единичный уровень, который через элемент И 15-1 поступает на шину 27 Вывод и далее на вход элемента И &6, К этому моменту времени на группе шин 23 данных должны закончиться все переходные процессы и переключиться КМОП-ключи (при их наличии) на входах регистра 90, которые, имея более низкое быстродействие, чём основные элементы, и большое входное сопротивление, допускают значительное удаление блоков 57 без применения специального согласования (специальных кабелей) , а также значительно увеличивают допустимое их количество. При достаточном удалении внешних устройств, КМОП-ключи необходимо включать и на входах приемных ключей 5-1 для увеличения помехозащиценности передачи данных.

Изменение потенциала на выходе элемента И 86 разрешает запись инфомации с шин 23 данных в регистр 90. Через определенное время появляется сигнал на втором выходе счетчика 21-1, поступающий на шину КСИП-1. Процессор 1-1, получиб этот сигнал, очищает шину КВЬЮОД-1, снимая сигна на шине КСИП-1, и затем снимает информацию с шин КДА-1 и очищает шину КСИА-1. Формирователь 10-1 переводит триггер 11-1 в исходное нулевое состояние. На этом заканчивается цикл Вывод. Контроль наличия (исправности) блока 57 происходит аналогично описанному.

Устройство в режиме прерывания програь 1ы работает сдедующим образом.

Блоки 57, способные вызвать прерывание программы процессоров 1-1, и 1-2, имеют триггеры 93 и 94. Пере

6419210

ход их в активное (единичное) состояние происходит одновременно с записью информации в регистр 91 по сигналу с шины 96-1. Потенциалы с выхо5 дов триггеров 93 и 94 поступают на входы коммутатора 95, имеющего один выход. Переключение коммутатх ра 95 происходит по сигналам с пшн 35 и 36 которые поступают на его управляющие

10 входы. Разрешающий потенциал присутствует на шине 35, поэтому сигнал с выхода триггера 93 проходит через коммутатор 95 на одну из шин 29 группы. Этот сигнал, несущий информацию

15 о том, что блок 57 готов к передаче данных, поступает на вход одного из элементов И 48 группь и одного из элементов И 49 группы. Сигналы готовности с разных блоков 57 имеют раз20 ный приоритет. Наивысший приоритет у сигнала, поступающего на вход первого элемента И 48 из группы, далее сверху вниз, приоритетность убывает. Регистр 51 запргты служит для разре25 шения или запрета прохождения сигналов прерывания от тех или иных блоков 57. Для реализации этой функции в регистр 51 защиты в цикле Вывод записывается код защиты, который,

0 поступая на другие входы группы элементов И 48, разрешает или запрещает прохождение сигналов с триггеров 93 и 94 на входы блока 52 прерывания. При запрете прохождения сигналов че5 рез группу элементов И 48 процессор 1-1 может считывать состояние шин 29 в цикле Ввод через группу элементов И 49. Для этого выбирается необходимый а,дрес, по которому сра0 батывает элемент И 40, и по сигналу на шине КВВОД сигнал с выхода элемента И 42 разрешает прохождение информации с шин 29 через группу элементов И 49 на группу шин 23 данных

5 и на шины КДА-1. Низкий потенциал на выходе элемента НЕ 44 разрешает формирование сигнала на шине КСИП-1. Если прерывания разрешены, потенциалы с группы шин 29 поступают на

0 группу входов блока 52„

Блок 52 прерывания работает следующим образом.

Инициативные сигналы поступают на входы коммутатора 2, Триггер 164 5 находится в разрешающем состоянии и тактовые импульсы с шины 174 через элемент,И 165 поступают на вход счетчика 166. Код с выхода счетчика n 166 поступает на адресные входы ко мутатора 162, который последовател но переключает шины 169 на вход триггера 163 и вход триггера 164. При появлении инициативного сигнал на одном из входов коммутатора 162 этот си.гнал в момент равенства код счетчика 166 номеру этого входа появляется на его выходе и переводит триггер 164 в запрещающее сост ние, а триггер 163 - в единичное с тояние, которое поступает на вэодд коммутатора 53 и на шину КТПР-/г Пр цесс обработки сигнала -прерывания происходит аналогично описанному, однако триггер 164 и счетчик 166 возвращаются в исходные состояния по любому, сигналу на шине 26 Ввод В блоке 52 имеется еще один уста новочный вход, который соединен с выходом блока 46. Сигнал на этом входе формируется поокончанию кван та времени, выделенному каждой ЭВМ для обмена информацией с внешними устройствами. Блок 46 управления (фиг.З) формирует необходимые сигналы для совместной работы двух ЭВМ. С регистра 45 состояния на шины 145-147 блока 46 поступают потенциа лы, которые задают следующие режимы работы: переключение ЭВМ с ведущей на ведомую: отключение ЭВМ от участия в обмене информацией с внешними устройствами. Исходное состояние регистра 45 состояния таково, что первая ЭВМ ведущая, вторая - ведомая и обе под ключены к внешним устройствам. Для этого на шине 145 присутствует потенциал 1, а на шинах 146 и 147 потенциалы О. Переключатели 142 и 1-43 находятся в нулевых положениях. На выходах элементов ИЛИ 120122 находятся нулевые потенциалы и элементы 130-136 запрета открыты, ЕСли-триггер 112 находится в еди ничном состоянии, на элемент И 99 подается разрешение и счетчик 111 ведет счет импульсов. При переключе нии старшего разряда счетчика 111 из единичного состояния в нулевое триггер 112 также переходит в нулевое состояние. На вход элемента И 9 подается разрешение, и счетчик 110 начинает считать. Переход старшего разряда счетчика 110 из единичного состояния в нулевое вызывает новое 9212 переключение триггера 112 в единичное состояние. Таким образом, триггер 112 периодически переключается из единичного состояния в нулевое и обратно. Время нахождения его в единичном состоянии задается коэффициентом пересчета счетчика 111, а время нахождения его в нулевом состоянии коэффициентом пересчета счетчика 110. С прямого выхода триггера 112 через элемент ИЛИ 118 снимается управляющий сигнал СТРОБ ВДЩ-1, а с инверсного выхода триггера 112 через элемент 130 запрета - управляющий сигнал СТРОБ ВДМ-1 (шина 153). Элементы И 100 и 101 срабатывают, если счетчики 110 и 111 находятся в единичных состояниях. Целесообраз- но, чтобы длительность сигнала СТРОБ ВДЩ-1 бьша большей, чем длительность «сигнала СТРОБ ВДМ-1, поэтому у счетчика 111 больше разрядов, чём у счетчика 110. Импульсы с выходов элементов И 100 и 101 пос тупают на запрещакхцие входы элементов 128 и 129 запрета, поэтому на их выходах формируются сигналы с меньшей длительностью, чем на входах. На выходе элемента ИЛИ 117 формируется сигнал СТРОБ ВДЩ-2, а на: выходе элемента 131 запрета сигнал СТРОБ ВДМ-2 (шина 154). Элементы И 102 .и 103 выполняют логическое умножение сигналов с выходов элементов И 100 и 101 и входных сигналов счетчиков 110 и 111, поэтому на их выходах формируются импульсы, длительность которьгх равна длитель- ности- входных импульсов счетчиков 110 и 111. Объединяясь на элементе ИЛИ 119, они через элемент запрета поступают на шину 155 и на управляющий вход блока 52, устанавливая его в исходное состояние перед началом нового кванта времени. Единичный уровень на шине 145 разрешает прохождение сигнала с выхода элемента РШИ 118 через элемент И 104, а также через элемент ИЛИ 124 и элемент 133 Запрета на шину 156. Поэтоу сигнал СТРОБ-1 совпадает с сигнаом СТРОБ ВДЩ-1. Кроме того, сигнал выхода элемента 130 запрета проодит через элемент И 107,а также чеез элемент ИЛИ 125 и элемент 134 i апрета на шину 157. Поэтому сигнал;

СТРОК-2 совпадает с сигналом

СТРОБ вда-1, При и; менении потенциала ка. шине

145изменяются соответственно сигналы па шинах 156 и 157.

Передний фронт сигнала с кыкода элемента ШШ 117 переводит триггер 113 в единичное состояниеj которое через элемент ИЛИ 126 и элемент 135 запрета поступает на пшну 58 к на шину 29. Прерывание, Во эванное зтчг-: сигпалоМз несет информацию процессору ведущей ЭВМ о начале сигнала СТРОБ ВДЩ-2. Триггер 115 переводится в единичное состояние по окончании сигнала с выхода элемента ИЛИ ll/g и прерьгвамие, вызванное этгм сигналом., несет инфорнащ-по проо.ессору ведущей ЭВМ об окончании сигнала СТРОБ В,Ц11(-2. Таким образом, сигисялы прерывания J поступающие с 158159.) несут информа1гию ведущей ЭВМ о начапе и конце сигнала СТРОБ BMl,--2 Аналогично ,цля зедомой ЭВМ сигнал прерывания форш-ipyioT триггеры 114 и 116. Установка триггеров 113--116 в исходные состояния происходит в цикле Ввод после получения кшкдого прерывания, При отключении первой ЭВМ на шику

146р(еобходимо подать ед;(1ничньгй уровень или перевести пе зеклкгча-тель 14 в единичное состояние. Тогда на выходах элемента ИЛИ 120 и злемепта РШИ 1 22появляются едияичные уровни На шинах 151э 152 и 157 присутствуют постоянные единичные уровниj, на

шинах 153-156s, 158 и 159 - постоянные нулевые уровни.

При отключении второй ЭВМ на псине 156 liMeeTCH единичный уровень, а на шине 157 - нулевой Состояние ре- . гистра готовности ЭВМ может считьгвать Б цикле Ввод через группу элементов И 47. Сигнал СТРОБ-1 подается на вход первого элемента И 47 группы, поэтому первая ЭВМ считывает в этом разряде Г, а вторая ЭВМ . Таким образоМэ каждая ЭВМ может определить свой порядковый номер

Блок 55 контроля работает следующим образом.

Каждая ЭВМ производит периодически цикл Вывод по адресу блока контроля 55. Сигнал Вывод от ведущей ЭВМ поступает через элемент И 60 на вход триггера 65, а. от ведомой через элемент И 62 на вход триггера

14

И 59 фиксирует появлени данного адреса, а глеменг НЕ 64 выдает сигнал на, nmiiy 30 для формировния сигнала . Каждьгн импульс с ньгхода злеяеита И 60 пареводит (или подтзерждае1) триггер 65 в единично состояние. TaKTOBbie импульсы с шины 58 пег:-вводя т триггер 65 в нулевое сосгс Я;;:У р-, В качестзе гркггаров 66 и 69 Г1рикзнены тригтеры Ъ-типа,

1;Бход, триггера 66 соединен с вы:г,одом триггера 65 j а D-вход триггера 69 - с выходом триггера 68, Пр нормальной работе устройства в момент действия на тактовом (динамическом) входе D -триггера 66 сигнала с шины 58 на его ) -входе еще пр.н.сутствует .потенциал 1 из-за нн.утренней задержки на срабатьтание триггера 65. Поэтому триггеры 66 и 69 находятся постоЯ1-т:-.:о в состоянии 1 Исходные состояния триггеров 67 и 70 - нулевые,,

В случае р.енспр,3-зног;ти одной из ЭВМ., т.е. при отсутствлИз напримерj сиг-налов с выхода элемента И 60.

состояние а следусчщй тактовый 1мпульс с шины 58 лереводг-хт и триггер 66 в состояние О Это приводит к переводу триггера 67 в состояние которое чврез лоуп утатор 71 поступает: на шину 23 по сигналу СТРОБ ВЛМ-2„ т.,е. поступает прерывание в ,цругзпо (ведому;С|) ЭВМ„ Ведомая ЭВМ получив данный сигнал прерывания производит :аи:кл Ввод по адресу блока 55 коктро.гш, в результате чего на выходе элемента И 61 формируется :йМ1ту.г;ьс 3 переводящий триг:гер 67 в исходное нулевое состояние При необходимости в блоке 55 контроля к вы;л.о,цам триггеров 66 и 69 можно подключить дополнительно индикаторы (например светодиоды), подающие сигпал оператору об исправной (кеисправкой) работе ЭВМ,

Блок 56 обмена инфо)мацией работает следуюЕШм образом.

Любая ЭВМ может информа- . цию в регистр 80 в цикле Вывод по его адресу. При появлении кода адреса срабатывает элемент и 73 и элемент НЕ 72 выдает сигнал на шину 30. По сигналу Вывод на вьгходе элемента И. 76 появляется импульс, по которому, во-первых, производится запись инфор:мации в регистр 80 с ШР:Н 23 данных и, во-вторых, переходит в единичное состояние одни из триггеров 82 и 83 вне зависимости от того, какая ЭВМ произвела цикл Вывод. Если, напри мер, запись произвела ведущая ЭВМ, то изменяет свое состояние триггер 82 по сигналу с выхода элемента И 75. Сигнал с выхода триггера 82 через коммутатор 84 поступает на ши 29 группы по сигналу СТРОБ ВДМ-2, т.е. прерьшание поступает в противо положную (ведомую) ЭВМ. Ведомая ЭВМ получив данный сигнал прерыванг я, производит цикл Ввод, по которому во-первых, информация с регистра 80 через группу элементов И 81 (по сигналу с выхода элемента И 74) поступает на группу шин 23 данных и, вовторых, сигнал с элемента И 78 переводит триггер 82 в исходное нулевое состояние, заканчивая обмен информацией между двумя ЭВМ. Формула изобретения 1. Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами, содержащее первую группу приемопередатчиков, первый регистр адреса, регистр защиты, первый триггер, два дешифратора адреса, первый формирователь одиночного импульса,, первый элемент запрета, первый счетчик импульсов, блок прерывания, три группы элементов И, пять элементов И, три элемента ИЛИ, элемент НЕ, группу блоков связи, при чем первые информационные входы-выходы приемопередатчиков первой группы подключены к информационным входам-выходам первой ЭВМ, информационньй вход первого регистра адреса подключен к адресному входу первой ЭВМ, вход первого формирователя одиночного импульса соединен с синхровходом первого триггера и подключен к синхровыходу первой ЭВМ, информационный вход первого триггера подключен к выходу обращения первой ЭВМ, первые входы первого и второго элементов И подключены к выходам ввода и вывода данных первой ЭВМ соответственно, первый вход третьего элемента И соединен с первым входом первого элемента ИЛИ и подключен к выходу предоставления прерывания первой ЭВМ, первый выход первого счетчика импульсов подключен к синхровходу первой ЭВМ, счетньй вход 9216 первого счетчика подключен к первому тактовому входу устройства, первые информационные входы блоков связи группы подключены к информационным выходам соответствующих абонентов, синхровходы блоков связи группы подключены к синхровыходам соответствующих абонентов, при этом вторые информационные входы-выходы приемопередатчиков первой группы через внутреннюю шину данных устройства подключены к выходам элементов И первой и второй групп, информационному входу регистра защиты, вторым информационным входам и информационным выходам блоков связи группы, вход записи первого регистра адреса соединен с выходом первого триггера и первым входом четвертого элемента И, выход которого соединен с вторым входом цервого элемента И и вторым входом второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ, первым разрешающим входом приемопередатчиков первой группь и первым входом пятого элемента И, второй вход которого соединен с вторьм выходом первого счетчика импульсов, установочный вход которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента запрета, информаТционный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и первым входом третьего элемента ИЖ, выход которого соединен с BTOpbw разрешающим входом приемопередатчиков первой группы, выход первого формирователя одиночного импульса соединен с нулевым входом первого триггера, выход третьего элемента И соединен с вторым входом третьего элемента ИЛИ, группа информационных выходов регистра защиты соединена .с первыми входами элементов И третьей группы, выходы которых соединены с группой информационных входов блока прерываний, группа информационных выходов которого соег динена с первыми входами элементов И второй группы, отличающ ее с я тем, что, с целью повышения надежности путем унифицированного подключения внещних абонентов, в не- го введены два адресных коммутатора 17 второй регистр адреса,, второй формирователь одиночного импульса, второй триггер, вторая группа приемопередат .чикоВр второй счетчик импульсов, вто рой элемент запрета, коммутатор, регистр состояния, блок контроля, блок обмена информацией, блок управления, одиннадцать элементов И, три элемента ИЛИ и четвертая группа элементов И, причем первый выход коммутатора подключен к входу требования прерывания первой ЭВМ, второй выход комму татора подключен к входу требования прерывания второй ЭВМ, информационный вход второго регистра адреса подключен к адресному выходу второй ЭВМ, синхровход второго триггера соединен с входом второго формирователя одиночного импульса и подключен к синхровьпсоду второй ЭВМ, информационный вход второго триггера подключен к выходу обращения второй ЭВМ, первые информационные входывьп оды приемопередатчиков второй группы подключены к информационным входам-выходам второй ЭВМ, первый вход шестого элемента И соединен с первым входом четвертого элемента ИЛИ и подключен к выходу предоставления прерывания второй ЭВМ, первые входы седьмого и восьмого элементов И Подключены к выходам ввода и вывода данных второй ЭВМ соответственно, первьш выход второго счетчика импульсов подключен к синхровходу второй ЭВМ, счетньм вход втор. го счетчика импульсов подключен к первому тактовому входу устройства, синхровходы блока контроля, блока прерываний и блока управления подключены ко второму, третьему и четвертому тактовым входам устройства соответственно, при этом второй выход второго счетчика импульсов соед нен с первым входом девятого элемен та И, второй вход которого соединен с первым разрешающим входом приемопередатчиков второй группы, первым входом пятого элемента ИЛИ и выходом восьмого элемента И, второй вход которого соединен с вторым входом седьмого элемента И, управляющим входом первого адресного коммутатора и выходом десятого элемента И, первый вход которого соединен с вхо дом записи второго регистра адреса и выходом второго триггера, нулевой вход которого соединен с выходом второго формирователя одиночного им 9218 пульса, установочный вход второго счетчика импульсов соединен с выходом четвертого элемента ИЛИ, второй вход которого соединен с выходом второго элемента запрета, информационный вход которого соединен с выходом пятого элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И и первым входом шестого элемента ИЛИ, выход которого соединен с вторым разрешающим входом приемопередатчиков второй группы, второй вход шестого элемента ИЛИ соединен с выходом шестого элемента И, выход второго регистра адреса соединен с информационным входом первого адресного коммутатора, первый выход которого соединен с входом первого дешифратора адреса и первым выходом хзторого адресного коммутатора, второй выход которого соединен с входом второго дешифратора, адреса и вторым выходом первого адресного коммутатора, управляющий вход второго адресного коммутатора соединен с выходом четвертого элемента И, информационный вход второго адресного коммутатора соединен с.выходом первого регистра адреса, причем вторые информационные входы-выходы приемопередатчиков второй группы через внутреннюю шину данных устройства подключены к информационным входам и выходам блока обмена информацией и выходам элементов И четвертой группы, информационньм входам регистра состояния и вторым информационным входам-вькодам приемопередатчиков первой группы, выход первого дешифратора адреса соединен с первыми входами одиннадцатого и двенадцатого элементов И, с первыми входами блока управления, блока контроля, блока обмена информацией, блоков связи группы, выход второго дешифратора адреса соединен с вторыми входами одиннадцатого и двенадцатого элементов -И, вторыми входами блока управления, блока контроля, блока обмена информацией, блоков связи группы, выходы первого и седьмого элементов И через внутреннюю шину ввода устройства соединены с первыми входами тринадцатого и четырнадцатого элементов И, первым входом запуска блока прерывания, третьим и четвертым входами блока конт роля, третьим входом блока управления, претьим входом блока обмена 19 информацией и третьими входами блоков связи группы, выходы пятого и девятого элементов И через внутреннюю шину вывода устройства соединены с первыми входами пятнадцатого и шестнадцатого элементов И, пятым и шестым входами блока контроля, четвертым входом блока обмена инфор мацией и четвертыми.входами блоков связи группы, выходы третьего и шее того элементов И через внутреннюю шину предоставления прерывания устройства соединены с вторым входом запуска блока прерывания, с вторыми входами элементов И второй группы, первые выходы блока контроля j блока обмена информацией, блоков связи группы, первый и второй выходы блок управления через внутренние шины го товности соединены с вторыми входам соответствующих элементов И третьей группы и первыми входами соответств щих элементов И первой группы, вход запрета первого и второго элементов запрета соединены через внутреннюю шину разрешения форь-мрования сигнала синхронизации устройства с выходами первого и второго элементов НЕ третьим выходом блока управления, вторыми выходами блока контроля, блока обмена информатдией и блоков связи rpynnbij четвертый выход блока управления соединен с первым входом первого элемента И элементов И четвертой группы вторыми входами третьего и четвертого элементов И и пер вым управляюпщм входом коммутатора, второй управляющий вход которого соединен с вторыми входами шестого и десятого элементов ,й и с пятым выходом блока управления, шестой выход которого соединен с седьмым и восьмым входами блока контроля, пятым и шестым входами блока обмена информацией и пятыми- входами блоков связи группы, шестые входы которых соединены с седьмым и восьмым входами блока обмена информацией, девятым и десятым входами блока контроля и седьмьм выходом блока управления, восьмой выход которого соединен с одиннадцатым входом блока контроля, девятым входом блока обмена информацией и седьмыми входами блоков связи группы, восьмьге входы которых соединены с десятым входом блока обмена информацией, двенадцатым входом блок контроля и девятым выходом блока управления, десятый выход которого сое 9220 динеи с третьи„м входом запуска блока прерывания, выход которого соединен с информационным входом коммутатора, вторые входы элементов И первой группы соединены с выходом четырнадцатого элемента И, второй вход которого соединен с входом второго элемента НЕ, выходом двенадцатого элемента И и вторыми входами шестнадцатого элемента И, вьосод которого соединен с входом записи регистра защиты, первые входы элементов И четвертой группы начиная с второго элемента И н второй вход первого элемента И четвертой группы соединены с выходами тринадцатого элемента И, второй вход которого соединен с входом первого элемента НЕ, выходом одиннадцатого элемента И и вторым входом пятнадцатого элемента И, выход которого соединен с входом записи регистра состояния, группа выходов которого соединена с группой входов блока управления и вторыми входами элементов И четвертой группы начиная со второго элемента И. 2, Устройство по П.1, отличающееся тем, что блок управления содержит два счетчика им тульсов, пять триггеров, одиннадцать элементов запрета, двенадцать элементов И, одиннадцать элементов ИЛИ, четыре элемента НЕ, два переключателя , причем первый вход первого элемента И соединен с первым входом второго элемента И и является синхровходом блока управления, первый, второй входы третьего элемента И и первый вход четвертого элемента И явлйются первыми, вторыми и третьими входами блока управления соответственно, информационные входы первого и второго элементов запрета и вход первого элемента НЕ образуют группу входов блока управления, выходы третьего и четвертого элементов запрета являются первым и вторым выходами блока управления соответственно, выход второго элемента НЕ является третьим выходом блока управления, выходы пятого и шестого элементов запрета являются четвертым и пятым входами блока управления соответственно, выход первого элемента ИЛИ соединен с первыми входами пятого и шестого; элементов И и является шестым выходом блока управления, выход седьмого

211

элемента запрета соединен с первыми входами седьмого и восьмого элементов И и является седьмым выходом блока управления, выход второго элемента ШШ соединен с синхровходом первого триггера и входом третьего элемента НЕ и является восьмым выходом блока управления, выход восьмого элемента запрета соединен с

синхровходом второго триггера и ВХОдом четвертого элемента НЕ и является девятым выходом блока управления, выход девятого элемента запрета является десятым выходом блока управления, при этом выход третьего элемента И соединен с входами второго элемента НЕ и вторым входом четвертого элемента И, выход которого соединен с информационными входами первого, второго, третьего и четвертого триггеров, выход второго элемента И соединен с счетным входом первого счетчика импульсов и первым вход-ом девятого элемента И, второй вход которого соединен с входом запрета десятого элемента запрета и выходом десятого элемента И, первый, второй, третий и четвертый входы которого соединены соответственно с первым, вторым, третьим и четвертьм выходами первого счетчика импульсов, четвертый выход которого соединен с нулевым входом пятого триггера, единичный вход которого соединен с первым выходом второго счетчика импульсови первым входом одиннадцатого элемента И, второй вход которого соединен с вторым выходом второго счетчика импульсов, счетный вход которого соединен с первым входом двенадцатого элемента И и выходом пepвo o элемента И, второй вход которого соединен с информационным входом десятого элемента запрета, входом запрета . седьмого элемента запрета и нулевым выходом пятого триггера, единичный выход которого соединен с вторым входом второго элемента И, первым входом первого элемента ИЛИ и информационным входом одиннадцатого элемента запрета, вход запрета которого соединен с выходом одиннадцатого элемента И и вторым входом двенадцатого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И, выход третьего элемента ИЛИ соединен

9222

с информационным входом девятого

элемента запрета, вход запрета которого соединен с входом запрета третьего и четвертого элементов запрет выходом четвертого элемента ИЛИ, входом запрета восьмого элемента запрета, информационным входом седьмого элемента запрета, вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом одиннадцатого элемента запрета, выход десятого элемента запрета соединен с информационным входом восьмого элемента запрета, первый контакт первого переключателя соединен с первым входом пятого элемента ИЛИ и первым входом шестого элемента ИЛИ, второй вход которого соединен с первым контактом второго переключателя и первым входом седьмого элемента ИЛИ, второй вход которого соединен с выходом первого элемента запрета, вход запрета которого соединен с выходом шестого элемента ИЛИ и входом запрета второго элемента запрета, выход которого соединен с вторым входом пятого элемента ИЛИ, выход которого соединен с входом запрета шестого элемента запрета, с первым входом восьмого элемента ИЛИ, и первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента МИ, первым входом девятого элемента ИЛИ и входом запрета пятого элемента запрета, информационный вход которого соединен с выходом восьмог элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, второй вход которого соединен втрым входом восьмого элемента И и входом первого |Элемента НЕ, выход которого соединен с вторыми входами шестого и седьмого элементов И, выход седьмого элемента И соединен с третьим входом восьмого элемента ИГШ, информационный вход шестого элемента запрета .соединен с выходом -девятого элемента ИЛИ, второй и третий входы которого соединены с выходами шестогс и восьмого элементов И соответственно, выходы третьего и четвертого элементов НЕ соединены с синхровходами третьего и четвертого триггеров соответственно, выходы которых соединены с первым и вторьм входами десятого элемента ИЛИ, выход которого соединен с информацион ным входом четвертого элемента запр та, информационный вход третьего эл мента запрета соединен с. выходом одиннадцатого элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго триггеро соответственно, вторые и третьи кон такты первого и второго переключате лей подключены к шинам нулевого и единичного потенциалов устройства соответственно. 3. Устройство по П.1, отличающееся тем, что блок конт роля содержит коммутатор, шесть триггеров, элемент НЕ и пять элемен тов И, причем выходы коммутатора и элемента НЕ являются первым и вторым выходами блока контроля соответстве но, первый и второй входы первого элемента И являются первым и вторым входами блока контроля соответствен но, первые входы второго, третьего, четвертого и пятого элементов И являются третьим, четвертым, пятым и пестым входами блока контроля соответственно, вторые входы четвертого третьего, второго и пятого элементов И являются седьмьм, восьмым, де вятым и десятым входами блока контр ля соответственно, первый и второй управляющие входы коммутатора являются одиннадцатым и двенадцатым входами блока контроля, синхровход первого триггера соединен с синхровходом второго триггера и нулевыми входами третьего и четвертого триггеров и является синхровходом блока контроля, при этом в блоке контроля выход четвертого элемента И соединен с единичным входом четвертого триггера, выход которого соединен с информационным входом второго триггера, выход которого соединен с единичным входом пятого триггера, выход которого соединен с первым информационным входом коммутатора, вто .рой информационный вход которого соединен с выходом шестого триггера, единичный вход которого соединен с выходами первого триггера, информационный вход которого соединен с выходом третьего триггера, единичный вход которого соединен с выходом пятого элемента И, третий вход которого соединен с входом элемента НЕ, выходом первого элемента И, третьими ;входами второго, третьего и четвертого элементов И, выходы второго и третьего элементов И соединены с входами пятого и шестого элементов, И соответственно. 4. Устройство по п,1, отличающееся тем, что блок обмена информацией содержит коммутатор, регистр, два триггера, группу элементов И, семь элементов И и элемент НЕ, причем выходы коммутатора и элемента НЕ являются первым и вторым выходами блока обмена информацией соответственно, группа информационных входов регистра образует группу информационных входов блока обмена информацией, первый и второй входы первого элемента И являются первыУ и вторым входами блока обмена информацией, первые входы второго, третьего, четвертого, пятого, шестого и седьмого элементов И являются третьим, четвертым, пятым, шестым, седьмым и восьмьм входами блока обмена информацией соответственно, первый и второй управляющие входы коммутатора являются девятым и десятым входами блока обмена информацией соответственно, выходы элементов И группы образуют группу информационных вьпсодов блока обмена информацией, при этом в блоке обмена информацией первый информационный вход коммутатора соединен с выходом первого триггера, единичный вход которого соединен с выходом четвертого элемента И, второй вход которого соединен с вторым входом шестого элемента.И, входом записи регистра и выходом третьего элемента И, второй вход которого соединен,с выходом первого элемента И, входом элемента НЕ и вторым входом второго элемента И, выход которого соединен с первыми входами элементов И группы, с вторыми входами пятого и седьмого элементов И, выходы которых соединены с нулевыми входами второго и первого триггеров соответственно, группа выходов регистра соединена с вторыми входами элементов И группы, выход шестого элемента И соединен с единичным входом второго триггера, выход кот торого соединен с вторым информационным входом коммутатора. 5. Устройство по П.1, отличающееся тем, что блок связи содержит приемный регистр, ком25t2

мутатор, передаюищй зе1истр, два триггера, пять элементов И, элеме.мт НЕ5 группу элементов И, причем г): уапы информационных входов передаю1 1;е)о регистра и гфиемного регистра образуют первую и вторую группы рщформадионньк входов блока связи соответственно, выходы элементов И группы образуют группу информационных выходов блока связи, вход записи передгисщего регистра соединен с единичными входами первого и второго триггеро и является синхровходом блока связиз первый и второй входы первого эпеме.нта И являются первьгм и вторым входами блока связи, первые входы второго, третьего,, четвертого и пятого

элементов И являются третьим,, четвер

тымэ пятым и шестым входами СВЯЗИ; первый и второй управлгтющие входы коммутатора являются седьмым;9226

и восьмыми входами блока связи соответственно, выходы коммутатора и элемента НЕ являются первым и вторым выходами блока связи соответственно, при этом в блоке связи вход записи приемного регистра соединен с выходом третьего элемента Hj второй вход которого соединен с выходом первого элеэлекента И,, входом злемента НЕ И с втоptJM входом второго элемента И выход которого соединен с вторыми входаг-м чeтвepтoI o и пятого элементов К и с первыми входами элементов И группы вторые входы которых соединены с группой выходов передающего регистра у вьгкоды четвертого и пятого элементов И соединены с нулевыми входам--: первого и второго триггеров соответственно, выходы которых соединены с первым и вторым информационными входами ког-даутатора,

23 25 35

Ю2

щц -. т Ч-1

Yiilfh-fl-ah

n-J

т

т

И

НТгП

уГт-Гг

да

W3

т

fSl

ФигЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения вычислительных машин в многопроцессорной вычислительной системе | 1986 |

|

SU1368883A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1984 |

|

SU1211744A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1564636A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения ЭВМ, имекгщих единый канал обмена информацией с внешними устройствами пользователя. Основной задачей изобретения является повьшен«е надежности за счет унифицированного подключения внешних абонентов. Устройство содержит два регистра адреса, два адресных коммутатора, два дешифратора адреса, две группы приемопередатчиков, два счетчика импульсов, два триггера, два элемента запрета, регистр защиты, коммутатор, блок приоритета, регистр состояния, блок управления, блок контроля, блок обмена информацией, группу блоков связи, два формировате ля ОДИНОЧНЫХ- импульсов, шестнадцать (/) элементов И, шесть элементов ИЛИ, два элемента НЕ, четыре группы элементов И. 4 з.п. ф-лы, 8 ил;

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1984 |

|

SU1211744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-02-19—Подача