1

Изобретение относится к области вычислительной техники и может быть использовано для расчета в реальном масштабе времени спектральных компонентов сложного многочастотного колебания.

Известны арифметические устройства для для вычисления быстрого преобразования Фурье (БПФ), содержащие регистры реальной и мнимой частей комплексного весового коэффициента, регистр вещественной части числа, регистр мнимой части числа, первый и второй сумматоры с запоминанием переноса.

Известные устройства сложны и обладают недостаточным быстродействием. Эти отрицательные свойства являются следствием того, что суммы поразрядных произведений при перемножении формируются каждый раз заново, что требует соответствующего времени и оборудования.

Целью изобретения является повышение быстродействия.

Сущность изобретения заключается в том, что устройство содержит два сумматора чисел, входы каждого из которых подключены к первому и второму информационным входам устройства, и три логических блока, первые входы первого и второго логических блоков соединены соответственно с выходами первого и второго сумматора чисел, вторые, третьи и четвертые входы подключены соответственно

к выходам первого и второго регистров чисел и выходу третьего логического блока, входы которого соединены с выходами регистров реальной и мнимой частей комплексного весового коэффициента, выходы первого и второго логических блоков подключены соответственно ко вторым входам первого и второго сумматоров поразрядных сумм.

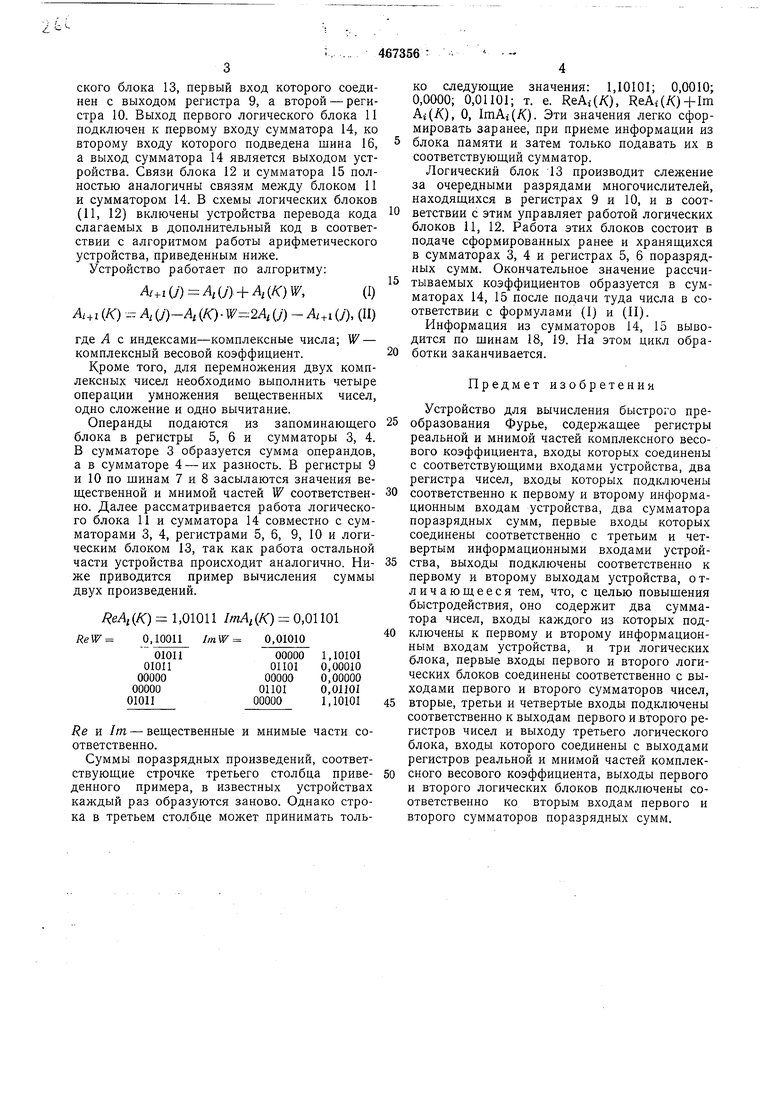

Блок-схема предлагаемого устройства представлена на чертеже, где приняты следующие обозначения: 1 и 2 - входные числовые шины; 3 и 4 - сумматоры чисел; 5 и 6 - регистры чисел; 7 - входная шина реальной части комплексного весового коэффициента; 8 - входцая шина мнимой части комплексного весового коэффициента; 9 - регистр реальной части комплексного весового коэффициента; 10 - регистр мнимой части комплексного весового коэффициента; 11, 12, 13 - логические блоки; 14, 15 - сумматоры норазрядных сумм; 16, 17 - входные щины чисел; 18, 19 - выходные шины устройства.

Шина 1 соединена со входом регистра 5 и первыми входами сумматоров 3, 4. Шина 2 подключена ко входу регистра 6 и входам сумматоров 3, 4. Выходы сумматоров 3, 4 и регистров 5, 6 связаны со входами логических блоков 11 и 12. Со входами этих логических блоков соединен также выход третьего логнчеCKoro блока 13, первый вход которого соединен с выходом регистра 9, а второй - регистра 10. Выход первого логического блока 11 подключен к первому входу сумматора 14, ко второму входу которого подведена шина 16, а выход сумматора 14 является выходом устройства. Связи блока 12 и сумматора 15 полностью аналогичны связям между блоком 11 и сумматором 14. В схемы логических блоков (11, 12) включены устройства перевода кода слагаемых в дополнительный код в соответствии с алгоритмом работы арифметического устройства, приведенным ниже. Устройство работает по алгоритму; Ac+i(j) MJ} + Ai(K)W,(I) (K} -Л(У)-ЛЛЮ-Ш- 2ЛДУ) -Л+1(у), (II) где А с индексами-комплексные числа; W - комплексный весовой коэффициент. Кроме того, для перемножения двух комплексных чисел необходимо выполнить четыре операции умножения вещественных чисел, одно сложение и одно вычитание. Операнды подаются из запоминающего блока в регистры 5, 6 и сумматоры 3, 4. В сумматоре 3 образуется сумма операндов, а в сумматоре 4 - их разность. В регистры 9 и 10 по шинам 7 и 8 засылаются значения вещественной и мнимой частей W соответственно. Далее рассматривается работа логического блока 11 и сумматора 14 совместно с сумматорами 3, 4, регистрами 5, б, 9, 10 и логическим блоком 13, так как работа остальной части устройства происходит аналогично. Ниже приводится пример вычисления суммы двух произведений. ReAt (К) 1,01011 ImAi (К) 0,01101 ReW 0,10011 ImW 0,01010 00000 01011 01101 OIOll 00000 00000 01101 00000 00000 01011 Re и Im - вещественные и мнимые части соответственно. Суммы поразрядных произведений, соответствующие строчке третьего столбца приведенного примера, в известных устройствах каждый раз образуются заново. Однако строка в третьем столбце может принимать только следующие значения: 1,10101; 0,0010; 0,0000; 0,01101; т. е. ReAi(K), ReAi(K)+lm Ai(/(), О, ImAi(/C). Эти значения легко сформировать заранее, при приеме информации из блока памяти и затем только подавать их в соответствующий сумматор. Логический блок 13 производит слежение за очередными разрядами многочислителей, находящихся в регистрах 9 и 10, и в соответствии с этим управляет работой логических блоков И, 12. Работа этих блоков состоит в подаче сформированных ранее и хранящихся в сумматорах 3, 4 и регистрах 5, 6 поразрядных сумм. Окончательное значение рассчитываемых коэффициентов образуется в сумматорах 14, 15 после подачи туда числа в соответствии с формулами (I) и (II). Информация из сумматоров 14, 15 выводится по шинам 18, 19. На этом цикл обработки заканчивается. Нредмет изобретения Устройство для вычисления быстрого преобразования Фурье, содержащее регистры реальной и мнимой частей комплексного весового коэффициента, входы которых соединены с соответствующими входами устройства, два регистра чисел, входы которых подключены соответственно к первому и второму информационным входам устройства, два сумматора поразрядных сумм, первые входы которых соединены соответственно с третьим и четвертым информационными входами устройства, выходы подключены соответственно к первому и второму выходам устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит два сумматора чисел, входы каждого из которых подключены к первому и второму информационным входам устройства, и три логических блока, первые входы первого и второго логических блоков соединены соответственно с выходами первого и второго сумматоров чисел, вторые, третьи и четвертые входы подключены соответственно к выходам первого и второго регистров чисел и выходу третьего логического блока, входы которого соединены с выходами регистров реальной и мнимой частей комплексного весового коэффициента, выходы первого и второго логических блоков подключены соответственно ко вторым входам первого и второго сумматоров поразрядных сумм.

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования фурье | 1977 |

|

SU750494A1 |

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

| Устройство для умножения по модулю | 1980 |

|

SU947860A1 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1388891A1 |

| Устройство для быстрого преобразования фурье | 1977 |

|

SU656070A1 |

| Устройство для вычисления коэффициентов фурье | 1977 |

|

SU736112A1 |

| Устройство для быстрого преобразования Фурье | 1982 |

|

SU1170462A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1982 |

|

SU1101835A1 |

Авторы

Даты

1975-04-15—Публикация

1974-03-25—Подача