1

Изобретение относится к вычисли- тэльной технике,

Известно специализированное арифметическое устройство для операдиЁ с комплексными числами, которое содержит регистры реальной и мнимой частей исходных, чисел А (К ) и W , четыре поразрядных формирователя произведений (K) ,ЗшА,- ( ЮЗтЧ Dm Д.1К)Яе,,Тг.еК; СЮЗьлХ11/, два комбинационных накапливающих сумматора р-З За счет того, что частичные произведения формируются одновременно на вькодах четырех умножителей, это устройство обладает относительно большим быстродействием, однако, из-аа того, что действия умножения и сложения производятся поразрядно, его быстродействие также недостаточно для йспользоВгэния в АУ: работающих в реальном масштабе времени с сигналами, верхняя гр&ничная частота которых больше 4-10 кГи

Наиболее близким техническим решением к изобретению является устройство

ДЛЯ вычисления коэффициентов , содержащее блоки умножения и суммирую- шиа блоки, регистры действительной и мнимой части операндов, регистры действительной и мнимой части весового коэффициента, выходы регистров действительной и мнимой части первого операнда и весового коэффициента соединены с первым ьходами соответственно с первого по четвертый блоков умножения, вторые

10 аходы которых соединены соответственно с выходами регистров действитопь- ной и мнимой части весового коэффициента, мнимой и действительной части первого операнда 1.2 J.

15

Операнды А (К) и А.,- ( j ) подаются в регистры из буферного запоминающего устройства, а значения комплексного весового коэффициента поступают из постоянного запоминающего устройства.

20 После приема исходных данньрс начинается процесс вычислений.

Однако несмотря на прямонение четырех множительных устройств и одновро-

менное выполнение операций умножения, локенпя к вычитания, устройство дает небольшим быстродействием, так как все операции выполняются поспедоватаоьно. по мере поступления разрядов, участвующих в данном вычислении чисел, В результате вычислений реальные и мнимые части вычисленных чисел () и {j } оказываются записанными в те же регистры, куда записываются исходные данные. Поэтому вычислительное устройство не может начать обработку следующих операндов до т ах пор, пока числа А (К) и . ( j ) не будут переписаны в ОЗУ, кроме того не предусмотрено никаких мер по контролю и предотвращению переполнения масштабной сетки вычислителя в п роцес-. С8 проведения вычислений,

Целью изобретения является повы.шани точности и быстродействия вычисления.

Достигается это тем, что устройство содержит блоки сдвигов, блок упра зления сдвигами, промежуточные регистры причем выходы первого и второго блоков умножения через первый и второй промежуточные регистры подключены к входам первого суммирующего блока, выходы; третьего и четвертого блоков умножения через третий и четверть промежуточные регистры поД1слючены к аходам второго суммирующего блока, выходы первого, второго суммируюхцих блоков и регистров действительной и мнимой частей второго операндов подключены к первым аходам третьего, четвертого, пятого и шестого, суммирующих блоков, вторые входы которых подключены соответсггвен- но к выходам регистров действител1ьной и мнимой частей второго операнда, выходам первого и второго суммируюии.х блоков выходы с третьего по щестой суммирующих блоков подключены к :ахо дам соответствующах промежуточных регистров и к аходу блока управления сдвигами, выход которого подключен к первым входам блоков сдви1 а, а их вторые аходы соединены с шинами операндов, выходы блоков сдвига соединены с 1входами регистров действительной и мни мой частей операндов,

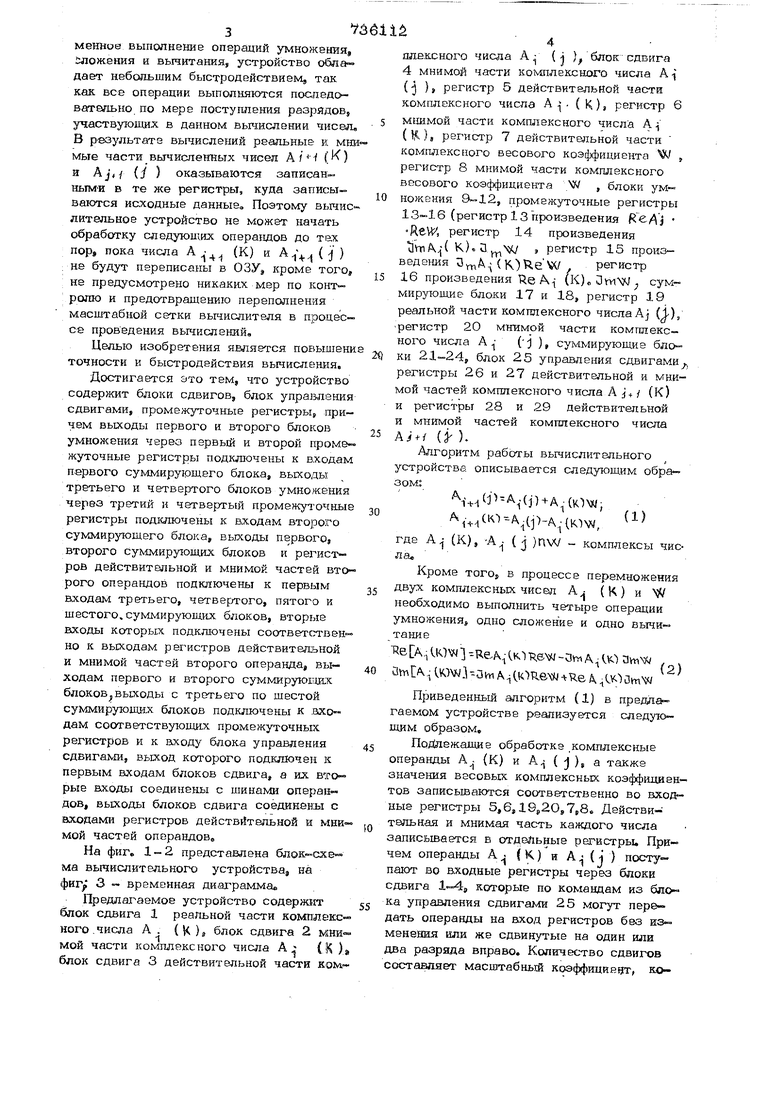

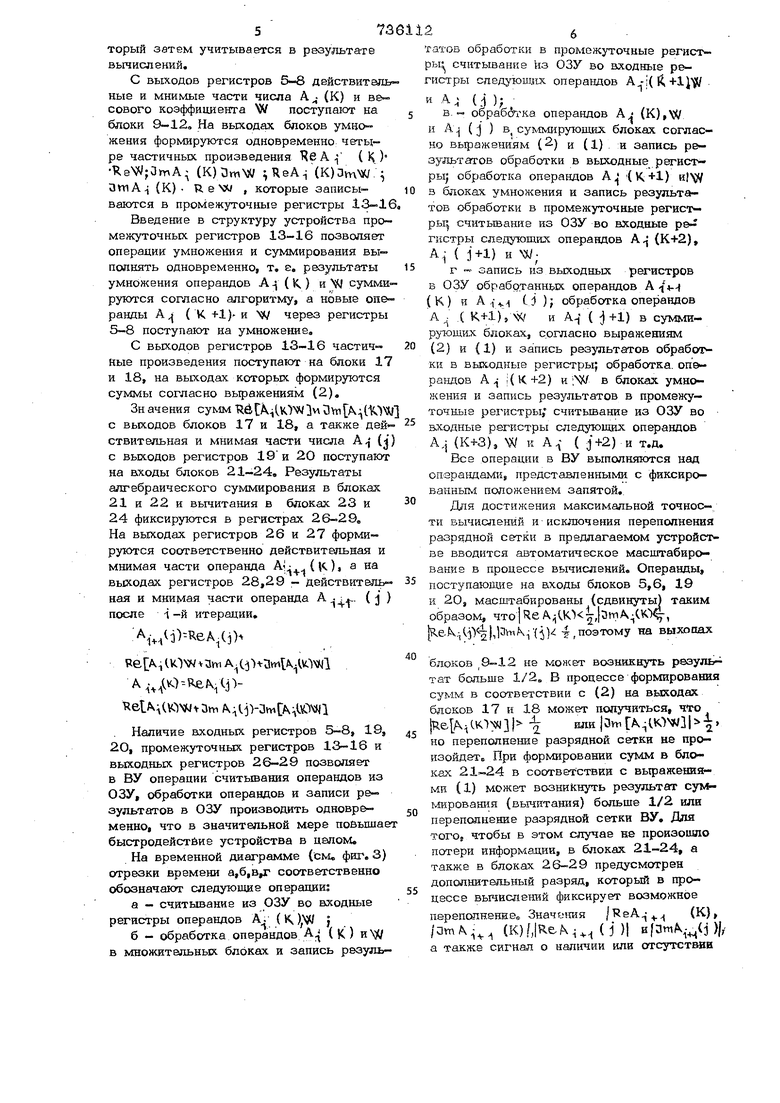

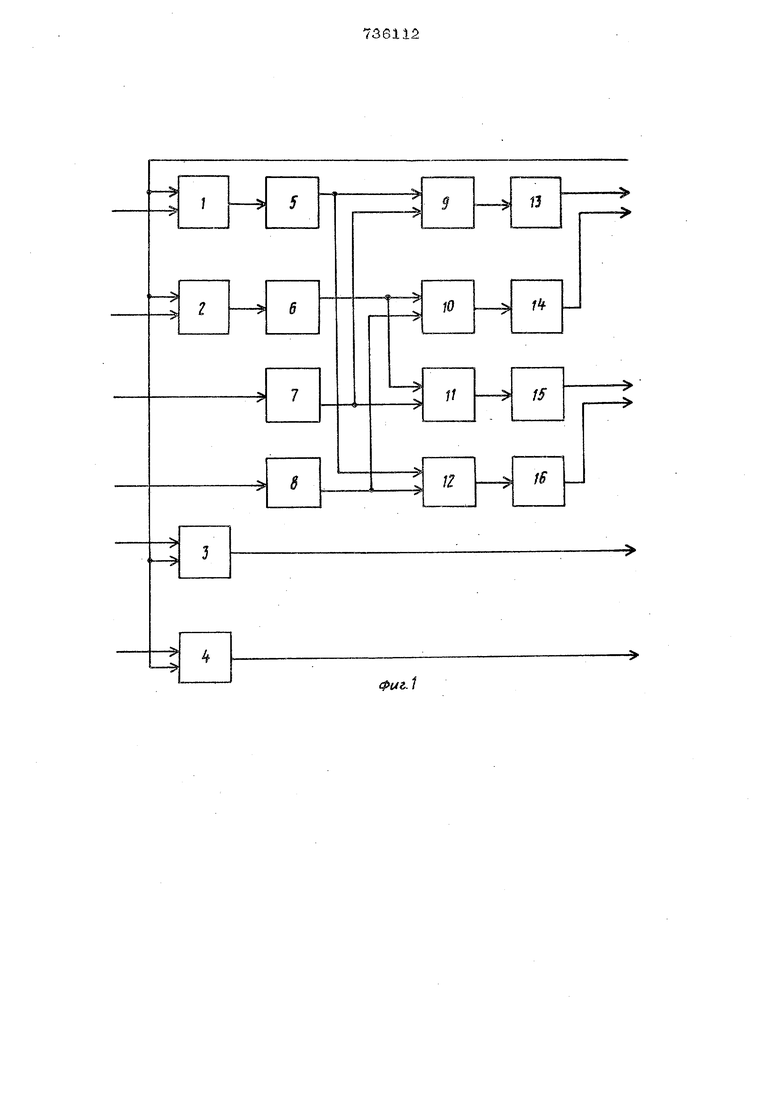

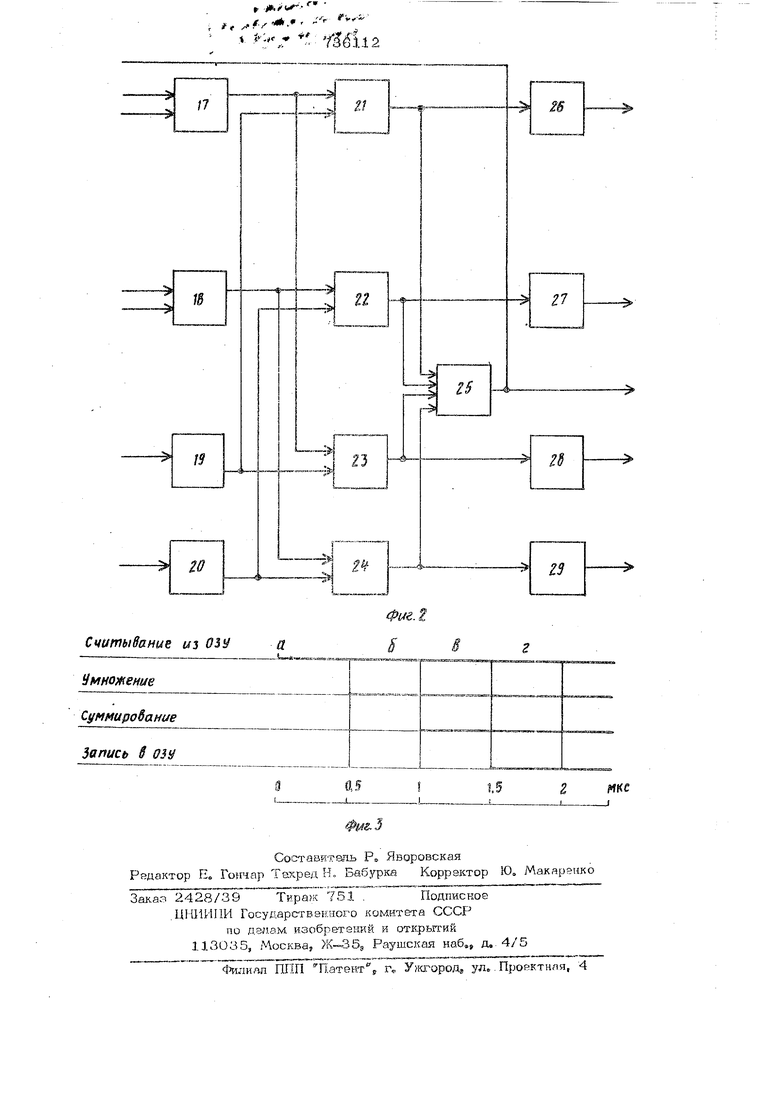

На фиг« 1-2 представлена блок-схе- ма вычислительного устройства, на фиг 3 временная диаграммав

Предла1 аемое устройство содержит блок сдвига 1 реальной частя комплексного, числа А . (К) блок сдвига 2 мни- мой части комплексного числа А (К ) блок сдвига 3 действительной части ком

плаксного числа А (j ) блок сдвига 4 мнимой части комплексного числа А -f (j ), регистр 5 действительной части комплексного числа А. (К), регистр 6

5 МЕШМОй части комплексного числа А. | , регистр 7 действительной части комплексного весового коэффициента W , регистр 8 мнимой части комплексного весового коэффициента W , блоки ум-

0 ножения 9-12, промежуточные регистры 13-16 (регистр 13 произведения Rt,W, регистр 14 произведения tlVnA -( K). регистр 15 произведения { К) UeW , регистр

5 16 произведения Re Аi (K).j суммирующие блоки 17 и 18, регистр 19 реальной части комплексного числа Aj (i-), регистр 20 мнимой части комплексКОГО числа А - (J ), суммирующее блоки 21-24, блок 25 управления сдвигами, регистры 26 и 27 действительной и мнимой частей комплексного числа А j+ / (К) и регистры 28 и 29 действительной и мнимой частей комплексного числа (f ).

Алгоритм работы вычислительного устройства описывается следующим образом:

,(j)+A,(KlW, i t --A,()-A 4KlVJ, где (К), -А. ( j )nw - комплексы числа

Кроме того в процессе перемножения двух комплексных чисел А { К) и W необходимо выполнить четыре операции умножения, одно сложение и одно вычитание

-Re А,, tK)w 1--Яел ЧЮ T ev/-C)w А, (.К) 0 avYACA..tWNWh-uHA Ckme w- ueA.(.

Приведенный алгоритм (1) в предлагаемом устройстве реализуется следуто- щим образом.

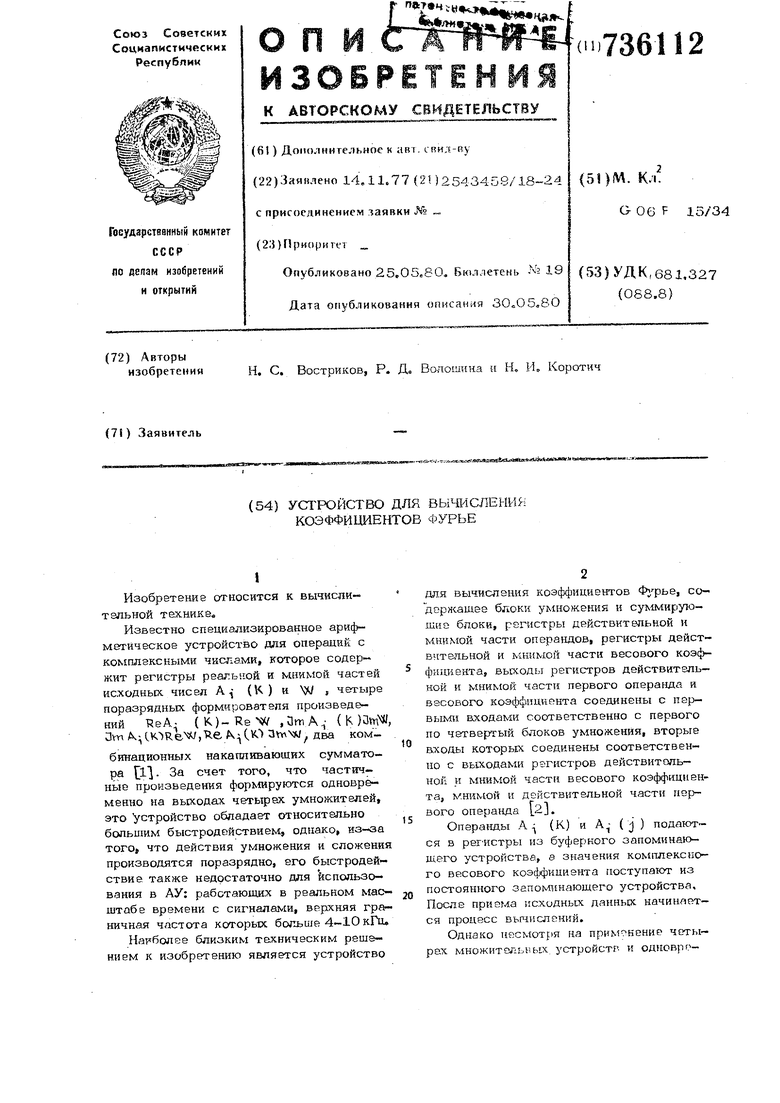

Подлежащие обработке .комплексные операнды (К) и А { J ), а также значения весовых комплексных коэффициентов записываются соответственно во входные регистры 5,6,18p2Os7,8. Действительная и мнимая часть каждого числа записывается в отдельные регистры. Причем операнды А ( К) и А (j ) поступают во аходные регистры через блока сдвига 1-4j которые по командам из блока управления сдвигами 25 могут передать операнды на аход регистров без изменения или же сдвинутые на один или два разряда вправо. Количество сдви1Х)в составляет масштабный коэффициент, ко- торый затем учитывается в результате вычислений. С выходов регистров 5-8 действиталь ные и мнимые части числа А. (К) и весового коэффициента W поступают на блоки 9-12, На вьрсодах блоков умножения формируются одновременно четыре частичных произведения ( ) ReVJjOmA- (К) ReA (K)3mW. amA-i (К)- R eW , которые записываются в промежуточные регистры 13-1 Введение в структуру устройства про межуточных регистров 13-16 позволяет операции умножения и суммирования выполнять одновременно, т. е. результаты умножения операндов А - ( К ) и Ч сумми руются согласно алгоритму, а новые опе ранды А ( К+) и V через регистры 5-8 поступают на умножещ1е, С выходов регистров 13-16 частичные произведения поступают на блоки 17 и 18, на выходах которых формируются суммы согласно вьфажениям (2), Зн ачения сумм ЯйСА Ю М и с выходов блоков 17 и 18, а также действительная и мнимая части числа (j с выходов регистров 19 и 20 поступают на В.ХОДЫ блоков 21-24, Результаты алгебраического суммирования в блоках 21 и 22 и вычитания в блоках 23 и 24 фиксируются в регистрах 26-29, На выходах регистров 26 и 27 формируются соответственно действительная и мнимая части операнда Ац (к), а на выходах регистров 28,29 - действительчасти операнда А . :.,. ( j ) ная и мнимая 1 -и итерации, после )ReA(jV (Ю ) )--ReK|tj el(Ю Mt3ni/ ;,lj)-3w A:i00 1 Наличие входных регистров 5-8, 19, 2O| промежуточных регистров 13-16 и выходных регистров 26-29 позволяет в ВУ операции считьтания операндов из ОЗУ, обработки операндов и записи результатов в ОЗУ производить одновременно, что в значительной мере повышае быстродейстбие устройства в цапом« На временной диаграмме (см, фиг. 3) отрезки времени а,б,в,г соответственно обозначают следующие операции: а - считывание из ОЗУ во входные регистры операндов А (К ),Ч } б - обработка операндов А. (К.) в множительных блоках и запись резульатов обработки в промежуточные регисты; считывание k3 ОЗУ во входные реистры следуюитх операндов (Й, . и А, (J ); в - обрабспка операндов А.- {K),VV. и (j ) в, суьширутощих блоках согласно вьфажениям (2) и (1) и запись результатов обработки в выходные регист- ры; обработка операндов Aj {К+1) и|Х(/ в блоках умножения и запись результатов обработки в промежуточные регистры считьюание из ОЗУ во входные pe-s гкстры следующих операндов А (К+2), ( J+1) и N51/; г запись из выходных регистров в ОЗУ обработанных операндов А i4(К) и А.{ (. j ); обработка операндов А ( K-H) и ( +1) в суммирующи-х блоках, согласно выражениям (2) и (1) и запись результатов обработки в выходные регистры; обработка, операндов А К К+2) и в блоках умножения и запись результатов в променсу- точные регистры, считьшание из ОЗУ во входные регистры следующих операндов А,| (К+З), W к ( J+2) и т.д. Все операции в ВУ выполшпотся над опарандами, представленными с фиксированным положением запятой.. Для достижения максимальной точное-; ти вычислений и исключения переполнения разрядной сетки в предлагаемом устройст не вводится автоматическое масштабирование в процессе вычислений. Операнды, поступающие на аходы блоков 5,6, 19 и 20, масштабированы (сдвинуть) таким образом, что 1 Re ЛДКХ|-,|зи1Л:|(КЦ;-, }РхеЦф |,13п,К-(5)4:-J,поэтому на выхооах блоков ,9-12 не может возникнуть резуль тат больше 1/2, В процессе формирования сумм в соответствии с (2) на выходах блоков 17 и 18 может получиться, что JR6 A:jCK N« -L шш)Оп., но переполнение разрядной сетки не произойдеТб При формировании сумм в блоках 21-24 в соответствии с вьфажения ми (1) может возникнуть результат сут мирования (вычитания) больше 1/2 или переполнение разрядной сетки ВУ, Для тогог чтобы в ЭТОМ случве не произошло потери информации, в блоках 21-24, а также в блоках 26-29 предусмотрен дополнительный разряд, который в процессе вычислеттай фиксирует возможное переполнение Значения /ReA. (К), /am - (К) ,MRe 4 ( j )| иfOn1,-(i )|, а также сигнал о наличии или отсутствии переполнения с блоков 21-24 поступа5от в блок управления масштабированием 25, .Сигналы О сдвигов, 1 сдвиг и 2 сдвига с выхода блока уярааленкя сдвигами 25 поступают на входы блоков сдвига 1-4, которые в соответствии с этими сигнала1 та передают значения опе- рандов на вх.оды регистров 5,6, 19 и 20 на следующей итерации без измеи9 ния или сдвинутые на один или два разряда вправо. .Арифметическое устройство, реализую щеа алгоритм быстрогр праобрааования Фурье, обладает большим быстродействием, что позволяет при его использоваНИИ в специализированных вьиислит1зль« ных устройствах значительно повысить верхний частотный предал обрабатьгаа& мых процессов. Сравнительно простая аппаратурная реализаций} большая точность вычислений являются основой для получения экономического эффекта при использовании предлагаемого устройства. Формула изобретения Устройство для вычисления коэф(}эииие тов Фурье, содержащее блоки умножения и суммирующие блоки, регистры действительной и мнимой части операндов, ре гистры действительной и мнимой части весового коэффициента, выходы регистров действительной и мнимой части первого операнда и весового коэффициента соеди нены с первыми входами соответствен но с первого по четвертый блоков умножения, вторые входы которых соединены соответственно с выходами регистров действительной части и мнймой части весового коэс|)фш1иенга, мнимой части и Действительной части первого оиератща, о т л и ч а ю ш и е с я том, что, с целью повышения точности и .быстродейстВИЯ вычисления, устройство содержит блоки сдвигов, блок управления сдвигами, промежуточные регисары, причем выходы первого и второго блоков умножения через первый и второй промежуточные регистры подключены к входам первого сул/пугарующего блока выходы третьего и четвертого блоков умножепия через третий и четвертью промежуточные регистры подключены к входам второго суммирующего блока, выходы napBoz-o, второго суммнрую1ци.х блоков и регистров действительной и мнймой частей второго опера щов подключены к первым аходам третьего, четвертого, пятого и шестого суммирующих блоков, вторые входы KOI Oрых Подключены соответственно к выходам регистров действительной и мнимой частей второго операнда, выходам первого и второго суммирующих блоков, вьрсоды с третьего по шестой суммирующих блоков подключены ко входам соответствующих промежуточных регистров и к входу блока управления сдвигами, выход которого подключен к первым входам блоков сдвига, вторые входы которых соединены с шинами операндов, выходы блоков сдвига соединены с входами регистров действительной и мнимой части операндов. Источники .информации, принятые во внимание при экспертизе 1в Авторское свидетельство СССР № 399859, 006 F 7/38, 1973. 2, Авторское свидетельство СССР № 421994, 606 F 15/34,30,03,74.

.,.

; t, f-.. - 7

- : Ш112

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Устройство для вычисления коэффициентов Фурье | 1980 |

|

SU1098004A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1282156A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| Арифметическое устройство процессора быстрого преобразования Фурье | 1981 |

|

SU999061A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Устройство для реализации алгоритма быстрого преобразования Фурье | 1982 |

|

SU1078434A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

/7

т

Zl

Считывание из ОЗУ

.

Авторы

Даты

1980-05-25—Публикация

1977-11-14—Подача