(54) ЧАСТОТНО-ДИФРОВОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДИСПЕРСИИ И МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕЙНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU374610A1 |

| Цифровой определитель дисперсии | 1984 |

|

SU1205155A2 |

| Устройство для определения экстремумов и среднего размаха случайного процесса | 1975 |

|

SU552614A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для определения параметров распределения случайных величин | 1981 |

|

SU1084811A1 |

| ВЕРОЯТНОСТНОЕ УСТРОЙСТВО ВЫЧИСЛЕНИЯ ДИСПЕРСИИ | 2022 |

|

RU2803254C1 |

| Устройство для определения дисперсии | 1975 |

|

SU642715A2 |

| Устройство для статистического анализа циклических процессов | 1984 |

|

SU1233171A1 |

| Устройство для вычисления дисперсии случайного процесса | 1981 |

|

SU1029183A1 |

| Цифровой определитель дисперсии | 1978 |

|

SU767772A1 |

Изобретение касается средств цифровой вычислительной техники и может быть использовано для измерения дисперсии входных сигналов в измерительных системах с представлением информации в частотно-им- пульсной форме.

Известны устройства, позволяющие решить поставленную задачу, содержащие счетчик математического ожидания, подключенный ко входу устройства, счетчик днеПерсии, блок управления, образцовый генератор, подключенный через делитель частоты к первой группе входов логического блока И-ИЛИ, вторая группа входов которого подключена к выходам реверсивного счетчика, входы которого через элементы И соединены соответственно со входом устройства ас выходом логического блока И-ИЛИ.

В этих устройствах возводятся в квадрат все мгновенные значения частоты, в , то время как в частотно-ци4ровых системах обычно измеряемой величине пропорционально только приращение частоты относительно некоторой начальной частоты, которое и

должно возводиться в квадрат. Кроме того, в известных устройствах не вносится поправка на ненулевое математическое ожидание измеряемой величины. Эта поправка мо жет вводиться двумя способами: либо вычитанием математического ожидания из каждого мгновенного значения измеряемой величины перед возведением в квадрат, либо вычитанием квадрата математического ожидания из результата измерения среднего квадрата (второй способ в системах без промежуточной регистрации процесса предпочтительнее, так как измерение величины позволяет определять математическое ожидание и дисперсию по одной и той же реализации). Введение поправки для увеличения точности требует дополнительных устройств вычитания кодов.

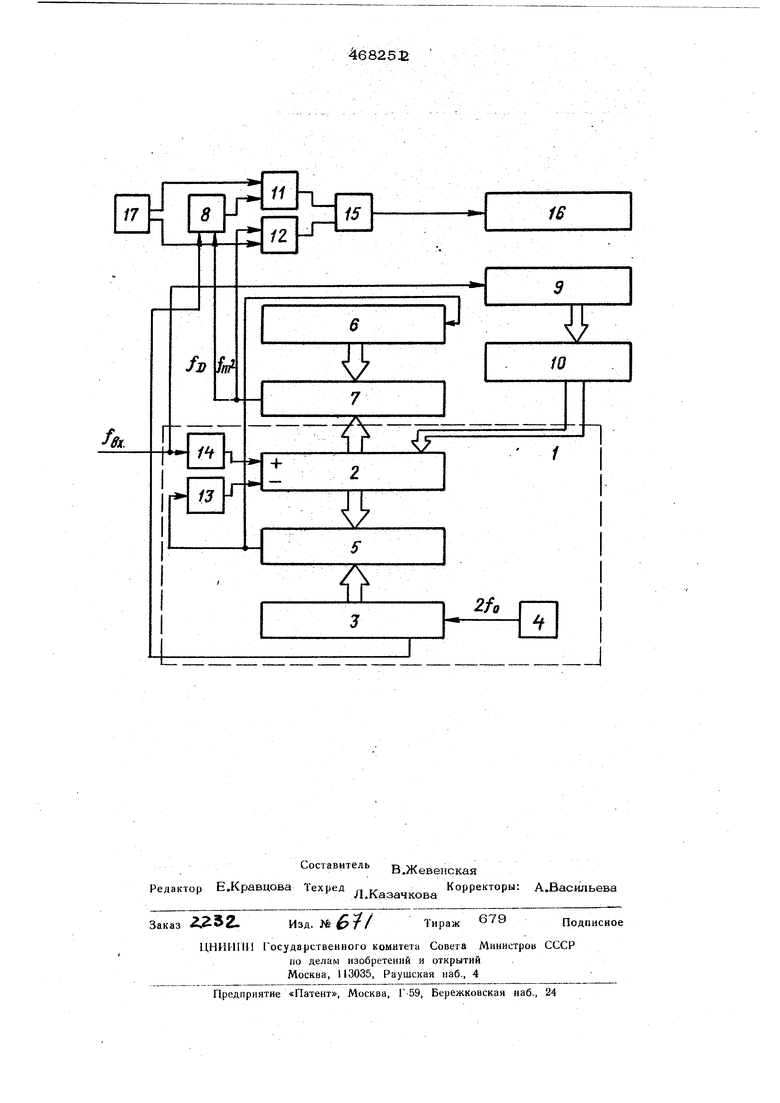

Целью изобретения является повышение точности устройства в работе путем возведения в квадрат только приращения частоты относительно начальной и введения подправки на ненулевое математическое ожидание без применения дополнительных вычитающих устройств. Предложенное устройство содержит дополнительные L; делитель частоты, логический блок И-ИЛИ, блок вычитания частот, два элемента И, элемент ИЛИ и логический блок перезаписи, подключенный к установочным входам реверсивного счетчика .соединенного инверсными выходами с потенциальными входами дополнительного логического блока И-41ЛИ, другие входы которого подключены к выходам дополнительного делителя частоты, соединещюго с выходом логического блока И-ИЛИ, выход дополнительного логического блока И-ИЛИ подключен к первому входу первого дополнительного элемента И и к первому входу блока вычитания частот, второй вход которого соединен с выходом делителя частоты, а выход подключен i к первому входу второго дополнительного эле мента И, вторые входы дополнительных элементов И соединены с блоком управления, а их выходы - через элемент ИЛИ подключены к счетчику дисперсии. Блок-схема предложенного устройства показана на чертеже, где приняты следующие обозначения: 1 - следящий преобразователь частоты в код, 2 - реверсивный счетчик, 3 - делитель частоты с промежуточными выходами несовпадающих импуль- сов, 4 - образцовый генератор, 5 - логический блок Й-ИЛИ, образующий вместе с делителем 3 так называемый двоичный (или двоично-десятичный) перемножитель, 6 - делитель частоты, аналогичный делите лю 3, 7 - логический блок И-ИЛИ, аналогичный цепи 5 и образующий вместе с делителем 6 дополнительный двоичный (или двоично-десятичный) перемножитель, 8 - блок вычитания частот, 9 - счетчик математического ожидания, 10 - логический блок перезаписи числа из счетчика 9 в счетчик 2, 11,-14 - элементы И, 15 - элемент И ЛИ, 16 - счетчик диспер сии, 17 - блок управления. В предложенном частотно-цифровом устройстве наряду с прямым использован инверсный крд числа, записанный в реверсивном счетчике 2, для возведения в квадрат частотного си1нала. Это позволяет исключить возведение в квадрат постоянной составлшощей последнего и простыми средствами осуществить вычитание поправки на ненулевое математическое ожидание. Устройство работает в два такта. В течение первого такта производится определение дисперсии и математического ожидания случайного процесса. Во втором такте вво.октсн поправка на кенуггевое математическое ожидание. Рассмотрим первый такт. В установив- , шёмся режиме выхорнан частота следящего преобразователя 1 оказывается равной с погрешностью слежения мгновенному значению 1б)(. На вход делителя частоты 6 дополнительного двоичного или двоично-десяTKHiioro перемножителя подается выходная частота следящего преобразователя f Несовпадающие импульсы с промежуточных выходов этого делителя сполаь ются для опроса по импульсным ходам ячеек И-ИЛИ, входящих в состав огического блока 7., По потенциальным ходам эти ячейки управл$потся сигналами инверсных выходов реверсивного счетчиа 2. В этом случае выходная частота логиеского блока 7 равна: K(t) ч , (. NCt) ,. (. N, щкс -макс )- прямой код числа, записанного в реверсивный счетчик 2; (.t) - инверсный код того же числа. С целью дсклюнетя возведения в квадат постоянной составляющей сигнала частоту импульсов опорного сигнала на входе делителя 3 выбирают равной 21 g , при этом код N (t ), записанный в реверсивном счетчике 2, относится к числу состояний реверсивного счетчика 1 как N(fc) fflx N taкc afo- ex / i N -6 1-217) ia 65cU2fo 2.fe i o A lt 3L2fo- o- f(tn , fo лТО afn «0 T. e, в квадрат возводится только приращение частоты входного преобразователя uf(t) пропорциональное ординате случайного процесса. Для исключения члена J требуется дополнительный блок 8, представляю - щий собой цепь вычитания частот. Частота , пропорциональная квадрату мгновенного значения случайного процесса, получает, который может ся с коэффициентом быть учтен в счетчике дисперсии 16. Таким образом, в первом такте элементы И 11, 13, 14 открыты и пропускajQT сигнал fox на реверсивный счетчик2 пропорциональную квадр и частоту ту мгновенного значения л. , через бло 8 на счет;1ШС 16. В начале второго такта для введения поправки на ненулевое значение математического ожидания случайного процесса осуществляется параллельная перезапись из старших разрядов счетчика математиI ческого ожидания в соответствующие разряды реверсивного счетчика. На время второго такта прерываются вхоДы частот- ных сигналов от входного преобразователя и обратной связи преобразователя 1 (аапрещена работа элементов И 11, 13, 14 и открыт элемент 12). В квадрат возводит ся код, соответствующий математическому ожиданию, т. е. на выходе логического блока 7 подавляется частота f.p2.-Xrn..., где К - коэффициент пропорциональности. Для осуществления операции вычитания, поправки выходная частота f г. блока 7 подается на счетчик 16, минуя цепь вычитания частот, а емкость счетчика 16 выбирают равной произведению длительности второго такта на частоту fp . 2 Предмет изобретения Частотно-цифровое устройство для определения дисперсии и математического ожидания, содержащее счетчик математического ожидания, подключенный ко входу устройства, счетчик дисперсии, блок управления, образцовый генератор, подключенный через делитель частоты к первой группе входов логического блока И-ИЛИ, вторая группа входов которого подключена к выходам реверсивного счетчика, входы которого через элементы И соединены соответствен- но со входом устройства и выходом логического блока И-ИЛИ, отличающееся тем, что, с целью повыщения точности работы, устройство содержит дополнительные делитель частоты, логический блок И-Или, блок вычитания частот, два элемента И, элемент ИЛИ и логический блок перезаписи, подключенный к установочным входам : реверсивного счетчика, со- единннного инверсными выходами с потенциальными входами дополнительного логического блока И-ИЛИ, другие входы кото- . рого подключены к выходам дополнительного делителя частоты, соединенного с выходом логического блока И-ИЛИ, выход дополнительного логического блока И-ИЛИ подключен к первому входу первого дополнительного элемента И и к первому вхрду блока вычитания частот, второй вход которого соединен с выходом делителя частоты, а выход подключен к первому входу второго дополнительного элемента И, вторые входы дополнительных элементов И соединены с блоком управления, а юс выходы - через элемент ИЛИ - подклюены к счетчику дисперсии.

Авторы

Даты

1975-04-25—Публикация

1974-04-24—Подача