11

Изобретение относится к вычислительной технике и может быть -использовано в аппаратуре, предназначенной для статистической обработки результатов измерений.

Цель изобретения - расширение функциональных возможностей за счет формирования гистограмм скользящих оценок математического ожидания и дисперсии.

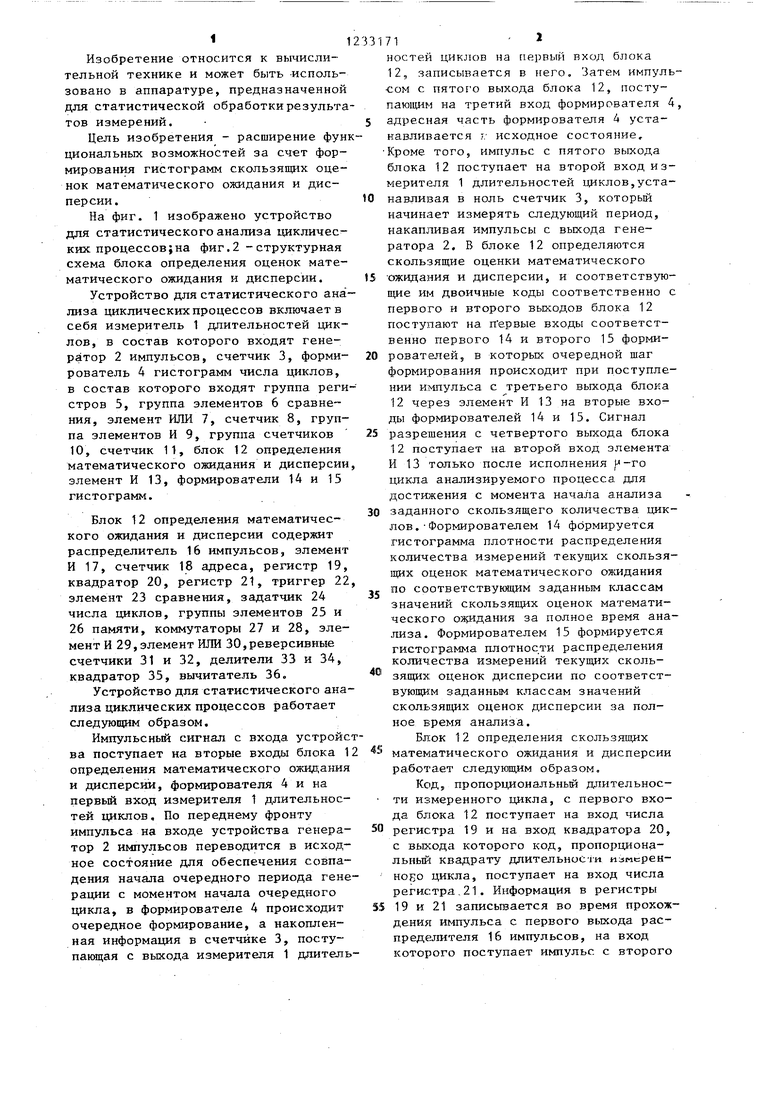

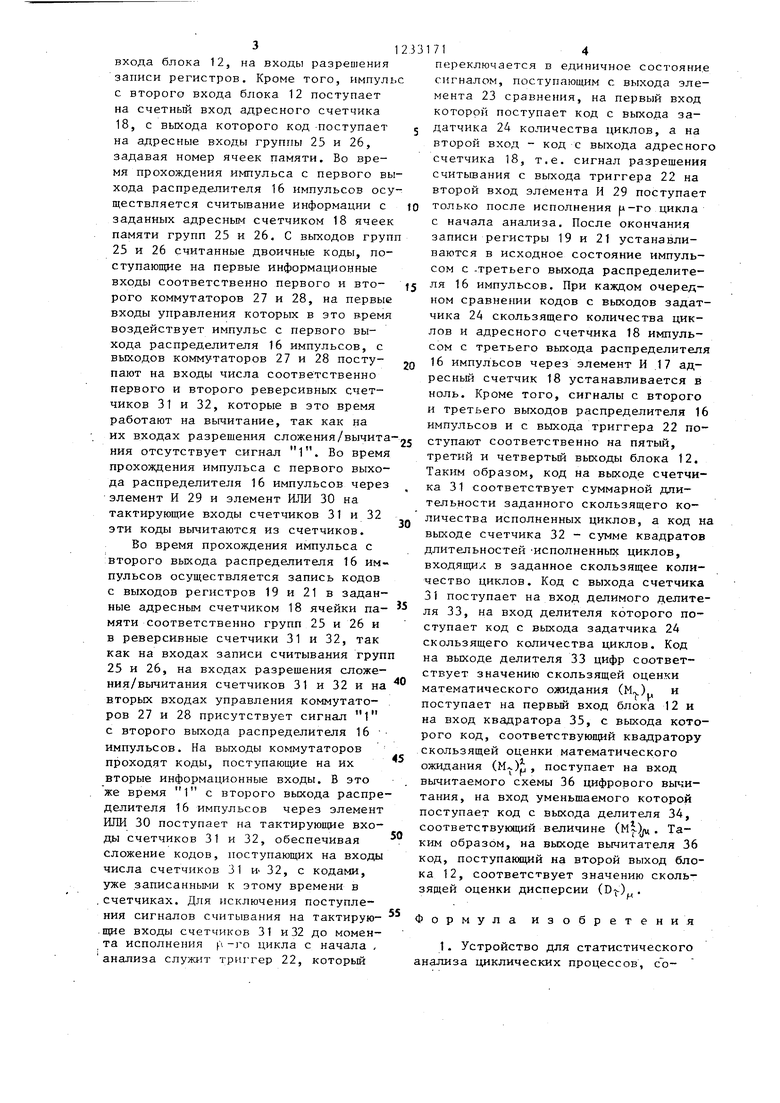

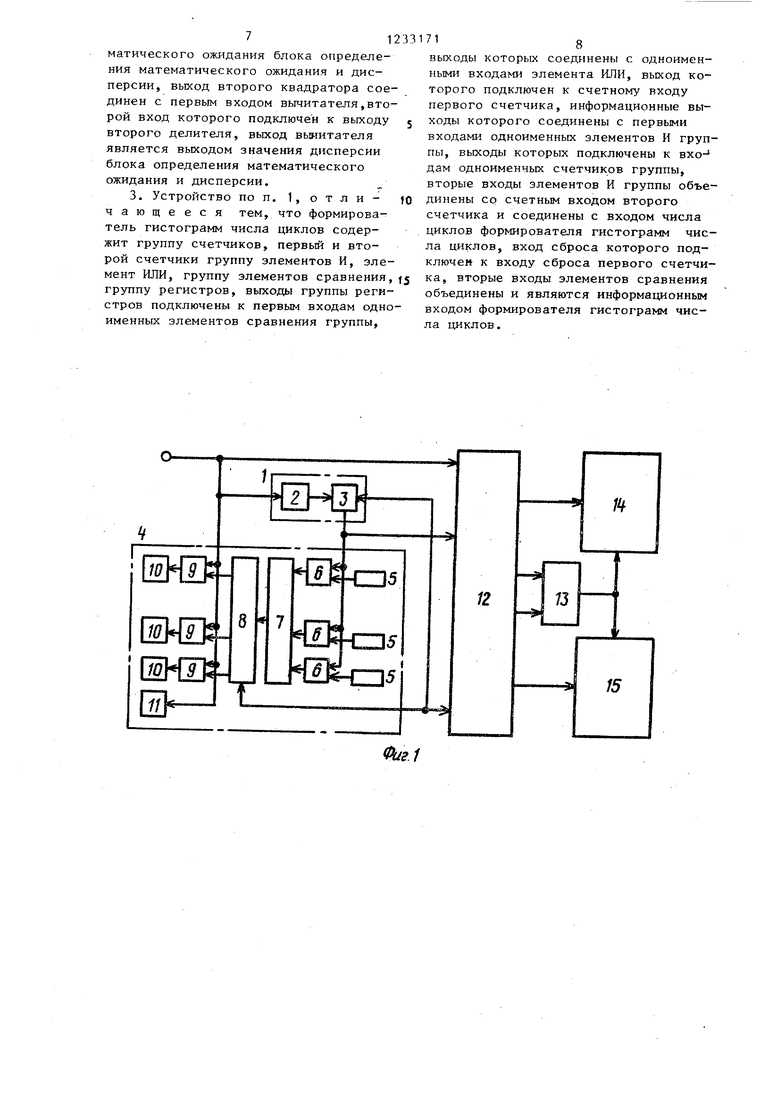

На фиг. 1 изображено устройство для статистического анализа циклических процессов; на фиг.2 - структурная схема блока определения оценок математического ожидания и дисперсии.

Устройство для статистического анализа циклических процессов включает в себя измеритель 1 длительностей циклов, в состав которого входят генератор 2 импульсов, счетчик 3, форми- рователь 4 гистограмм числа циклов, в состав которого входят группа регистров 5, группа элементов 6 сравнения, элемент ИЛИ 7, счетчик 8, группа элементов И 9, группа счетчиков 10, счетчик 11, блок 12 определения математического ожидания и дисперсии элемент И 13, формирователи 14 и 15 гистограмм.

Блок 12 определения математического ожидания и дисперсии содержит распределитель 16 импульсов, элемент И 17, счетчик 18 адреса, регистр 19, квадратор 20, регистр 21, триггер 22, элемент 23 сравнения, задатчик 24 числа циклов, группы элементов 25 и 26 памяти, коммутаторы 27 и 28, элемент И 29,элемент ИЛИ 30,реверсивные счетчики 31 и 32, делители 33 и 34, квадратор 35, вычитатель 36.

Устройство для статистического анализа циклических процессов работает следующим образом.

Импульсный сигнал с входа устройства поступает на вторые входы блока 12 определения математического ожидания и дисперсии, формирователя 4 и на первьй вход измерителя 1 длительностей циклов. По переднему фронту импульса на входе устройства генера- тор 2 импульсов переводится в исходное состояние для обеспечения совпадения начала очередного периода генерации с моментом начала очередного цикла, в формирователе 4 происходит очередное формирование, а накопленная информация в счетчике 3, посту- пакнцая с выхода измерителя 1 длитель71 J

костей циклов на первый вход блока 12, записывается в него. Затем импулсом с пятог о выхода блока 12, поступающим на третий вход формирователя адресная часть формирователя 4 устанавливается . исходное состояние, Кроме того, импульс с пятого выхода блока 12 поступает на второй вход измерителя 1 длительностей циклов,устанавливая в ноль счетчик 3, который начинает измерять следующий период, накапливая импульсы с выхода генератора 2. В блоке 12 определяются скользящие оценки математического ожидания и дисперсии, и соответствующие им двоичные коды соответственно первого и второго выходов блока 12 поступают на п ервые входь соответственно первого 14 и второго 15 формирователей, в которых очередной шаг формирования происходит при поступлении и:мпульса с третьего выхода блока 12 через элемент И 13 на вторые входы формирователей 14 и 15. Сигнал разрешения с четвертого выхода блока 12 поступает на второй вход элемента И 13 только после исполнения р-го цикла анализируемого процесса для достижения с момента начала анализа заданного скользящего количества циклов. -Формирователем 14 формируется гистограмма плотности распределения количества измерений текущих скользящих оценок математического ожидания по соответствующим заданным классам значений скользящих оценок математического ожидания за полное время анализа. Формирователем 15 формируется гистограмма плотности распределения количества измерений текущих скользящих оценок дисперсии по соответст- вующн;м заданным классам значений скользящих оценок дисперсии за полное Е:ремя анализа.

Блок 12 определения скользящих математического ожидания и дисперсии работает следующим образом.

Код, пропорциональный длительности измеренного цикла, с первого входа блока 12 поступает на вход числа регистра 19 и на вход квадратора 20, с вькода которого код, пропорциона- льньм квадрату длительности иамерен- HOJ5O цикла, поступает на вход числа регистра,21. Информация в регистры 19 и 21 записывается во время прохождения импульса с первого выхода распределителя 16 импульсов, на вход которого поступает импульс, с второго

входа блока 12, на входы разреиения записи регистров. Кроме того, импуль с второго входа блока 12 поступает на счетный вход адресного счетчика 18, с выхода которого код -поступает на адресные входы группы 25 и 26, задавая номер ячеек памяти. Во время прохождения импульса с первого выхода распределителя 16 импульсов осуществляется считывание информации с заданных адресным счетчиком 18 ячеек памяти групп 25 и 26, С выходов груп 25 и 26 считанные двоичные коды, поступающие на первые информационные входы соответственно первого и второго коммутаторов 27 и 28, на первые входы управления которых в это время воздействует импульс с первого выхода распределителя 16 импульсов, с выходов коммутаторов 27 и 28 поступают на входы числа соответственно первого и второго реверсивных счетчиков 31 и 32, которые в это время работают на вычитание, так как на

20 16 импульсов через элемент И 17 ресный счетчик 18 устанавливаетс ноль. Кроме того, сигналы с втор и третьего выходов распределител импульсов и с выхода триггера 22

их входах разрешения сложения/вычита-25 ступают соответственно на пятый,

1, Во время

ния отсутствует сигнал прохождения импульса с первого выхода распределителя 16 импульсов через элемент И 29 и элемент ИЛИ 30 на тактирующие входы счетчиков 31 и 32 эти коды вычитаются из счетчиков.

Во время прохождения импульса с второго выхода распределителя 16 импульсов осуществляется запись кодов с выходов регистров 19 и 21 в заданные адресным счетчиком 18 ячейки памяти соответственно групп 25 и 26 и в реверсивные счетчики 31 и 32, так как на входах записи считывания групп 25 и 26, на входах разрешения сложения/вычитания счетчиков 31 и 32 и на вторых входах управления коммутаторов 27 и 28 присутствует сигнал 1 с второго выхода распределителя 16 импульсов. На выходы коммутаторов проходят коды, поступающие на их вторые информационные входы. В это

же время 1 с второго выхода распределителя 16 импульсов через элемент ИЛИ 30 поступает на тактирующие входы счетчиков 31 и 32, обеспечивая сложение кодов, поступающих на входы числа счетчиков 31 И 32, с кодами, уже записанными к этому времени в

.счетчиках. Для исключения поступления сигналов считывания на тактирую.щие входы счетчиков 31 и 32 до момента исполнения |. i цикла с начала ,

анализа служит триггер 22, который

30

J5

40

45

50

55

третий и четвертый выходы блока Таким образом, код на выходе сче ка 31 соответствует суммарной дл тельности заданного скользящего личества исполненных циклов, а к выходе счетчика 32 - сумме квадр длительностей исполненных циклов входящих в заданное скользящее ко чество циклов. Код с выхода счетч 31 поступает на вход делимого дел ля 33, на вход делителя которого ступает код с выхода задатчика 24 скользящего количества циклов. Ко на выходе делителя 33 цифр соотве ствует значению скользящей оценки математического ожидания (M,v).j и поступает на первьй вход блока 12 на вход квадратора 35, с выхода к рого код, соответствующий квадрат скользящей оценки математического ожидания (М)р , поступает на вход вычитаемого схемы 36 цифрового вы тания, на вход уменьщаемого котор поступает код с выхода делителя 3 соответствующий величине (Мj-)ju . Т ким образом, на выходе вычитателя код, поступакяций на второй выход ка 12, соответствует значению ско зящей оценки дисперсии (D).

Формула изобретени

1, Устройство для статистическо анализа циклических процессов, сЪпереключается в единичное состояние сигналом, поступающим с выхода элемента 23 сравнения, на первый вход которой поступает код с выхода эа- датчика 24 количества циклов, а на второй вход - код с выхода адресного счетчика 18, т.е. сигнал разрешения считьшания с выхода триггера 22 на второй вход элемента И 29 поступает

только после исполнения р-го цикла с начала анализа. После окончания записи регистры 19 и 21 устанавливаются в исходное состояние импульсом с -третьего выхода распределителя 16 импульсов. При каждом очередном сравнении кодов с выходов задат- чика 24 скользящего количества циклов и адресного счетчика 18 импульсом с третьего выхода распределителя

16 импульсов через элемент И 17 адресный счетчик 18 устанавливается в ноль. Кроме того, сигналы с второго и третьего выходов распределителя 16 импульсов и с выхода триггера 22 поступают соответственно на пятый,

30

5

0

5

0

5

третий и четвертый выходы блока 12. Таким образом, код на выходе счетчика 31 соответствует суммарной длительности заданного скользящего количества исполненных циклов, а код на выходе счетчика 32 - сумме квадратов длительностей исполненных циклов, входящих в заданное скользящее количество циклов. Код с выхода счетчика 31 поступает на вход делимого делителя 33, на вход делителя которого поступает код с выхода задатчика 24 скользящего количества циклов. Код на выходе делителя 33 цифр соответствует значению скользящей оценки математического ожидания (M,v).j и поступает на первьй вход блока 12 и на вход квадратора 35, с выхода которого код, соответствующий квадратору скользящей оценки математического ожидания (М)р , поступает на вход вычитаемого схемы 36 цифрового вычитания, на вход уменьщаемого которой поступает код с выхода делителя 34, соответствующий величине (Мj-)ju . Таким образом, на выходе вычитателя 36 код, поступакяций на второй выход блока 12, соответствует значению скользящей оценки дисперсии (D).

Формула изобретения

1, Устройство для статистического анализа циклических процессов, сЪдержащее блок определения математического ожидания и дисперсии, отличающееся тем, что, с целью расширения функциональных возможностей за счет формирования гистограмм скользящих оценок математического ожидания и дисперсии, в него введены счетчик, элемент И, генерато импульсов, первый и второй формирователи гистограмм, формирователь гистограмм числа циклов, вход числа циклов которого объединен с входом запуска генератора импульсов и информационным входом блока определения математического ожидания и дисперсии и подключен к информационному входу устройства, выход генератора импульсов соединен со счетным входом счетчика, вход сброса которого подключен к выходу сброса блока определения математического ожидания и Д11сперсии и объединен с входом сброса формирователя гистограмм числа циклов, информационный вход которого объединен с входом задания длительности циклов блока определения математического ожидания и дисперсии и соединен с выходом счетчика, выход математического значения, -первый и второй выходы готовности и выход значения дисперсии блока определения математического ожидания и дисперсии подключен соответственно к информационному входу первого формирователя гистограмм, к первому и второму входам элемента И, к информационному входу второго формирователя гистограмм, вход синхронизации которого объедине с входом синхронизации первого формирователя гистограмм и соединен с выходом элемента И,

2. Устройство по П.1, отличающееся тем, что блок определения математического ожидания и дисперсии содержит распределитель импульсов, первый и второй реверсивные счетчики, счетчик адреса, регист ры элементы И, элемент ИЛИ, делители, квадраторы, коммутаторы, вьгчита- Т(2ль, элемент сравнения, группы элементов памяти, -задатчик числа циклов выход которого подключен к входам делителя первого и второго депител:я и к первому входу элемента сравнения второй вход которого объединен с адресными входами первой и второй груп элементов памяти и подключен к вькод счетчика tvipeca, вход установки в

0

5

0

5

0

5

5

0

5

О которого объединен с входом синхронизации распределителя импульсов и соединен с выходом счетчика, счетный вход счетчика адреса подключен к выходу первого элемента И, первый вход которого объединен с тактовым входом первого триггера и соединен с выходом элемента сравнения, прямой выход пер- )зого триггера подключен к первому входу готовности блока определения математического ожидания и дисперсии и первому входу второго э.аемента И, второй вход которого объединен с первыми управляютцими- входами первого и второго коммутаторов, информационными входами первого и второго регистров и соединен с первым выходом распределителя импульсов, второй вход которого подключен соответственно к первым информационным входам первой и второй Г рупп элементов памяти, входам сложения-вь/читания первого и второго реверсивных счетчиков, первому входу .элемента ИЛИ, к вторым управляю- П1;им входам первого и второго коммутаторов и выходу сброса блока определения математического ожидания и дисперсии, выход второго элемента И подключен к второму входу элемента ИЛИ, выход которого соединен с тактовыми входами первого и второго реверсивных счетчиков, информационные входы кото- pbDC подключены соответственно к выходам первого и второго коммутаторов, первые информационные входы которых соединены соответственно с выходами элементов пятой, первой и второй групп, информационные входы которых объединены с вторыми информационными входами ко1ммутаторов и подключены соответственно к выходам первого и второго регистров, входы записи которых: объединены с вторым входом первого элемента И и соединены с третьим выходом распределителя импульсов .и являются вторым выходом готовности блока опре 5еления математического о;кидания и дисперсии, информационный вход первого регистра и первого квадратора объединены и подключены к входу задания длительности циклов блока определения математического ожидания и дисперсии, выходы первого и второго реверсивньпс счетчиков соединены соответственно с входами делимого, первого и второго делителей, выход первого делителя подключен к входу второго КБа,дратора и к выходу значения мате71233

магического ожидания блока определения математического ожидания и дисперсии, выход второго квадратора соединен с первым входом вычитателя,второй вход которого подключен к выходу 5 второго делителя, выход вынитателя является выходом значения дисперсии блока определения математического ожидания и дисперсии.,

3. Устройство по п. 1, о т л и - 0 чающееся тем, что формирователь гистограмм числа циклов содержит группу счетчиков, первый и второй счетчики группу элементов И, элемент ИЛИ, группу элементов сравнения, 5 группу регистров, выходы группы регистров подключены к первым входам одноименных элементов сравнения группы,

718

выходы которых соединены с одноименными входами элемента ИЛИ, выход которого подключен к счетному входу первого счетчика, информационные выходы которого соединены с первыми входами одноименных элементов И группы, выходы которых подключены к вхо- дам одноименных счетчиков группы, вторые входы элементов И группы объединены со счетным входом второго счетчика и соединены с входом числа циклов формирователя гистограмм числа циклов, вход сброса которого подключен к входу сброса первого счетчика, вторые входы элементов сравнения объединены и являются информационным входом формирователя гистограмм числа циклов.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР НАПРЯЖЕНИЯ | 1990 |

|

RU2024880C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР КАЧЕСТВА ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1993 |

|

RU2096788C1 |

| Устройство для вычисления оценок математического ожидания и дисперсии | 1983 |

|

SU1280392A1 |

| Цифровой определитель дисперсии | 1984 |

|

SU1205155A2 |

| Цифровой определитель дисперсии | 1978 |

|

SU767772A1 |

| КАРДИОМОНИТОР КВАНТИЛЬНЫЙ | 1994 |

|

RU2107455C1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU949788A1 |

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

| Устройство для вычисления дисперсии случайного процесса | 1981 |

|

SU1029183A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

Изобретение относится к области вычислительной техники и может быть использовано в аппаратуре, предназначенной для статистической обработкирезультатов измерений.. Цель изобретения - расширение функциональных возможностей за счет формирования гисто-, грамм скользящих оценок математического ожидания и дисперсии. Цель изобретения достигается за счет введения в устройство счетчика, элемента И, генератора импульсов, двух формирователей гистограмм и формирователя гистограмм числа циклов с соответствующими функциональными связями между ними и известными блоками устройства. Блок определения математического ожидания и дисперсии, а также формирователь гистограмм числа циклов имеют сложную структуру и описаны в втором и третьем пунктах формулы изобретения. 2 з.п. ф-лы. 2 ил. (/)

о--ц

Составитель И. Мухин Редактор С. Патрушева Техред О,Сопко

Заказ 2772/51 , Тираж 671 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С. Черни

| Устройство для определения статистических характеристик | 1976 |

|

SU716044A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения дисперсии | 1978 |

|

SU860080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-06-22—Подача