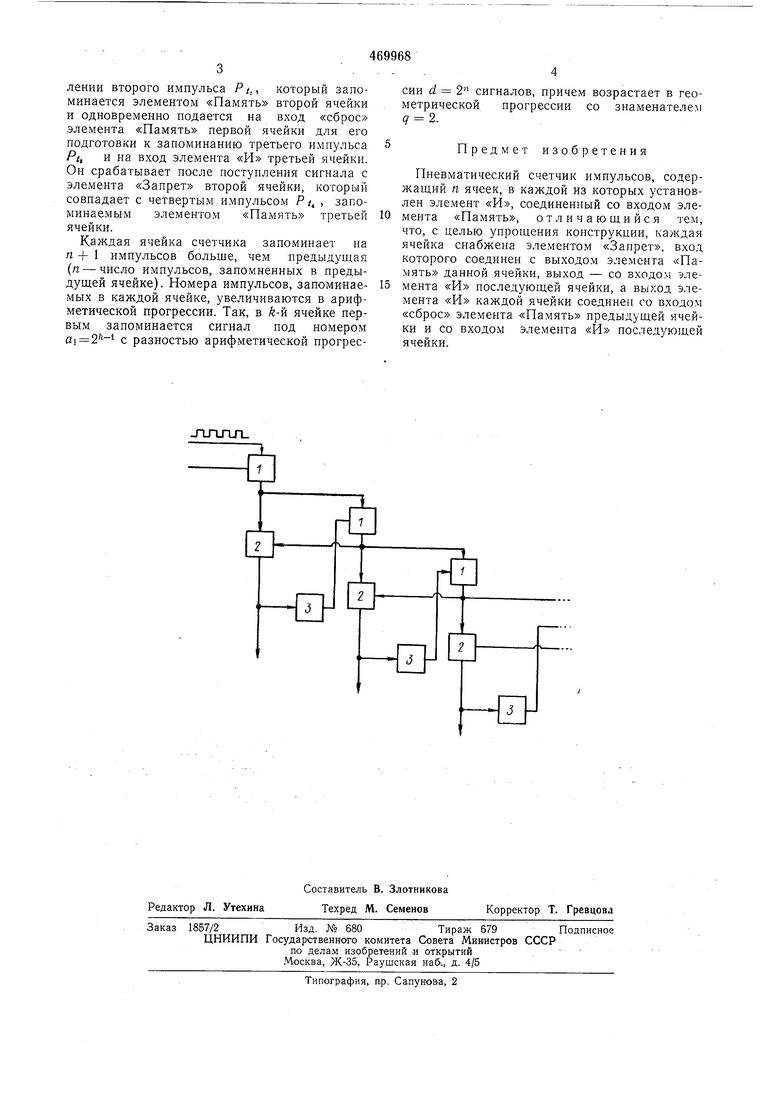

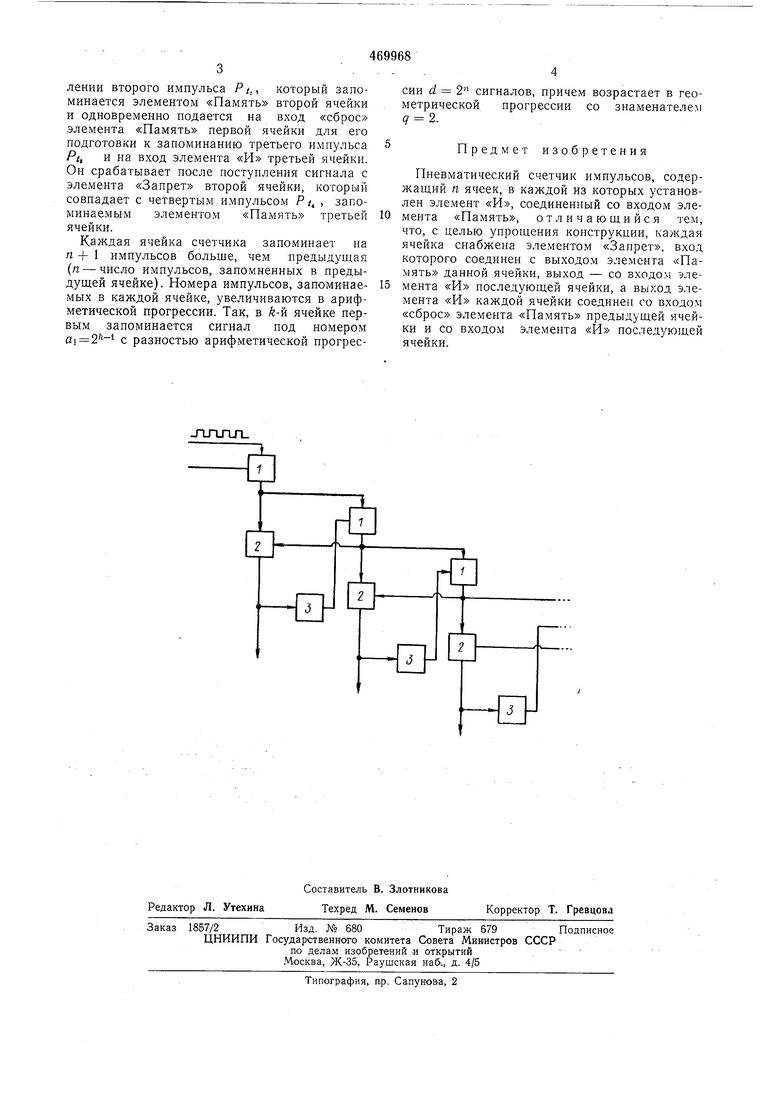

лении второго импульса Р/,, который запоминается элементом «Память второй ячейки и одновременно подается на вход «сброс элемента «Память первой ячейки для его подготовки к запоминанию третьего импульса Pt, и на вход элемента «П третьей ячейки. Он срабатывает после поступления сигнала с элемента «Запрет второй ячейки, который совпадает с четвертым импульсом Р t , запоминаемым элементом «Память третьей ячейки.

Каждая ячейка счетчика запоминает на п + 1 импульсов больше, чем предыдущая (я - число импульсов, запомненных в предыдущей ячейке). Номера импульсов, запоминаемых в каждой ячейке, увеличиваются в арифметической прогрессии. Так, в й-й ячейке первым запоминается сигнал под номером 01 с разностью арифметической прогрессии d 2 сигналов, причем возрастает в геометрической прогрессии со знаменателем 7 2.

Предмет изобретения

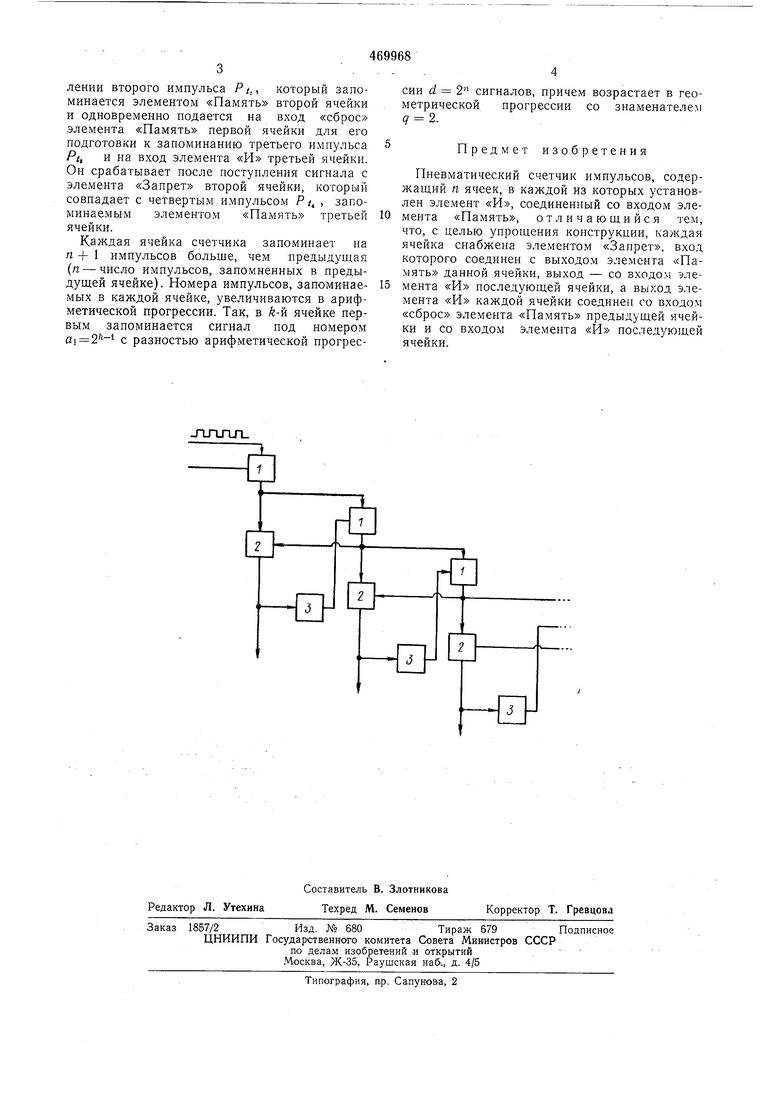

Пневматический счетчик импульсов, содержащий п ячеек, в каждой из которых установлен элемент «И, соединенный со входом элемента «Память, отличающийся тем, что, с целью упрощения конструкции, каждая ячейка снабжена элементом «Запрет, вход которого соединен с выходом элемента «Память данной ячейки, выход - со входом элемента «И последующей ячейки, а выход элемента «И каждой ячейки соедине; со входом «сброс элемента «Память предыдущей ячейки и со входом элемента «И последующей ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пневматический счетчик импульсов | 1977 |

|

SU618732A2 |

| Пневматический счетчик импульсов | 1982 |

|

SU1024892A1 |

| Пневматический двоично-десятичный декадный счетчик | 1980 |

|

SU1049885A1 |

| Позиционный дискретный электропривод | 1985 |

|

SU1352474A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для многоточечной сигнализации | 1990 |

|

SU1795496A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

Авторы

Даты

1975-05-05—Публикация

1972-12-11—Подача