(54) УСТРОЙСТВО ДЛЯ РЕДАКТИРОВАНИЯ ИНФОРМАЦИИ

1

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах и. системах пля обработки информации.

Известно устройство аля реаактиро вания информации, сопержащее регистр BBota-вывоаа, регистр числа, блок памяти символов, регистр формирования апресов, первый и второй регистры начального апреса, регистр метки, регистр по- |0 полните пьного а ареса и блок управле.

ния

Редактирование ввеаенной информации осуществляется путем последовательного во времени чтения символов из блока па- j мяти, поэтому недостатком данного уст.ройства является низкое быстропействие.

Известно также устройство для редактирования информации, содержащее регистр команпного слова, регистр маски 20 регистр информации, коммутатор информации, сумматор маски, узел уплотнения, узел расстановки, регистр результата, . блок местной памяти, формирователь ааресов записи, формирователь ааресов об- мена f 23.

За один такт работы устройства редактируется часть строки входвой ивфо{мааив (1/8-1/4), а не всястрока, поэтому нв; достатком данного устройства также является. низкое быстродействие.

Наиболее близким по технической суш

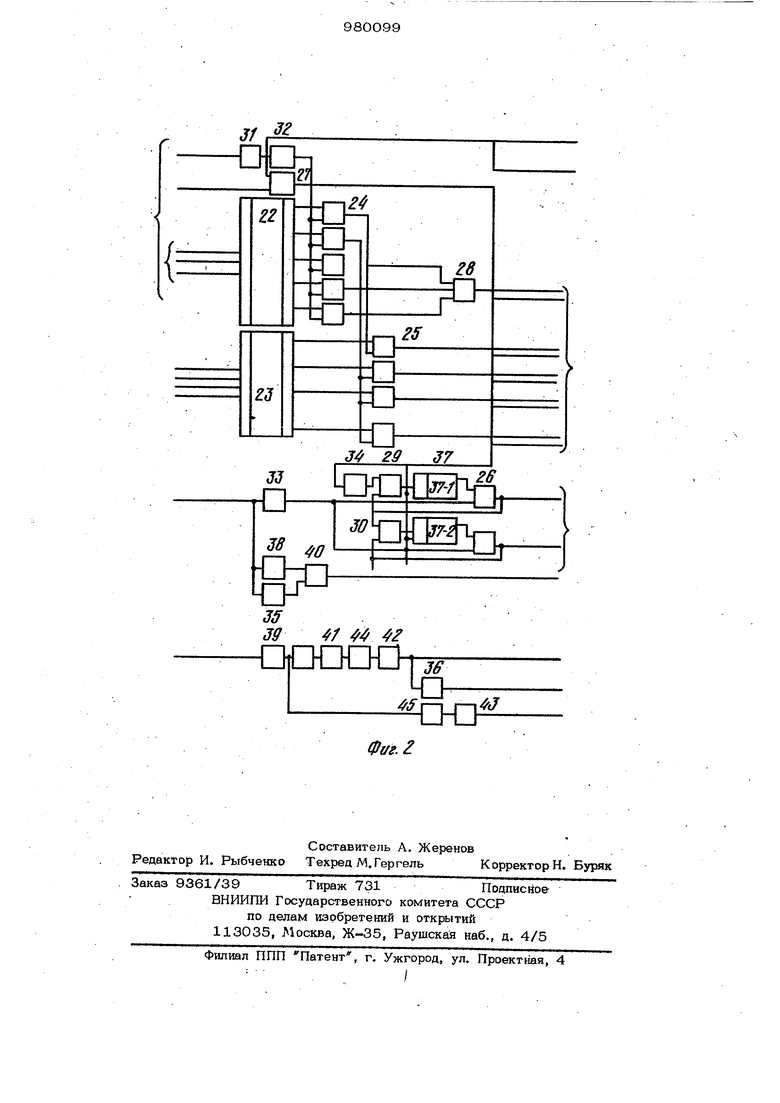

: нести к преалагаемому является устройство, которое содержит группу вхоанык регистров, группу выхоаных регистров, составляющих местную память, коммутатор, группу регистров ааресов записи в местную память, группу сумматоров аа;реса, регистр управляющих констант, сумматор констант и блок управления. При этом выход каждого входного pernci pa соепинен с соответствующим., инфор-, мационным входом коммутатора, информационные выходы коммутатор соепинены с вхопами соответствующих выходных регистров, выход каждого регистра адре-j са соёдвнен с первым входом соответствующеГо сумматора аареса, выхоа каж aofo сумматора аареса соецинен с соответствующим адресным входом коммутатора, выхоа регистра констант соеаинен с информационным вхоаом сумматора кон стант, информационный выхоа которого соеаинен с вторым входом каждого сум(Матора аареса, а управляющий выход с входом блока управления, первый, второй и третий выходы блока управления соединены соответственно с управляющи входом каждого сумматора адреса, управ ляющим вхоаом коммутатора и управляющим вхоаом сумматора констант. Устройство обменивается с памятью вычислительной системы строкой , содержащей слова (элементы) заданного формата и может работать в режимах Упаковка формуляров, Распаковка фор муляров, Упаковка слов, Распаковка слов, Перестановка,слов зJ. Описанное устройство имеет недостаточно высокое быстродействие в режимах Упаковка формуляров и Распаковка, формуляров из-за неполного использования возможностей основного оборудовани для обеспечения высокого быстродействия IB этих режимах. Действительно, в этих (режимах, так же как и в остальных, перед редактированием каждой стройн входной информации осуществляется модификация зааанных адресов записи ее слов в местную память на сумматорах апре- .сов, что связано с затратами времени. Этих затрат времени можно избежать, если операция редактирования Упаковка формуляторсю и Распаковка форМупя- ров выполнять не путем размещения сло каждой строки входной информации по за данным адресам местной памяти, а путем последовательного переписывания строк входной информации или содержащихся в вих формуляров в местную память и последующего чтения этой информации из местной памяти в таком порядке, который обеспечивает автоматическое редактирование. Однако такая возможность в данном устройстве не предусмотрена. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее регистры вывопа, ко1у1мутатор, V регистров адресов, Y сумматоров адресов, регистр констант, сумматор констант, блок управления и регистры ввода, входы которых являются соответственно информационными входами устройства, выход каж дого регистра ввода подключен к соответствующему информационному входу коммутатора, адресные входы устройства соединены соответственно с входами регистров адресов, выход каждого из которых соединен с первым входом соответствующего сумматора адресов, выход каждого из которых соединен с соответствующим адресным входом коммутатора, вход.регистра констант является вхоаом констант устройства, а выход подключен к первому входу сумматора констант, информационны.й выход которого соединен с вторым входом каждого сумматора адресов, управляющий выход сумматора констант соединен с первым входом блока управления, первый, второй и третий выходы которого соединены соответственно с управляющим входом каждого сумматоре адресов, с управляющим входом коммутатора и с управляющим входом сумматора констант, выходы регистров вывода являются информационными выходами устройства,второй,третий,четвертый и пятый входа блока управления являются соответственно управляющими входами устройства, шестой вход блока управления 5тляется вхо : дом .кода операции устройства, введены счетчик столбцов, дешифратор и коммутатор строк, информационные входы которого соединены соответственно с выходами коммутатора, выходы коммутатора строк соединены соответственно с информационными входами регистров вывода, первый и второй управляющие входы коммутатора строк соединень соответственно с управляющим выходом сумматора констант и четвертым выходом блока управления, пятый и шестой выходы которого соединены соответственно с управляющим вхо- аом дешифраторами входом счетчика стол- . бцов, выход которого подключен к информационному входу дешифратора, выходы дешифратора соединены соответственно с управляющими входами регистров вывода входы установки исходного состояния которых поаключены к седьмому выходу блока управления, восьмой выход которого является выходом запроса записи устройства. Кроме того, блок управления содержит элементы -И, ИЛИ, задержки, триггеры формирователи, прямоугольных импульсов, ограничители амплитупы, дифференцирующие элементы, генератор синусоидальных сигналов, элемеьт запрета, дешифратор кода операции и дешифратор констант, вход которого является первым входом блока,втррой вход блока соедики, выхоа которого подключен к.первому и третьему выходам блока, к входу второго элемента задержки и к первому вхо ду первого элемента ИЛИ, второй вход которого является третьим входом блока, выхоц второго элемента задержки подключен к первым входам элементов И первой группы, вторые входы которых со единены соответственно с выходами дешифратора кода операции, выход первого элемента И-первой группы соединены с первым входом первого элемента И второй группы, выход второго элемента И первой группы соединен с первыми входами элементов И, начиная со второго, второй группы, выходы элементов И, начиная с третьего, первой группы соединены соответственно с входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ и выходы элементов И второй группы явпяются вторы выходом блока, вторые входы элементов И второй группы соединены соответствен но с выходами дешифратора констант, че вертый вход блока соединен с входами третьего и четвертого элементов задержки и с входом первого формирователя прямоугольных импульсов, вход пятого элемента задержки соединен с выходом первого элемента ИЛИ, выход подключен к первому входу первого элемента ИЛИ группы, выход каждого элемента ИЛИ группы соединен со счетным входом соответствующего триггера, выходы триггеров подключены соответственно к первым ,входам элементов И третьей группы вторые входы которых соединены с выходом третьего элемента задержки, выход каждого элемента И третьей груп- пы соединен с вторым входом предыдущего и первым входом последующего элементов ИЛИ группы и с четвертым выходом блока, выходы первого формирователя прямоугольных импульсов и четвертого, элемента задержки соединены соответственно с входами элемента запрета, выход которого является восьмым выходом блока, установочные входы триггеров соединены с выходом первого элемента ИЛИ, вход второго формирователя прямоугольных импульсов является пятым входом блока, вЬ1Ход подключен к входам первого дифференцирующегоэле мента и генератора синусоидальных сигналов, выход которого через последовательно соединенные первый ограничитель амплитуды, второй дифференцирующий элемент и второй ограничитель амплиту- с входом шестого элемента задержки, выход которого является пятым выхоаом блока, выход первого дифференцирующего элемента через третий ограннчнтеиь амплитуды соединен с седьмым выходом На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема блока управления, Устройство включает регистры 1 вво fla, информационные входы 2 устройства, регистры 3 вывода, инфс мационные рыходы 4 устройства, регистры 5 адреров, сумматоры 6 адресов, регистр 7 констант, сумматор 8 констант, коммутатор 9, блок 1О управлений, адресные входы 11 устройства, вход 12 устройстеа, коммутатор 13 строк, счетчик 14 :столбцов, деишфратор 15, входы 16-2О устройства, выход 21 устройства, дешифратор 22 кода операции, дешифратор 23 констант, группы элементов И 24-26, элементы ИЛИ 27-ЗО, элементы задержки, триггеры 37, формирователи 38 и 39 прямоугольных импульсов, эле мент 4О запрета, ограничители 41-43 амплитуды, дифференцирующие элементы 44 и 45. Количество регистров 1, регистров 5 и сумматоров 6 равно у (где /Ц - количество слов заданного формата в строке информации, которой устройство обменивается с памят.ью вычислительной системы). Разрядность регистров 1 и 5 и сумматоров 6 ся1ределяется принятой в вычисга- тельной системе разрядностью одного слова. Совокупность регистров 3, составляющих местную память устройства,по информационной структуре представляет собой матрицу, имеющую YV строк и у столбцов. Элементом строки или столбца матрицы является один регистр, предназначенный для хранения одного слова. Запись редактируемой информации производится в те элементы, матрицы, которые выбраны коммутаторами 9 и 13 под воздействием на них сигналов строки заданных адресов записи с выходов сумматоров 6 адресов и управляющих сиг налов с выходов блока 1О управления. Чтение отредактированной информации для передачи ее в память вычислительной системы может производиться либо по строкам матрицы, либо по ее столбцам. В режимах Упаковка формуляров и Распаковка формуляров чтение производится

по столбцам путем последоватепьного перебора номеров столбцов с помощью счетчика 14 под воздействием на него управляющих сигналов с выхода блока 1О управления и выбора очередного столбца с помощью соответствующего выходного сигнала дешифратора 15, причем подаваемые на дешифратор 15 управляющие сигналы с выхода блока Ю управления предназначены для преобразования потенциальных выходных сигналов .дешифратора 15 в импульсные,

Коммутатор 9 служит дпя подключения к регистрам 1 любых регистров 3с адгресами, заданными в строке адресов

записи. Количество выходов коммутатора 9 равно количеству элементов матрицы. Коммутатор 9 используется во . всех (эежимах редактирования .

Коммутатор 13 предназначен для

замены выбранной Коммутатором 9 строки матрицы на -.другие строки Б режимах /Упаковка формуляров и Распаковка формуляров Количество информа- ционных входов коммутатора 13 равно количеству информационных выходов коммутатора 9.

Устройство для редактирования информации может работать в режимах Упаковка формуляров, Распаковка

формуляров, Упаковка слов, Распа.ковка слов, Перестановка слов,

В режиме -Упаковка формуляров , информация, подлежащая редактированию . за один шаг, представляет собой N стро где N - KorfkHecTBO элементов (слов) в одном формуляре, причем каждая строка содержит W1 элементов одного присущего только ей класса с различными порядковыми номерами, например:

(1-я строка)

«ч.а,

.«w, (2-я строка)

b-i, Ъ,--- , Ьт

(М-я строка) 5

. Sa..-. ОТ

m

Устройство -формирует из этих Ы строк подмассив, состоящий из гп формуляров, причем каждый, формуляр содержит ( N элементов, различнькс классов, но с одинаковыми номерами, т.е.

а. - формуляр)

1,0, - .5 (2-й формуляр)

.Я ..Я::::...

ат.Ъуп,.-,8Гт (vn-й формуляр) В режиме Упаковка формуляров |устройство работает cлeдyющи f образом.

По сигналу центрального процессора вычислительной системы из специальной ячейки оперативной памяти выбирается . строка адресов записи входной информации в регистры 3, содержащая адреса элементов только первой строки матрицы. Строка записи содержит также константу управления коммутатором 13, которая обозначает количество строк матрицы, по началам которых распределяется для записи одна строка входной информации. Для режима Упаковка формуляров эта константа равна . Адреса записи принимаются по адресным входам 11 в регистры 5 адреса, а управляющай константа - по входу 12 в регистр 7 констант. По сигналу Пуск из блока 10 управления, поступающему на ; управляющие входы сумматоров 6 адресов и сумматора 8 констант, адреса записи из регистров :5 адресов переписываются в сумматоры 6 адресов, а управня ющая константа из регистра 7 констант переписывается в сумматор 8 констант. Содержимое сумматоров 6 адресов и сумматора 8 констант в течение всех щагов редактирования остается неизменным. После этого ш шолняется первый шаг редактирования, в начале которого первая строка входной информации принимается в регистры 1,

По сигналу Редактирование, поступающему с выхода,блока 1О управления на управляющий вход коммутатора 9, последний подключает регистры 1 к своим входам, предназначенным для передачи информации в элементы первой строки матрицы. Коммутатор 13 строк под воздействии на его вход сигнала управляющей константы А 1 с выхода сумматора 8, а также под воздействием на управляющий вход сигнала Редактирование- (означающего редактирование первой строки входной информации) с выхода бпока 10 управления подключает к выходам коМ мутатора 9, обслуживающим первую строку матрицы, соответствующие элементы ее первой строки, в которьш переписывается первая строка входной информации,

После этого в регистры 1 принимается вторая строка входной .информации. С блока 10. управления сигнал Редактирование не подается (так как .он запоминается в коммутаторе 9 при обработке первой строки), а подается только сигнал Редактирование-2, под воздай- - ствием которого ксммутатор 13 строк подключает к выходам коммутатора 9, обслуживающим первую строку матрицы.

вместо соответствующих элементов первой строки матрицы аналогичные им эпе- менты второй строки матрицы, в которые переписывается вторая строка входной информации.Последующие строки входной информации принимаются в соответствующие строки матрицы точно так же.как и вто рая строка.

После запопнения строк матрицы строками входной информации блок 10 управпения формирует запрос на запись результатов первого шага редактирования в оперативную память вычислительной сие- , темы. При осуществлении этой записи чтение информации из матрицы устройств производится не по строкам, а ,по столбцам путем поспедовательного перебора номеров столбцов с помощью счетчика 14 по управляющим сигнгпам с выхода блока 10 управления, расшифровки этих номеров дешифратором 15 и выбора очередного столбца благодаря воздействию соответствующего выходного сигнала де.г шифратора 15 на входы регистров 3 этого столбца, управляющие выдачей информации. Преобразование потенциальных вы ходных сигналов дешифратора 15 в импульсные обеспечивается путем подачи на дешифратор 15 управляющих сигналов с выхода блока 1О управления. Чтение информации из матрицы по столбцам обес печивает автоматическое выполнение операции редактирования Упаковка формуляров.. На этом первый шаг редактирования заканчивается. Второй и последующие шаги редактирования выполняются аналогично, только с той разницей, что в начале каждого из этих шагов сигнал Редактирование не подается, так как он уже хранится в коммутаторе 9. о В режиме Распаковка формуляров информация, подлежащая редактирова П1Ю за один шаг, представляет собой W стро где К1 - количество элементов (слов) в одном формуляре, причем каждая строка содержит Vvi элементов, которые разделе ны на До формуляров, т.е. . Устройство формирует из этих М стро подмассив, состоящий также из N строк, причем каждая строка содержит Wi элементов одного, присущего только ей класса. В режиме Распаковка формуляров устройство работает следующим образом. По сигналу центрального процессора вычислительной системы из специальной ячейки оперативной памяти выбирается строка адресов записи информации в регистры 3, содержащая адреса N левых элементов для каждой из строк матрицы с номерами 1,2,...,АО- Строка адресов записи содержит также константу управления коммутатором 13 строк, обозначающую количество строк матрицы, по началам которых распределяется для записи одна строка входной информации. Для режима Распаковка формуляров эта константа равна количеству формуляров в одной строке входной информации, т.е. АО 1 Адреса записи принимаются по адресным входам 11 в регистры 5 адресов, а управляющая константа - по входу 12 в регистр 7 констант. По сиг налу Пуск на блоке 10 управления, поступающему на управляющие входы сум:маторов 6 адресов и сумматора 8, адреса записи из регистров 5 адресов переписы.ваются в сумматоры 6 адресов, а ynpai ляющая константа из регистра 7 переписывается в сумматор 8. Содержимое сумматоров 6 адресов и сумматора 8 кон- стант в течение всех шагов редактирования остается неизменным. После этого выполняется первый шаг редактирования, в начале которого первая строка входной информации принимается в регистры 1. По сигналу Редактирование , поступающему с выхода блока 10 управления i на управляющий вход коммутатора 9, последний подключает регистры 1 к своим входам, предназначенным для передачи информации в группы Ы левых элементов, принадлежащие строкам матрицы с номерами 1,2,..., Ар. Коммутатор 13 под воздействием на его управляющий вход сигнала управляющей константы АО с выхода сумматора 8 констант, а также под воздействием на его другой вход сипнала Редактирование (означающего редактирование первой строки входной информации) с выхода блока 10 управления подключает к выходам коммутат ра 9, обслуживающим группы N левых элементов, принадлежащие строкам матрицы с номерами 1,2,.-.,Ао соответствующие элементы этих строк так, что из первой строки входной информации первый формуляр переписывается в N левых элементов первой строки матрицы, второй форму ляр-в левых эпементов второй строки матрицы,и т.д;,формуляр с номерами Ар в К левых элементов строки матрицы с номером АОПосле этого в регистры 1 принимает ся вторая строка входной информации. С блока 10 управления сигнал Редактирование не подается (так как он запомина/ется в каммутйтурв 9 при . обработке первой строки), а подается только сигнал Редактирование-2, под воздействием которого коммутатор 13 строк подключает к )илходам ксммутатора 9, обслуживающим грушпы левых элементов, принадлежащие строкам i матрицы с номерами 1,2,..., АО , вместо этих элементов аналогичные им элементы, принадлежащие строкам матрицы с номерами AQ+I ,Ао.-2,...,2 До в которые из второй строки входной ин.формаиии -переписываются «формуляры с , номерами А о Досоответственво. Из последующих строк входной информации формуляры переписываются в груп пы Ы левых элементов соответствую- , строк матрицы точно так ж, как из |Второй строки. После заполнения: в. каждой, из Hi строк матрицы N левых элементов, соответству ющих - очередному формуляру, блок 1О yitравления формирует запрос на запись ре- зультатов редактирования в оперативную память вычислительной системы. При осуществлении этой записи чтение информации из матрицы производится .по столбцам так же, как и в режиме Упаковка формуляров. Это обеспечивает автомати ческое выполнение операции редактирования Распаковка формуляров. На атом первый шаг редактирования заканчивается Второй в последующие шаги редакт1 рования выполняются аналогично, только с той разницей, что в начале каждого из этих шагов сигнал Редактирование не подается, так как он уже хранится в коммутаторе 9.. ..гхг Работа устройства в режимах Упаковслов (выделение в массиве заданных слов и их размещение в памяти без промежутков между ними с сохранением порядка следования), Распаковка Слов (размещение слов массива по заданным адресам памяти с промежутками и с сохранением порядка следова1В Ия) и Перестановка слов (изменение порядка следования слов в массиве) Iфoиckoдит по.средством размещения слов каждой строки входной информации по заданным адресам с помощью коммутатора 9 (коммутатор 13 строк не используется). Адреса задаются в строках адресов записи, принимаемь1х регистрами 5 адресов, и перед обработкой каждой очередной строки входной информации модифицируются на сумматорах 6 адресов путем сложения с. константой модификации адресов, теку66612 щее значение -которой формируется сумматором 8 констант из значения управпяющей константы, принимаемой регистром 7 констант. Текущим значением конст йты модификации адресов в режиме Упа: ковка слов является общее количество p«tHee упакованных слов, в режиме Распаковка слов - общее количество ранее занятых адресов (с учетом промежуточных не занятых адресов), а в режиме Перестановка слов - общее количество слов в ранее обработанных строках входной информации. Чтение отредактированной и формации из матрицы производится по строкам. Блок управления содержит узел пуска и управления коммутатором, узел управления коммутатором строк и выдачи запроса на запись в оперативное запомина:ющее устройство иузел управления мат .ридей местной памяти, Узел пуска и управления коммутатором предназначен для выработки управляющих сигналов Пуск, подаваемых на сумматор адреса и на сумматор констант, а.также управляющих сигналов Редакти- рование, подаваемых на коммутатор, По сигналу от центрального процессора Начать редактирование (импульсный сигналУформируется сигнал Пуск с запаздыванием, которое определяется временем задержки элемента 31 задержки. После этого по сигналу от центрального процессора Код операции редактирования (потенциальный ..параллельный трехразрядный код) происходит дешифрация кода операции редактирования (со значением из набора 1,2,3,4,5) и затем с йогмощью сигнала Пуск, задержанного по времени элементом 32 задержки, - формгтппят,.. ,,.,v ..««rrr, мирование импульснь1х сигналов Редактирование. Сигнал Редактирование для режимов Упаковка слов, Распаковка слов и f Перестановка слов формируется одина ково. Сигналы Редактирование для режимов Упаксюка формуляров (при зна ченин ухфавляющей константы А 1) и Распаковка формуляров (при значениях управляющей константы АО из набора 2,3,415) формируются с использованием деши4Ч)атора 23 констант, работающего под воздействием сигнала управляющей константы от сумматора констант. Сигнал Редактирование для любого режима подается в коммутатор на соответствующий триггер,, где хранится в те.. чение всех шагов редактирования в данном режиме. Предварительная установка этого триггера в исходное нулевое состояние производится сигналом Пуск, а сброс по окончании всех шагов редактирования сигналом от центрального процессора Закончить редактирование (импульсный сигнал), поступающим на вход элемента. Узел управления коммутатором строк и выдачи запроса на запись в оператив-. ное запоминающее устройство (ОЗУ) предназначен для выработки управляющих сигналов Редактирование- , Редактирование-2, Редактирование-З и т.д., подаваемых на коммутатор строк для обеспеч ния редактирования 1-й, 2-и, 3-й и т.д. строк входной информации в. режимах Упаковка формуляров и Распаковка форт луляров. Кроме того, он формирует управляющий сигнал Заппос на запись в ОЗУ на наибольшее возможное количеотво строк входной информации, подлежащи редактированию за один щаг. По сигналу Пуск.триггеры 37 устанавливаются в исходное нулевое состояни По сигналу Пуск, задержанному по времени элементом 34 задержки, триггер 37-1 устанавливается в единичное соотояние и тем самым подготавливает к срабатыванию элемент И, подключенный к его единичному выходу. По сигналу приема первой строки входной информации в регистры 1, поступающему от центрального процессора и задержанному по времени элементом 33 задержки, на выходе указанного элемента И, т.е. на одной из шин четвертого выхода, образуется импульсй 1й сигнал Редактирование-1. Триггер 37-2 при формирований сигнала Редактирование-2 работает аналогично триггеру 37-1 с той лишь раэ{щцей, что роль пускового сигнала для триггера 37-2 выполняет сигнал Редактирование-, а сигнал Редактирование2 формируется с помощью сигнала при ема второй строки входной информации. Аналогично работают и остальные тригге ры, не показанные на фиг. 2. Принцип действия цепи формирования сигнала запроса на запись в ОЗУ состоит в том, что каждый импульс приема очередной строки сам готовит себя к выдаче в качестве запросного в случае, если за данным импульсом не подается последук щий.. Это обеспечивается -подачей импульса приема строки, задержанного на перио следования этих импульсов элементом 35 |3адержки, на основной вход элемента 4О запрета и расширенного последующего импульса на запрещающий вход этого элемента. Узел управления матрицей местной памяти предназначен для выработки управляющих сигналов счета номеров столбцов и выбора столбцов матрицы, а также управляющего сигнала сброса матрицы после переписывания содержимого всех ее столбцов в оперативное запоминак щее устройство в конце шага редактирова-г ния. По сигналу Ответ от центрального процессора узел формирует на шестом выходе последовательность импульсов, количество которых равно количеству столбцов матрицы, а на пятом выходе блока, такую же последовательность, задержанную по времени элементом 36 задержки. Импульс сброса матрицы формируется путем дифференцирования спада выходного импульса формирователя 39 и последук щего ограничения. Предлагаемое устройство для редактирования информации, обеспечивает по сравнению с известным более высокое быстродействие в режимах Упаковка формуляров и Распаковка формуляров. Это обусловлено тем, что данные операции редактирования выполняются не путем размещения слов каждой строки входной информации по заданным адресам местной памяти, а путем последовательного пер&писывания строк входной информации или содержащихся в них формуляров в строки элементов матрицы местной памяти в последующего чтения информации из столбцов элементов этой матрицы. При этом перед переписыванием каждой строки входной информации в местную память модификация адресов записи слов этой строки на сумматорах адресов не производится, что уменьшает время, затрачиваемое на редактирование одной строки. Действительно, в известном устройстве модификация адресов записи слов очередной строки входной информации на сумматорах адреса начинается одновре менно с приемом этой строки во входные регистры. Однако сложение адресов запасе с константой их модификации с помощью сумматоров накапливающего типа за-, нимает больше врземени, чем прием очередной строки во входнь1е регистры. Поэтому сигнал редактирования данной стрюки из блока управления на управляющий вход коммутатора 9 может быть подан только после окончания этого сложения. В предлагаемом устройстве в режимах паковка форялуляров и Распаковка формуляров модификация адресов записи слов очередной строки входной информации и© производится, поэтому сигнал .редактирования данной строки из блока управления на управляющий вход коммутатора 13 строк может быть подан сразу после окон чания ее приема в регистры 1. Сокращен ние времени выполнения одного шага ре. дактирования по сравнению с известным устройством достигается за счет того, что в одном шаге редактируются несколья ко строк входной информации. Формула изобретения 1. Устройство для редактирования информации, содержащее регистры вывода, коммутатор, И. регистров адресов, И сумматоров адресов, регистр констант сумматор констант, блок уп1 авления и ре гистры ввода, . входы которых являются со ответственно информ&пионными входами ,устройства, вь1ход каждого регистра ввода подключен к соответствующему информационному входу коммутатора, адрес ные входы устройства соединены соответственно с входами регистров адресов, выход каждого из которых соединен с первым входом соответствующего сумма тора адресов, выход каждого из.которых соединен с соответствующим адресшз1м входом коммутатора, вход регистра констант является входом констант устройства, а выход подключен, к первому входу сумматора констант, информационный выход которого соединен с вторым входом каждого сумматора адресов, управляюЕщй выход сумматора констант соединен с первым входом блока управления, первый, второй и третий выходы которого соединены соответственно с управляющим входом каждого сумматора адресов, с управляющга д входом коммутатора и с управляющим входом сумматора констант выходы регистров вывода являются информационными выходами устройства, второй, третий, четвертый и пятый входы блока управления являются соответствен но управляющими входами устройства, щестой вход блока управления является вход см кода операции устройства, о т. личающееся теМ, что, с целью повышения быстродействия устройства, в него введены счетчик столбцов, дешифратор и коммутатор строк, инфо1Ж1аци онные входы которого соединены соответственно с выходами коммутатора, вы- .ходы коммутатора строк соединены соответственно с информационными входами регистров вывода, первый и второй управляющие входы ксммутатора строк соединены соответственно с улравляк щим выходом сумматора констант и четвертым выходом блока управления, пятый и шестой выходы которого соединены соответственно с управляющим входом дешифратора и входом счетчика столбцов, выход которого подключен к информационному входу дешифратора, выходы дешифратора соединены соответственно с управляющими входами регистров вывода, входы, установки исходного состояния которых подключены к седьмому выходу блока управления, восьмой выход котор1 го является выходом запроса записи устройства. 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок управления содержит элементы И, ИЛИ, задержки, триггеры формирователи прямоугольных импульсов, ограничители амплитуды, диф-. ференцирующие элементы, генератор ci нусоидальных сигналов, элемент запрета, дешифратор кода операции и дешифратор констант, вход которого является первым входом блока, второй вход блока соединен с входом первого элемента задерж- ки, выход которого подклю 1ен к первому и третьему выходам блока, к входу второго элемента задержки и к первому входу первого элемента ИЛИ, второй вход которого Я1зляется третьим входом блока, выход второго элемента задержки пр®клк чен к первым входам элементов И первой группы, вторые входы которых соединены соответственно с выходами дешифра -ора кода операции, выход первого элемента И первой группы соединеи с первым вхо дом первого элемента И второй группы, выход второго элемента И первой группы соединен с первыми входами элементов И, начиная со вторЬго, второй группы, выходы элементов И, нвчиная с третьего, первой группы соедвнены соответственно с входами второго элемента ИЛИ, выходы первого и второго элементов ИЛИ и вы:. ходы элементов И второй группы являются BTopwirf вь1ходом блока, вторые входы элементов И второй группы соединены соответственно с выходами дешифратора коистант, четвертый вход блока соединен с входами третьего и четвертого элементов задержки и с вход сы первого формирователя прямоугольных импульсов, вход пятого элемента задержки соединен с выходом первого элемента ИЛИ, выход подключен к первому входу первого эпемента ИЛИ группы, выход каждого элемента ИЛИ группы соединен со счет ным входом соответствующего триггера, выходы триггеров подключены соответственно к первым входам элементов И третьей группы, вторые входы KOTOE IX соединены с выходом третьего элем1знта задержки, выход каждого элемента И третьей группы соединен с вторым входом предыдущего и первым 1входом последующего элементов ИЛИ группы и с четвертым выходом блока, выходы первого формирователя прямоугольных импульсов и четвертого элемента задержки соединены соответственно с входами элемент запрета, выход которого является восьмым выходом блсжа, установочные входы триггеров соединены с выходом первого элемента ИЛИ, вход второго формировате ля прямоугольных импульсов является пя тым входом блока, выход подключен к входам первого дифференцирующего элемента и генератора синусоидальных налов, выход которого через последовательно соединенные первый огравшчигель амплитуды, второй дифференцирующий элемент и второй ограшиитель амплитуды соединен с щестым выходом блока и с входом шестого элемента задержки, выход которого является пятым выходом блока, выход первого дифференцирующего элемента через третий ограничитель амплитуды соединен с седьмым выходом бпог Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 524177, кл. Q 06 F 3/14, 1974. 2.Белков М.С., Братальский Е.А., Крупский А. А. Устройство редактирования информации. - Вотросы радиоэлектроники, сер. Электронная вычислительная техника , М., 1976, вып. 8, с. 69-74. 3.Авторское свидетельство СССР № 805297, кл. Q 06 Р 3/14, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

Фаг. г

Авторы

Даты

1982-12-07—Публикация

1981-04-08—Подача