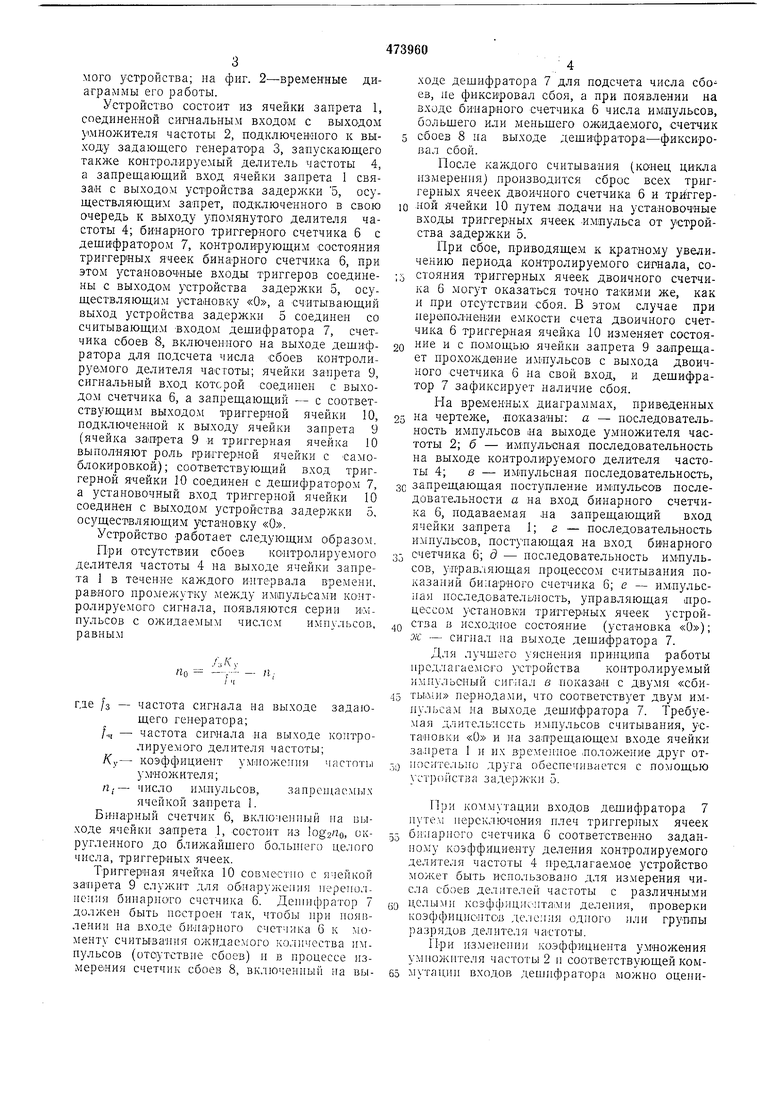

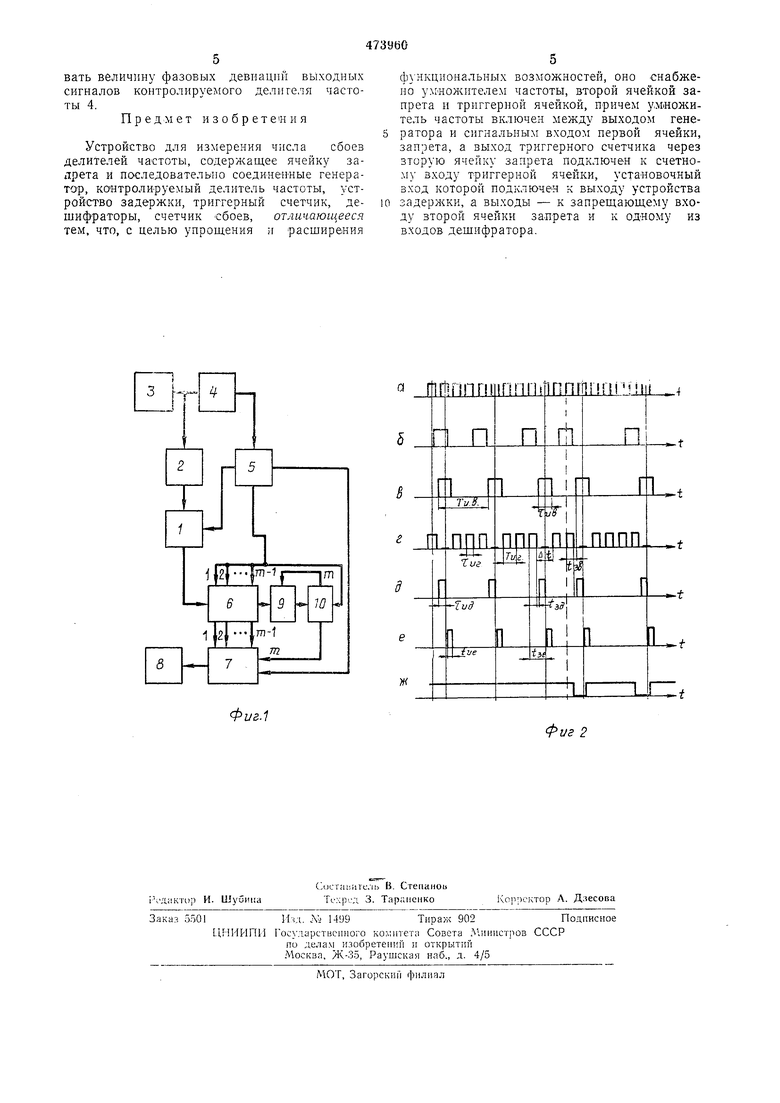

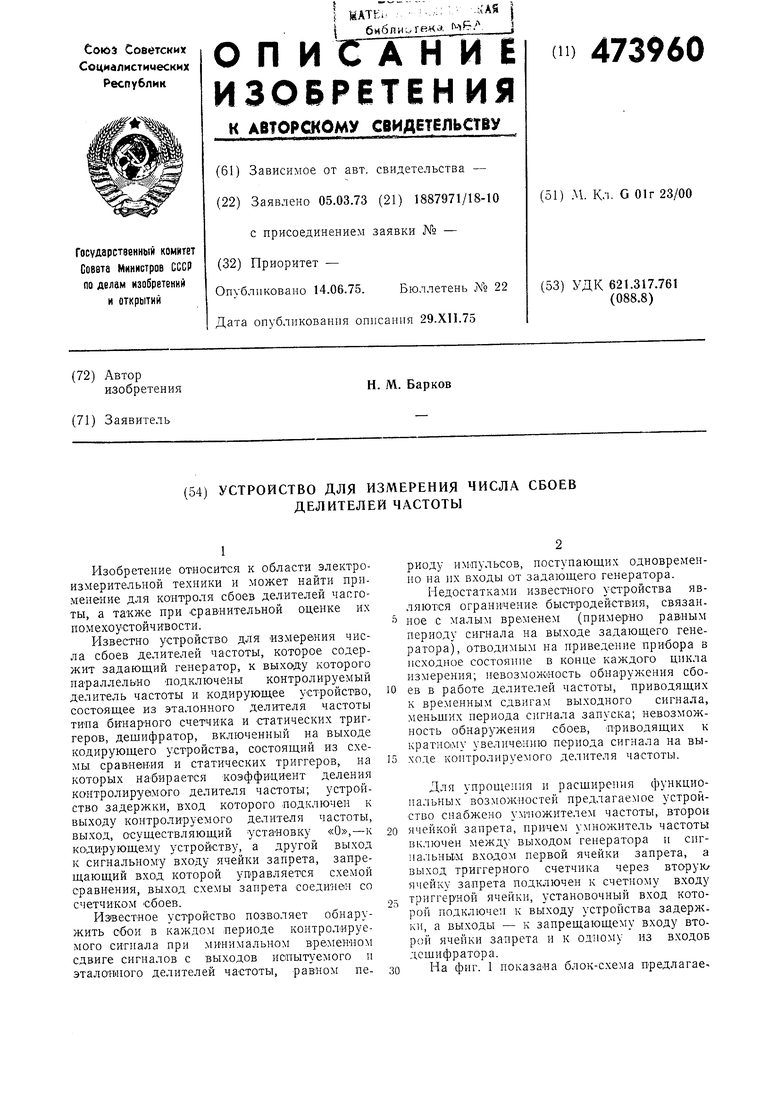

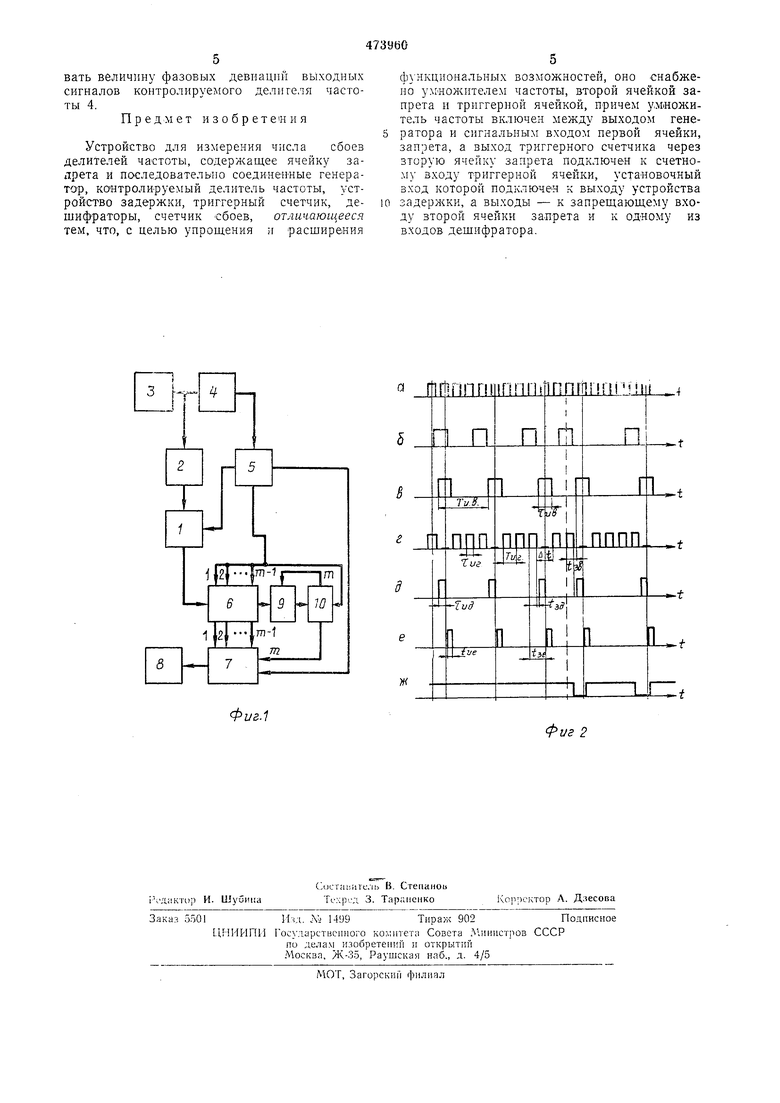

мого устройства; на фиг. 2-временные диаграммы его работы. Устройство состоит из ячейки запрета 1, соединенной сигнальным входом с выходом умножителя частоты 2, подключен1пого к выходу задающего генератора 3, запускающего также контролируемый делитель частоты 4, а запрещающий вход ячейки запрета 1 связан с выходом устройства задержки 5, осуществляющим запрет, подключенного в свою очередь к выходу упомянутого делителя частоты 4; бинарного триггерного счетчика 6 с дещифратором 7, контролирующим состояния триггерных ячеек бинарного счетчика 6, при этом установочные входы триггеров соединены с выходом устройства задержки 5, осуществляющим установку «О, а сч итывающий выход устройства задержки 5 соединен со считывающим входом дещифратора 7, счетчика сбоев 8, включенного на выходе дешифратора для подсчета числа сбоев контролируемого делителя частоты; ячейки запрета 9, сигна.тьный вход которой соединен с выходом счетчика 6, а запрещающий - с соответствующим выходом триггерной ячейки 10, подключенной к выходу ячейки запрета 9 (ячейка заярета 9 и триггерная ячейка 10 выполняют роль грштерной ячейки с самоблокировкой); соответствующий вход триггерной ячейки 10 соединен с дешифратором 7, а установочный вход триггерной ячейки 10 соединен с выходом устройства задержки 5, осуществляющим установку «О. Устройство работает следующим о-бразом. При отсутствии сбоев контролируемого делителя частоты 4 на выходе ячейки запрета 1 в течение каждого интервала времени, равного промежутку между имиульсами контролируемого сигнала, появляются серии вмпульсов с ожидаемым числом импульсов, равным По -,- - П; Ч где /3 - частота сигнала на выходе задающего генератора; /„1 - частота сигнала на выходе контролируемого делителя частоты; Ку- коэффициент умаюжеиия частоты умножителя; П;- число импульсов, запрещаемых ячейкой запрета 1. Бинарный счетчик 6, включенный па выходе ячейки запрета 1, состоит из Iog2no, округленного до ближайщего больи его целого числа, триггерных ячеек. Триггерная ячейка 10 совместно с ячейкой запрета 9 служит для обнаружения переполнения бинарного счетчика 6. Дешифратор 7 должен быть построен так, чтобы при появлении на входе бинарного счетчика G к моменту считывания ожидаемого количества импульсов (отсутствие сбоев) н в процессе измерения счетчик сбоев 8, включенный на выходе дещпфратора 7 для подсчета числа сбоев, не фиксировал сбоя, а при появлении на входе бинариого счетчика 6 числа импульсов, большего или меньшего ожидаемого, счетчик сбоев 8 на выходе дещифратора-фиксировал сбой. После каждого считывания (канец цикла измерения) производится сброс всех триггерных ячеек двоичного счетчика 6 и трйггерной ячейки 10 путем подачи на установочные входы триггерных ячеек импульса от устройства задержки 5. При сбое, приводящем к кратному увеличению периода контролируемого сигнала, состояния триггерных ячеек двоичного счетчика 6 могут оказаться точно та-кими же, как и при отсутствии сбоя. В этом Cviy4ae при переполнении емкости счета двоичного счетчика 6 триггерная ячейка 10 изменяет состояние и с помощью ячейки запрета 9 залрещает прохождение импульсов с выхода двоичного счетчика 6 на свой вход, и дешифратор 7 зафиксирует наличие сбоя. На временных диаграммах, приведенных на чертеже, показаны: а - последовательность и.мпульсов на выходе у.миожителя частоты 2; б - импульсная последовательность на выходе контролируемого делителя частоты 4; в - импульсная последовательность, запрещающая поступление импульсов последовательности а иа вход бинарного счетчика 6, подаваемая на запрещающий вход ячейки запрета 1; г - последовательность импульсов, поступающая на вход бинарного счетчика 6; д - последовательность импульсов, управляющая процессом считывания показаний бинарного счетчика 6; е - импульспая последовательность, управляющая .процессом установки триггерных ячеек устройства в исходное состояние (установка «О); ж - сигнал на выходе дещифратора 7. Для лучшего уяснения принципа работы предлагаемого устройства контролируемый импульсный сигнал в показан с двумя «сбиTbiiMH периодами, что соответствует двум импульсам на выходе дещифратора 7. Требуемая длительность импульсов считывания, установки «О и на запрещающем входе ячейки запрета 1 и их временное положение друг отиосительно друга обеспечивается с помощью ycTpiuiCTua задержки 5. При коммутации входов дешифратора 7 путем переключения плеч триггерных ячеек бинарного счетчика 6 соответственно заданному коэффициенту деления контролируемого делителя частоты 4 предлагаемое устройство может быть испо.чьзовано для измерения числа сбоев делителей частоты с различными целыми коэффиц; игга1ми деления, проверки коэффициснтСВ де.1е:1.:1я одного или группы разрядов делителя чаСтоты. При изменении коэффициеита умножения умножителя частоты 2 и соответствующей коммутации входов дешифратора можио оценивать величину фазовых девиаций выходных сигналов контролируемого дели геля частоты 4.

Предмет изобретения

Устройство для измерения числа сбоев делителей частоты, содержащее ячейку залрета и последовательно соединен«ые генератор, контролируемый делитель частоты, устройство задержки, триггерный счетчик, дешифраторы, счетчик сбоев, отличающееся тем, что, с целью упрощения и расширения

функциональных возможностей, оно снабжеио уМНожителем частоты, второй ячейкой запрета и триггерной ячейкой, причем улшожитель частоты включен между выходом генератора и сигнальным входом первой ячейки, запрета, а выход триггерного счетчика через вторую ячейку запрета подключен к счетно.му входу триггерной ячейки, установочный вход которой подключен к выходу устройства задержки, а выходы - к запрещающему входу второй ячейки запрета и к одному из входов дещифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕРПОЛЯТОР | 1970 |

|

SU272415A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| ВИБЛИОТЕКД J | 1971 |

|

SU299030A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Линейно-круговой интерполятор | 1974 |

|

SU500518A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1383449A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ФЕРРИТОВЫХ МАТРИЦ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1973 |

|

SU364030A1 |

Фиг 2

Авторы

Даты

1975-06-15—Публикация

1973-03-05—Подача