I

Изобретение относится к области запоминающих устройств.

Известно устройство для проверки ферритовых матриц оперативных запоминающих устройств, содержащее регистр адреса, нодсоединенный к блоку дещифраторов, выход которого подключен к блоку формирователей импульсов тока, блок считывания и контроля, подсоединенный к блоку управления, состоящему из схемы однократного цикла проверки ферритовых сердечников матрицы, генератора импульсов и схемы временной последовательности импульсов.

Предложенное устройство отличается от известного тем, что в него введен триггерный регистр количества дефектов, установочные входы которого соединены с первым выходом схемы временной задержки. Вход схемы подсоединен к выходу схемы однократного цикла проверки ферритовых сердечников матрицы, а второй выход этой схемы временной задержки - к первому входу схемы «И, второй вход которой подключен к генератору нмпульсов, а выход -к схеме временной последовательности импульсов.

Это позволяет повысить быстродейств1 е устройства.

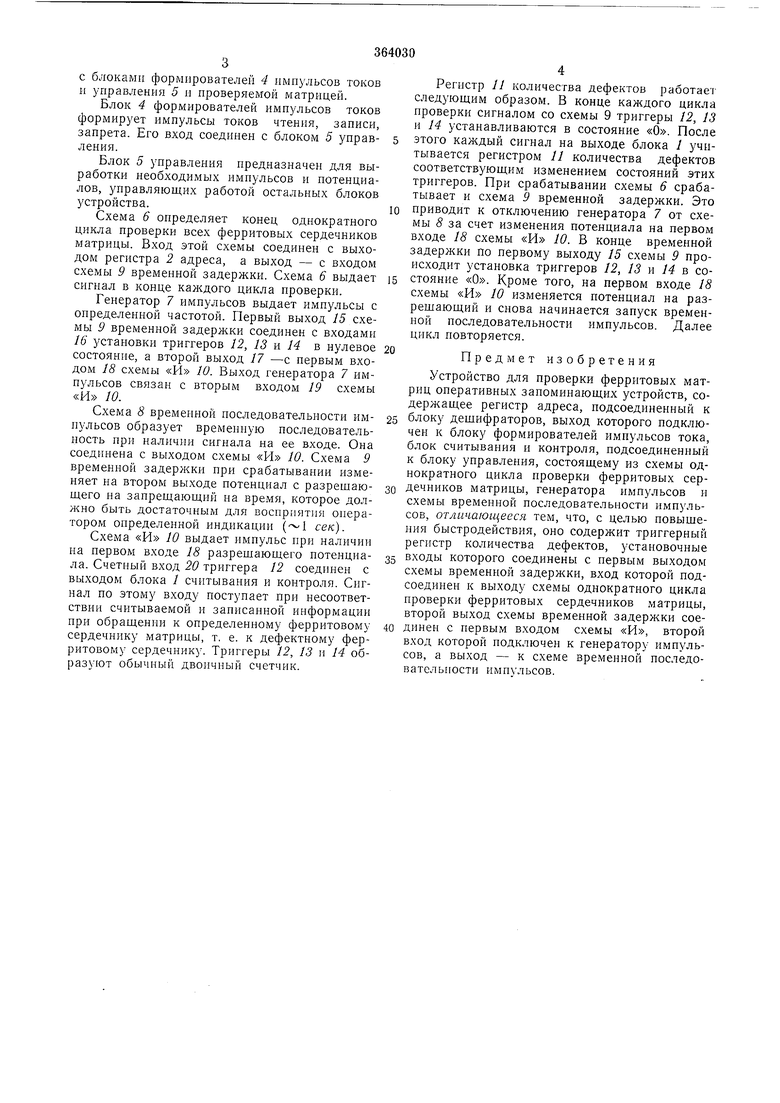

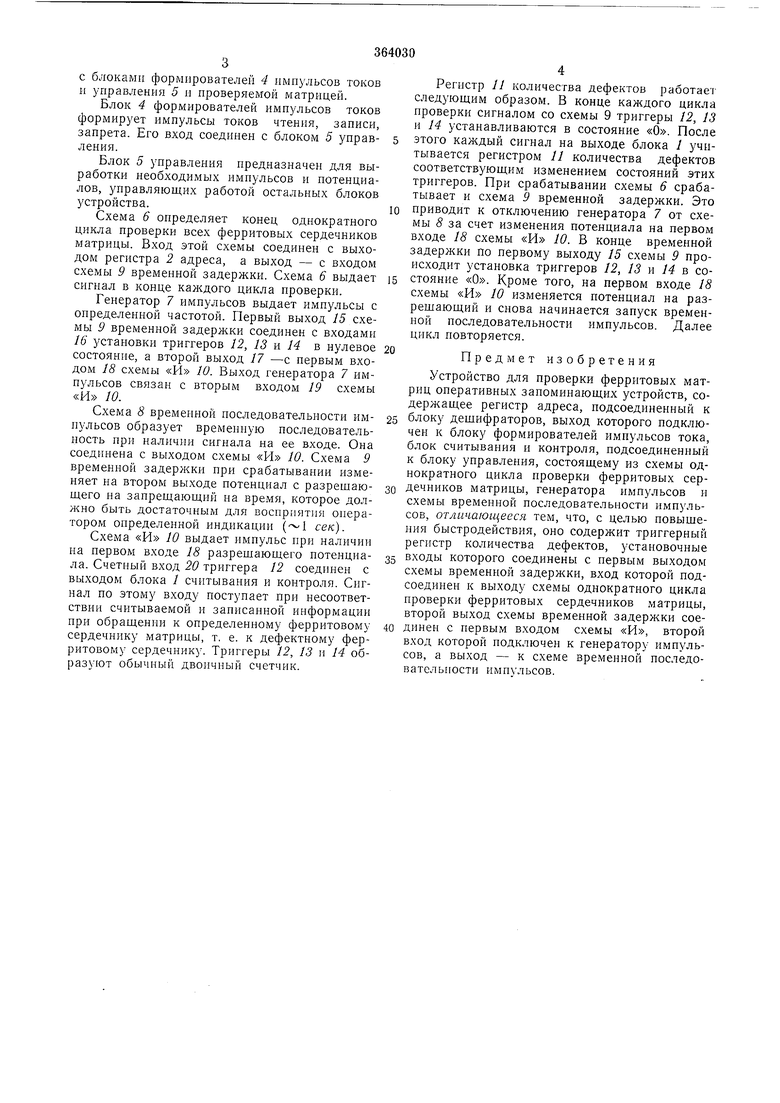

На чертеже показана блок-схема устройства для проверки ферритовых матриц оперативных запоминающих устройств.

Устройство содержит блок 1 считывания п контроля; регистр 2 адреса; блок 3 дешифраторов; блок 4 формирователей нмпульсов токов; блок 5 унравления, в который входят схема 6 однократного цикла проверки ферритовых сердечников матрицы, генератор 7 импульсов, схема 8 временной последовательности импульсов; схему 9 временной задержки; схему «И 10 и регистр }} количества дефектов, состоящий из триггеров 12, 13 и 14.

Блок 1 считывания и контроля предназначен для усиления сигналов с ферритовых сердечников матрицы до стандартного уровня н контроля соответствня счнтываемой и записанной информации. Он соедииен с обмотками считывания нроверяемой матрицы и блоком 5 управления (соединение с проверяемой матрицей и сама матрица на чертеже не показаны).

Регнстр 2 адреса, предусмотренный для последовательного выбора всех обмоток двух координат матрицы, представляет собой ряд триггеров, работающих в режиме счетчика. Он соединен с блоками дешифраторов 3 и управления 5.

Блок 3 дешифраторов служит для преобразования потенциалов триггеров регистра адреса в имиульсы возбуждеиия соответствующих токовых ключе, с иомощь о которых осуидествляется выбор определенной обмотки данной координаты матрицы. Блок 3 соединен с блоками формирователей 4 импульсов токов и управления 5 п проверяемой матрицей. Блок 4 формирователей импульсов токов формирует импульсы токов чтения, записи, запрета. Его вход соединен с блоком 5 управБлок 5 управления предназначен для выработки необходимых импульсов и потенциалов, управляющих работой остальных блоков устройства. Схема 6 определяет конец однократного цикла проверки всех ферритовых сердечников матрицы. Вход этой схемы соединен с выходом регистра 2 адреса, а выход - с входом схемы 9 временной задержки. Схема 6 выдает сигнал в конце каждого цикла проверки. Генератор 7 импульсов выдает импульсы с определенной частотой. Первый выход 15 схемы 9 временной задержки соединен с входами 16 установки триггеров 12, 13 и 14 в нулевое состояние, а второй выход 17 -с первым входом 18 схемы «И 10. Выход генератора 7 имнульсов связан с вторым входом 19 схемы «И 10. Схема 8 временной последовательности имиульсов образует времениую последовательность при наличии сигнала на ее входе. Она соединена с выходом схемы «И 10. Схема 9 временной задержки при срабатывании изменяет на втором выходе потенциал с разрещаю- зо щего на запрещающий на время, которое должно быть достаточным для воспр11ят 1я оператором определенной индикации (1 сек. Схема «И 10 выдает импульс при наличии на первом входе 18 разрешающего потенциа- 35 ла. Счетный вход 20 триггера 12 соединен с выходом блока / считывания и контроля. Сигнал по этому входу поступает при несоответствии считываемой и записанной информации при обращении к определенному ферритовому 40 сердечнику матрицы, т. е. к дефектному ферритовому сердечнику. Триггеры 12, 13 и 14 образуют обычный двоичный счетчик. Регистр 11 количества дефектов работает следующим образом. В конце каждого цикла проверки сигналом со схемы 9 триггеры 12, 13 и 14 устанавливаются в состояние «О. После этого каждый сигнал на выходе блока / учитывается регистром 11 количества дефектов соответствующим изменением состояний этих триггеров. При срабатывании схемы 6 срабатывает и схема 9 временной задержки. Это приводит к отключению генератора 7 от схемы 8 за счет изменения потенциала на первом входе 18 схемы «И 10. В конце временной задержки по первому выходу 15 схемы 9 происходит установка триггеров 12, 13 и 14 в состояние «О. Кроме того, на первом входе 18 схемы «И 10 изменяется потенциал на разрещающий и снова начинается запуск временной последовательности импульсов. Далее цикл повторяется. Предмет изобретения Устройство для проверки ферритовых матриц оперативных запоминающих устройств, содержащее регистр адреса, подсоединенный к блоку дещифраторов, выход которого подключей к блоку формирователей импульсов тока, блок считывания и контроля, подсоединенный к блоку управления, состоящему из схемы однократного цикла проверки ферритовых сердечников матрицы, генератора импульсов схемы временной последовательности импульсов, отличающееся тем, что, с целью повышения быстродействия, оно содержит триггерный регистр количества дефектов, установочные входы которого соединены с первым выходом схемы временной задержки, вход которой подсоединен к выходу схемы однократного цикла проверки ферритовых сердечников матрицы, второй выход схемы временной задержки соединен с первым входом схемы «И, второй вход которой подключен к генератору импульсов, а выход - к схеме времеиной последовательности импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1981 |

|

SU963110A1 |

| Устройство для контроля ферритовых сердечников запоминающих матриц | 1984 |

|

SU1280460A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| Устройсто для проверки ферритовых матриц | 1974 |

|

SU548893A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1968 |

|

SU211156A1 |

| Устройство для контроля запоминающих матриц на магнитных пленках | 1979 |

|

SU773736A1 |

| УСТРОЙСТВО для ПРОВЕРКИ ФЕРРИТОВЫХ МАТРИЦ | 1973 |

|

SU376813A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля матриц на ферритовых сердечниках | 1977 |

|

SU658601A1 |

Авторы

Даты

1973-01-01—Публикация