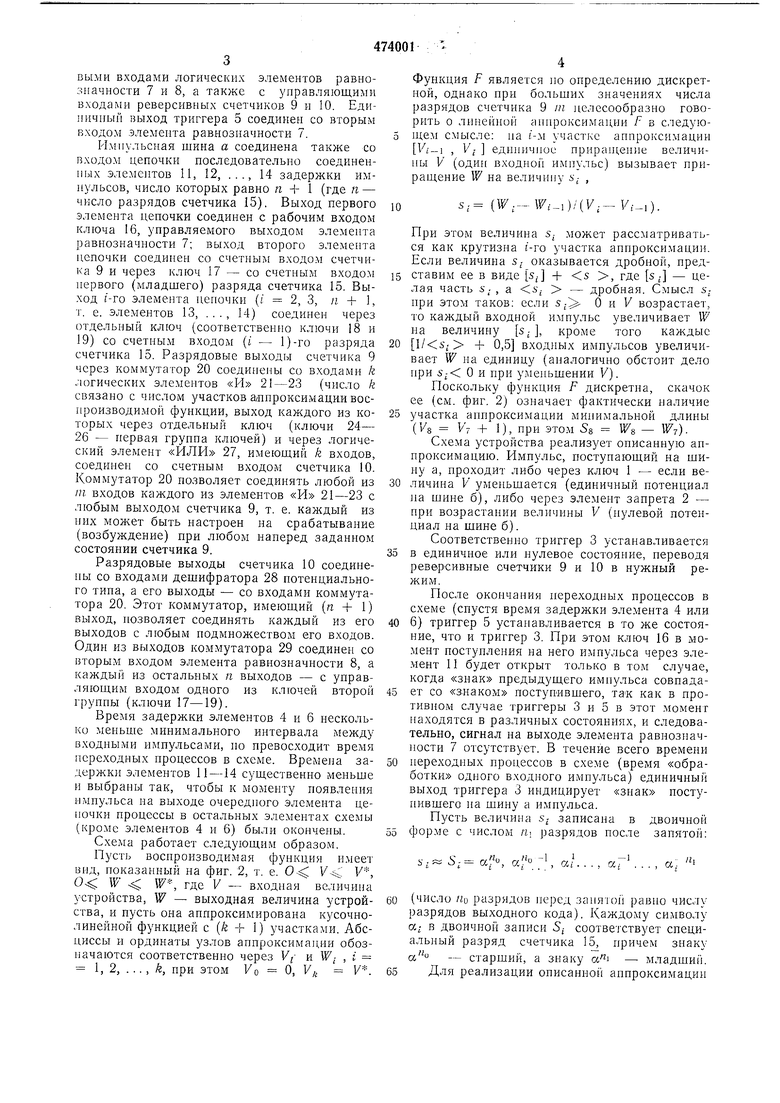

выми входами логических элементов равнозначности 7 и 8, а также с унравляющими входами реверсивных счетчиков 9 и 10. Единичный выход триггера 5 соединен со вторым входом элемента равнозиачиости 7.

Импульсная шина а соединена также со входом цепочки иоследовательно соединенных элементов 11, 12, ..., 14 задержки имнульсов, число которых равно п + 1 (где п - число разрядов счетчика 15). Выход первого элемента цеиочки соединен с рабочим входом ключа 16, управляемого выходом элемента равнозначиости 7; выход второго элемента цепочки соединен со счетным входом счетчнка 9 и через ключ 17 - со счетным входом первого (младшего) разряда счетчика 15. Выход (-ГО элемента иеночки (i 2, 3, п + I, т. е. элементов 13, . . . , 14) соедииен через отдельный ключ (соответственно ключи 18 и 19) со счетным входом (i - 1)-го разряда счетчика 15. Разрядовые выходы счетчика 9 через коммутатор 20 соединены со входами /г логических элемеитов «И 21-23 (число /г связано с числом участков а/инроксимации воспроизводимой функции, выход каждого из которых через отдельный ключ (ключи 24- 26 - нервая группа ключей) и через логический элемент «ИЛИ 27, имеющий k входов, соединен со счетным входом счетчика 10. Коммутатор 20 позволяет соединять любой из IH входов каждого из элементов «И 21-23 с любым выходом счетчика 9, т. е. каждый из иих может быть настроен на срабатывание (возбуждение) при любом наперед заданном состоянии счетчика 9.

РазрядоБые выходы счетчика 10 соедииеиы со входами дешифратора 28 потенциального тина, а его выходы - со входами коммутатора 20. Этот коммутатор, имеюш,ий (« + 1) вы/ход, нозволяет соединять каждый из его выходов с любым подмножеством его входов. Один из выходов коммутатора 29 соединен со вторым входом элемента равнозначности 8, а каждый из остальиых п выходов - с управляющим входом одного из ключей второй группы (ключи 17-19).

Время задержки элементов 4 и 6 несколько меньше минимального интервала между входными импульсами, ио превосходит время переходных ироцессов в схеме. Времена задержки элементов И-14 существенно меньше и выбраны так, чтобы к моменту появления имнульса на выходе очередного элемента цепочки процессы в остальных элементах схемы (кроме элементов 4 и 6) были окончеиы.

Схема работает следующим образом.

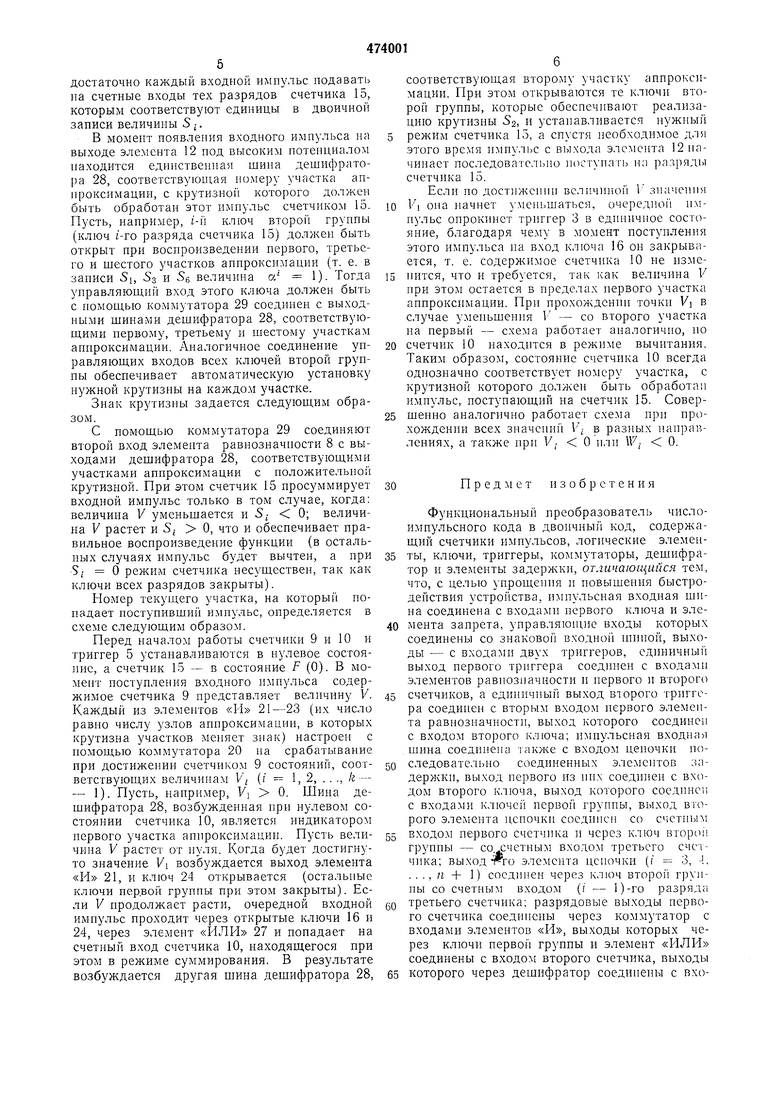

Пусть воснроизводимая функция и.меет вид, показанный на фиг. 2, т. е. 0 V, W ; W, где V - входная величина устройства, W - выходная величина устройства, и пусть она аппроксимирована кусочнолинейной функцией с (/г + 1) участками. Абсциссы и ординаты узлов аппроксимации обозначаются соответственно через Vf- и W , i I, 2, ..., k, при этом Vo Q, Vf, К.

Функция F является но определению дискретной, однако при больших значениях числа разрядов счетчика 9 in целесообразно говорить о линейной аппроксимации 1 в следуюИ1,ем смысле; на i-м участке аппроксимации Vj-i , V; едипичпое приращение величины V (один входной импульс) вызывает приращение W на величину 5,- ,

s, (W;- Г,,)/(У,--1/,,).

При этом величина s может рассматриваться как крутизиа (-го участка аппроксимации. Если величина s,- оказывается дробной, иредставим ее в виде sj + s , где sj - целая часть i. , а л; - дробная. Смысл s,ири этом таков: если О и V возрастает, то каждый входиой импульс увеличивает W на величину s-, кроме того каждые

+ 0,5 входных имиульсов увеличивает W на единицу (аналогично обстоит дело ири S; О и при уменьшении У).

Поскольку функция F дискретиа, скачок ее (см. фиг. 2) означает фактически наличие

участка аппроксимации мипнмальной длины (Vs V- + 1), при этом 58 Гв - Wj).

Схема устройства реализует описанную аппроксимацию. Импульс, поступаюший на шину а, проходит либо через ключ 1 - если величина V уменьшается (единичный потенциал па шине б), либо через элемент запрета 2 - при возрастании величины V (нулевой потенциал иа шине б).

Соответственно триггер 3 устанавливается

в единичное или нулевое состояние, переводя реверсивные счетчики 9 и 10 в нужный режим.

После окончания иереходных ироцессов в схеме (спустя время задержки элемента 4 или

6) триггер 5 устаиавливается в то же состояние, что и триггер 3. При этом ключ 16 в момент постуиления на него импульса через элемент 11 будет открыт только в том случае, когда «знак предыдущего импульса совпадает со «знаком поступившего, таК как в противиом случае триггеры 3 и 5 в этот момент находятся в различных состояниях, и следовательно, сигнал на выходе элемента равнозначности 7 отсутствует. В течеиие всего времени

переходных процессов в схеме (время «обработки одного входного импульса) единичный выход триггера 3 индицирует «знак постунившего на шииу а имнульса.

Пусть величина записана в двоичной

форме с числом /ii разрядов после запятой:

S;- af, ocf ;, а/..., аГ

11

а,(число Пи разрядов перед занятой равно числу разрядов выходного кода). Каждому си.мволу К; в двоичной заииси 5j соответствует специальный разряд счетчика 15, причем знаку а - старший, а знаку - младший.

Для реализации описанной аппроксимации

достаточно каждый входной импульс подавать на счетные входы тех разрядов счетчика 15, которым соответствуют единицы в двоичной записи величины 5;.

В момент ноявления входного импульса на выходе элемента 12 под высоким потенциалом находится единственная шина дешифратора 28, соответствующая номеру участка аппроксимации, с крзтизной которого должен быть обработан этот импульс счетчиком 15. Пусть, например, i-u ключ второй группы (ключ 1-го разряда счетчика 15) должен быть открыт при воспроизведении первого, третьего и шестого участков аппроксимации (т. е. в записи Si, 5з и Se величина а 1). Тогда управляющий вход этого ключа должен быть с помощью коммутатора 29 соединен с выходными шинами дешифратора 28, соответствующими первому, третьему и шестому участкам аппроксимации. Аналогичное соединение управляющих входов всех ключей второй группы обеспечивает автоматическую установку нужной крутизны на каждом участке.

Знак крутизны задается следующим образом.

С помощью коммутатора 29 соединяют второй вход элемента равнозначности 8 с выходами дешифратора 28, соответствующими участками аппроксимации с положительной крутизной. При этом счетчик 15 просуммирует входной импульс только в том случае, когда: величина V уменьшается и S; 0; величина V растет и 5; О, что и обеспечивает правильное воснроизведение функции (в остальных случаях импульс будет вычтен, а при S; 0 режим счетчика несуществен, так как ключи всех разрядов закрыты).

Помер текущего участка, на которьи попадает поступивший импульс, определяется в схеме следующим образом.

Перед началом работы счетчики 9 и 10 и триггер 5 устанавливаются в нулевое состояние, а счетчик 15 -- в состояние F (0). В момент поступления входного имнульса содержимое счетчика 9 представляет величину У. Каждый из элементов «И 21-23 (нх число равно числу узлов аппроксимации, в которых крутизна участков меняет знак) настроен с помощью коммутатора 20 на срабатывание при достижении счетчиком 9 состояний, соответствующих величинам V; (i 1,2,..., /г - - 1). Пусть, например, У 0. Шина дещифратора 28, возбужденная нри нулевом состоянии счетчика 10, является индикатором первого участка аппроксимации. Пусть величина V растет от нуля. Когда будет достигнуто значение Vi возбуждается выход элемента «И 21, и ключ 24 открывается (остальные ключи пер.вой группы при этом закрыты). Если V нродолжает расти, очередной входной имнульс проходит через открытые ключи 16 и 24, через элемент «ИЛР 27 и попадает на счетный вход счетчика 10, находящегося при этом в режиме суммирования. В результате возбуждается другая шина дешифратора 28,

соответствующая второму участку аппроксимации. При этом открываются те ключи второй группы, которые обеспечивают реализацию крутизны 2, и устанавливается нужный

счетчика 15, а спустя необходимое для этого врс.мя импульс с выхода элемента 12 пачинает последовательно иостунагь на )лзряды счетчика 15.

Если по достижении вели.чииой I знамеппя

У она начнет уменьшаться, очередпоГ нмпульс опрокпнет триггер 3 в единичное состояние, благодаря че.му в момент поступления этого импульса иа вход ключа 16 он закрывается, т. е. содержимое счетчика 10 не изменится, что и требуется, так как величина V при этом остается в пределах первого участка аппроксимации. При прохождсннп точкп Vi в случае умепьщепия V - со второго участка на первый - схема работает аналогично, по

счетчик 10 иаходптся в режиме вычитания. Таким образом, состояние счетчика 10 всегда однозначно соответствует номеру участка, с крутизной которого должеи быть обработан импульс, поступающий на счетчик 15. Совершенно аналогично работает схема прп прохождении всех значений V; в разных направлениях, а также при V,. О или W; 0.

Предмет изобретения

Функциональный преобразователь числоимпульсного кода в двоичный код, содержащий счетчики импульсов, логические элемеиты, ключи, триггеры, коммутаторы, дешифратор и элементы задержки, отличающийся тем, что, с целью упрощения и повышепия быстродействия устройства, импульсная входиая щнна соединена с входами первого ключа и элемента запрета, управляюн1ие входы которых соединены со знаковой входной шиной, выходы - с входами двух триггеров, единичный выход первого триггера соединен с входами элементов равнозначности и нервого и второго

счетчиков, а единичный выход второго триггера соединен с вторым входом нервого элемента равнозначности, выход которого соединен с входом второго ключа; имиульсная входная шина соединена 1акже с входом цеиочки последовательио соединенных элементов задержки, выход нервого из них соед1П1еи с входом второго ключа, выход которого соединен с входами ключей первой групны, выход второго элемента цсночкн соединен со счетным

входов нервого счетчика и через ключ второ грунны - со. счетным входом третьего счетчика; выход го элемента цепочки (( 3, -I, . . ., п + 1) соединен через ключ второй группы со счетным входом (/ - 1)-го разряд;,

третьего счетчика; разрядовые выходы иервого счетчика соединеиы через коммутатор с входами элементов «И, выходы которых через ключи первой группы и элемент «ИЛП соединены с входом второго счетчика, выходы

которого через дешифратор соединены с вхоass

Й

JLJ Г/

ly .

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор периодического напряжения | 1983 |

|

SU1238212A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| Устройство для определения среднего гармонического значения случайного процесса | 1975 |

|

SU669361A1 |

| Устройство для программного управления | 1983 |

|

SU1160367A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1983 |

|

SU1150769A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Преобразователь кодов чисел из одной системы счисления в другую | 1981 |

|

SU966894A1 |

| Функциональный генератор | 1980 |

|

SU902022A1 |

15

и/

W5 Wfi W;/

r

Щ

VJo

V

9 Wj

X

w,

Wz

Vo V, Vf Vj

V

Ve

Vg Vy

V/ B V,,

Авторы

Даты

1975-06-15—Публикация

1972-11-16—Подача