постоянной памяти, могут быть внесены либо при условии отказа от использования постоянной памяти и перемещения этих микропрограмм в оперативную память, либо посредством исправления информации, хранящейся в постоянной памяти, осуществляемого путем физического вмешательства в блок постоянной памяти, что сопряжено со значительными трудностями и обыкновенно приводит к снижению надежности и даже порче устройства. В результате этого отладка микропрограммного обеспечения при разработке вычислительной машины, как правило, представляющая собой итерационный процесс, резко тормозится, что приводит к существеппому удлипению сроков разработки машины. Кроме того, затрудняется модернизация и расширение микропрограммного обеспечения в условиях пользователя.

Другим недостатком является зависимость микропрограммного обеспечения от объема постояпной памяти, используемой в устройстве. Информация, обеспечивающая обращение к оперативной или постояпной памяти, должна быть указана непосредственно в микропрограммах. Поэтому при изменении объема постоянной памяти, используемой в устройстве, при перемещении отлаженных микропрограмм из оперативной памяти в постоянную либо при обратном их перемещении в случае корректировки должны быть изменены, но крайней мере, микрокоманды, обеспечивающие переход к перемещеппым микропрограммам, и микрокомапды, обеспечивающие переход от перемещенных микропрограмм к неперемещенным. Кроме того, различные модели вычислительных машин одного семейства должны иметь различные варианты микропрограммного обеспечения.

Еще один недостаток состоит в недостаточной жизнеспособности устройства.

Устройство неработоспособпо в случае возникновения в блоке оперативной памяти или в блоке постоянной памяти пеисправности, приводящей к невозможности правильиого считывания хотя бы одной микрокоманды. Например, характерными неисправностями такого рода являются выход из строя отдельных модулей памяти (при модульной структуре памяти), разрыв цепи адресного провода, короткое замыкание адресных проводов и т. д.

Целью изобретения является увеличение гибкости при наладке и эксплуатации устройства.

Для этого в него введены блок сравнения, блок задания сегментов, блок обнаружения смены сегментов. Выход блока задания множеств сегментов соединен с первым входом блока сравнения, выход регистра номера сегмента - со входом блока обнаружения смены сегментов, а выходы блоков сравнения и обнаружения смены сегментов, а выходы блоков сравнения и обнаружения смены сегментов соединены с соответствующими входами блока управления. Регистр номера сегмента, кроме того, соединен со вторым входом блока сравнения. Второй блок ассоциативных регистров соединен соответствующими входами с регистром адреса микрокоманд и шиной кодовой магистрали, а выходом - с блоком унравления, выход последнего соединен с регистрами адреса микрокоманд и номера сегмента и вторым блоком ассоциативных регистров. Кроме того, входы блоков сравнения и

управления соединены с шиной контроля и диагностики вычислительной машины.

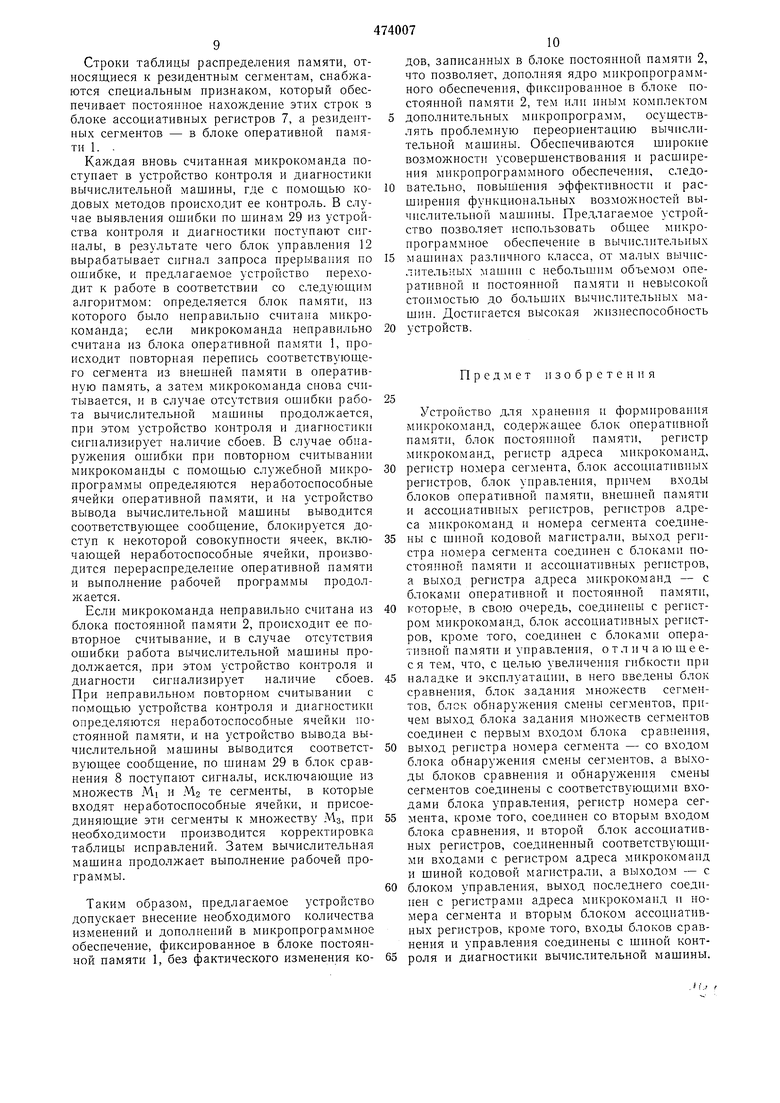

На чертеже представлена блок-схема предлагаемого устройства. В состав предлагаемого устройства входит

блок оперативной памяти 1, предназначенный для хранения информации, интенсивно используемой машиной и изменяюн1,ейся в процессе выполнения программы, причем один сегмент хранится в одной странице памяти.

Влок постоянной памяти 2 иредназначен для храпения сегментов микрокоманд, составляющих ядро микропрограммного обеспечения вычислительной машины; блок внешней памяти 3 - для хранения информации, с которой

работает вычислительная машина, включая сегменты микрокоманд. Регистр микрокоманд 4 для хранения выполняемой микрокоманды, регистр адреса микрокоманд 5 - для указания микрокоманды относительно начала сегмента. Регистр номера сегмента 6 предназначен для указания иомера сегмента, в которой входит микрокоманда, блок ассоциативных регистров 7 - для определения по номеру сегмента адреса страницы блока оперативпой памяти 1, в которой записан данный сегмент. В блоке ассоциативных регистров 7 хранится таблица расцределения оперативной памяти, устанавливающая соответствие между номерами сегментов и адресами страниц

блока оиеративной памяти 1, в которых записаны соответствующие сегменты, либо часть этой таблицы.

Блок сравнення 8 нредназначен для определения принадлежности запрошенного сегмента

одному из следующих непересекающихся множеств сегментов: множеству MI сегментов, фиксированных в блоке ностоянной памяти 2, в которых нет изменений, множеству М2 сегментов, фиксированных в блоке постоянной

памяти 2, в которых имеются изменения, множеству М.З сегментов, отсутствующих в блоке постоянной памяти 2.

Влок задания сегментов 9 предназначен для сообщения блоку сравнения 8

информации, позволяющей определить принадлежность любого сегмента одному из вышеуказанных множеств. Влок обнаружения смены сегментов 10 нредназначен для определения момента перехода к следующему сегменту. Влок ассоциативных регистров 11 предназначен для хранения таблицы изменений текущего сегмента, записанного в блоке иостоянной памяти 2, и обеспечивает ассоциативный поиск требуемой строки таблицы изменений (полная таблица изменений, в которой указаны все изменения микропрограмм, хранящихся в блоке постоянной памяти 2, записана в блоке оперативной памяти 1; в каждой строке таблицы изменений указан адрес микрокоманды, после выполнения которой необходим переход к микрокоманде, адрес которой указаи в той же строке таблицы).

Блок управления 12 предназначен для выполнения следую1цих функций: задание режима выборки микрокоманд из блока постоянной памяти 2, задание режима выборки микрокоманд из блока оперативной памяти 1, формирование сигналов запроса прерывания при переходе к сегменту, принадлежащему множеству Мг, или к сегменту множества Мз, отсутствующему в оперативной памяти, а также в случае обнаружения ошибки в считанной микрокоманде, выполнение переходов в соответствии с таблицей изменений.

Перечисленные блоки связаны меж/ду собой, а также с другими устройствами вычислительной машины, посредством шин 13-29. Шины 13 кодовой магистрали 13 предназначены для обмена информацией между блоком оперативной памяти 1, блоком внешней памяти 3, регистром адреса микрокоманд 5, регистром номера сегмента 6, блоком ассоциативных регистров 7, блоком ассоциативных регистров 11 и блоками других устройств вычислительной машины. Шикы 14 служат для передачи в регистр адреса микрокоманд 5 сигналов перехода к следуЕОщей микрокомаиде. Кодовые 15 предназначены для передачи адреса микрокоманды относительно начала сегмента в блок оперативной памяти I, блок постоянной памяти 2 и блоке ассоциативных регистров П. Кодовые шины 16 служат для передачи номера сегмента требуемой микрокоманды Б блок постоянной памяти 2, блок ассоциативных регистров 7, блок сравнения 8 и блок обнаружения смены сегментов 10, а кодовые шипы 17 - для передачи в блок оперативной памяти I адреса страницы требуемой микрокоманды.

Кодовые шины 18 предназначены для выдачи микрокоманды из блока оперативной памяти 1 в регистр микрокомаиды 4, кодовые ШИ1ТЫ 19 - для выдачи микрокоманд из блока постоягтпом памяти 2 в регистр микрокоманд 4. Кодовые шины 20 служат для передачи микрокоманд в устройство управления вычислительной машины, шины 21 - для передачи в блок сравнения 8 сигналов, позволягоших определить принадлежность любого сегметття одному из трех вышеуказанных множеств M -- М2Кпоме того, устройство содержит шины 22 сигнпло соавнения, указывающих на принадлежность текущего сегмента к ОДНОМУ из трех мтожесдп, шины 23 сигналов сравнения номера требуемого сегмента с одним из номеров сегментов, хоаняшимся в блоке ассоциативных регистров 7, шины 24 сигналов запуска блока управления 12 при переходе к очередному сегменту и шины 25 сигналов запуска

блока управления при совпадении содержимого регистра адреса микрокоманд 5 и одного из регистров блока ассоцнативиых регистров 11. Шины 26 служат для передачи в устройство управления вычислительной мащнны сигналов задания одного из следующих режимов; режима выборки микрокомаид из блока постоянной памяти 2 и режима выборки микрокоманд из блока оперативной памяти 1.

Имеются шины 27 сигналов выдачи из блока ассоциативных регистров 11 на шины 13 кодовой магистрали адреса микрокоманды в соответствии с табл1щей изменений и приема этого адреса в регистр адреса микрокоманды 5; шины 28 сигналов занроса прерывания для перехода к служебной микропрограмме и шины 29 сигналов обнаружения ошибки в считанной микрокоманде, поступающих от устройства контроля и диагностики вычислительной машины.

Подготовка предлагаемого устройства к работе производится следующим образом.

В блоке задания множеств сегментов 9 в соответствии с множествами MI и М2 нроизводится переключение (например, посредством включения тумблеров, предусмотренных в блоке заданий множеств сегментов 9, или установки перемычек), что обеспечивает передачу ио шинам 21 в блок сравнения 8 сигналов, указывающих мнол ество М сегментов, фиксированных в блоке постоянной памяти 2, в которых нет изменений, и множество Мо сегментов, фиксированных в блоке постоянной памяти 2, в которых имеются изменения. При

этом сегменты, которые претерпели существенные изменения и, хотя фактически присутствуют в блоке постоянной памяти 2, не могут быть использованы при выполнении программы, в выщеуказанные множества не включаются, в результате чего доступ к таким сегментам блокируется.

Под управлением программы, хранящейся в блоке постоянной памяти 2, производится начальная загрузка: в память микрокоманд

из внешнего накопителя или устройства ввода (магнитные ленты, перфоленты, перфокарты и т. д.) по шинам 13 кодовой магистрали передается необходимая информация (микропрограммное обеспечение, исправления микропрограмм, храняндихся в блоке постоянной памяти 2, указания с комплекте оборудования, имеющегося в составе вычислительной машины, и т. д.). При этом в блоке оперативной памяти I составляется таблица распределения памяти, в которой отражается распределение внешней и оперативной памяти для хранения сегментов, составляется таблица исправления микропрограмм, хранящихся в блоке постоянной памяти 2, происходит запись

служебной инфопман.иц и фиксированные ячейки блока оперативной памяти 1.

Обычно сегменты микрокоманд заг ружаются только в блок внешней памяти 3. Однако в случае, если некоторое количество микропрограмм, необходимых для работы памяти микрокоманд (например, микропрограмма переписи информации из блока внешней памяти 3 в блок оперативной памяти I), отсутствует в блоке постоянной памяти 2, то в блок оиератиБПой памяти 1 записывается некоторое количество сегментов, которые затем постояпно присутствуют в оперативной памяти, называемых резидентными, а в блок ассоциативных регистров 7 - соответствующие этим сегментам строки таблицы распределения памяти.

Устройство для хранения и формирования микрокоманд работает следуюни1М образом.

Математический адрес текущей микрокоманды, состоящий из номера сегмента и адреса микрокоманды относительно начала сегмента, поступает в регпстр адреса микрокоманд 5 н регнстр номера сегмента 6 но шинам 13 кодовой магистрали, либо формируется с помош,ью сигналов перехода к следующей микрокомаиде, nocTynaioniiix в регистр адреса микрокоманд 5 по шинам 14. Номер сегмента по кодовым шнпам 16 нередается в блок сравнения 8, где определяется вхождепие данного сегмента в одно из трех выиюуказаниых множеств, и в блок управления 12 по шипам 22 поступают сигналы сравнения. Номер сегмента поступает также в блок обнаружения смены сегментов 10, вырабатывающий в момент изменения кода в регистре номера сегмента 6 сигнал зануска блока упрагзления 12. Процедура перехода к участку микропрограммы, принадлежащему следующему сегменту, зависит от результата оиерации сравнения, выполняемой блоком сравнения 8.

Если сегмент входит в множество Мь с помощью сигналов, передаваемых в устройство управления вычислительиой машины по шниам 26, устанавливается режим выборки микрокоманд из блока постоянной памяти 2 до момента обращения к следующему сегменту. Выборка требуемой ячейки постоянной намяти осуществляется непосредственно с помощью математического адреса микрокоманды, совпадающего с ее физическим адресом в блоке постоянной памяти 2. Считанный код по кодовым шинам 20 поступает в устройство уиравлеиия вычислительной машины.

Если сегмент входит в миол ество Мз, с помощью сигналов, передаваемых по щинам 28, осуществляется переход к служебной микропрограмме, обеспечивающей перепись из блока оперативной памяти 1 в блок ассоциативных регистров 11 таблицы изменений текущего сегмента, после чего прерванная микропрограмма продолжает выполняться в режиме выборки микрокоманд из блока постоянной памяти 2 до момента обращения к следущему сегменту либо до момента окончания выполнения микрокоманды, адрес которой указан в блоке ассоциативных регистров 11. В этот момент в блок управления 12 по шинам 25 поступает сигнал запуска, в результате чего вырабатываются сигналы, передаваемые по щинам 27 в блок ассоциативных регистров 11, регистр номера сегмента 6, регистр

адреса микрокоманды 5 и обеспечиваюп ие перепись из блока ассоциативных регистров 11 и регистр иомера сегмента 6 и -регистр адреса микрокоманды 5 математического адреса очередной микрокоманды в соответствии с таблицей исиравлеиий.

Если сегмеит входит в множество Мз, немедленный доступ к нему возможен только в случае наличия номера требуемого сегмента

в блоке ассоциативных регистрор; 7. В этом случае блок аесоцпативпых регистров 7 вырабатывает сигнал сравнения, который совместс сигналом запуска поступает в блок унравления 12 н переключает устройство в режим

выборки микрокоманд из блока оиеративпой памяти 1. В этом режиме физический адрес микрокоманды в блоке оперативной памятп I задается адресом страиииы, переда аемым по кодовым ишнам 17, и адресом относгггелыю

начала страницы, передаваемым но кодовым нгииам 15. Считан ый код по кодовым шипам 18 принимается в регистр мпкрокомаудь 4, откуда по кодовым шипам 20 поступает в устройство управления вычислительной маи:ииь.

Нри отсутствии помера требуемого сегмента в блоке ассоциативных регистров 7 блок управления 12 вырабатывает сигнал запроса прерывапия, и вычислительная машина переходит к выполнению служебиой микропрограммы, обеспечивающей достуи к требуемому сегменту.

Нредварительно информация, храиящаяся в регистрах вычислительной мащииы, заиисывается в специальио отведенные ячейки блока

оперативной памяти 1, после чего в таблице распределения памяти по номеру сегмента отыскнвается физический адрес страницы памяти, в которой записан требуемый сегмент. Если эта страница принадлежит блоку оперативпой памяти 1, номер сегмента и адрес занимаемой им страницы занисываются в один из регистров блока ассоциативных регистров 7, определямый но некоторому правилу (нанример, циклически, либо па основании информации об интенсивности использоваиия регистров, накапливаемой в сиециальпом поле каждого регистра), затем происходит восстаиовление состояния процессора. Поскольку теперь в блоке ассоциативных регистров 7

нроисходит сравнение иомера сегмеита требуемой микрокоманды с содержимым одного из регистров, в1;1полнение прерванной микропрограммы продолжается. Если требуемый сегмент находится в блоке внешней памяти

3, то он переписывается в оперативную память. Если для хранения этого сегмента ие может быть выделена свободная страницы оперативной памяти, то в соответствии с некоторым правилом определяется сегмент, подлежащий удалению из блока оперативиой памяти 1, и на его место записывается требуемый сегмент, при этом производится корректировка таблицы распределения памяти в блоке оперативной памяти 1 и в блоке ассоциативных

регистров 7.

Строки таблицы распределения памяти, относящиеся к резидентным сегментам, снабжаются специальным признаком, который обеспечивает постоянное нахождение этих строк s блоке ассоциативных регистров 7, а резидентных сегментов - в блоке оперативной памяти 1. .

Каждая вновь считанная микрокоманда поступает в устройство контроля и диагностики вычислительной машины, где с помощью кодовых методов происходит ее контроль. В случае выявления ошибки по шинам 29 из устройства контроля и диагностики поступают сигналы, в результате чего блок управления 12 вырабатывает сигнал запроса прерывания по ошибке, и предлагаемое устройство переходит к работе в соответствии со следующим алгоритмом: определяется блок памяти, из которого было неправильно считана микрокоманда; если микрокоманда неправильно считана из блока оперативной памяти 1, происходит повторная перепись соотвстствуюшего сегмента из внешней памяти в оперативную память, а затем микрокоманда снова считывается, и в случае отсутствия ошибки работа вычислительной машины продолжается, при этом устройство контроля и диагностики сигнализирует наличие сбоев. В случае обнаружения ошибки при повторном считывании микрокоманды с помощью служебной микронрограммы определяются неработоспособные ячейки оперативной памяти, и на устройство вывода вычислительной машины выводится соответствующее сообщение, блокируется доступ к некоторой совокупности ячеек, включающей неработоспособные ячейки, производится перераспределение оперативной памяти и выполнение рабочей программы продолжается.

Если микрокоманда неправильно считана из блока постоянной памяти 2, происходит ее повторное считывание, и в случае отсутствия ошибки работа вычислительной машины продолжается, при этом устройство контроля и диагности сигнализирует наличие сбоев. При неправильном повторном считывании с помощью устройства контроля и диагностики определяются пеработоспособные ячейки постоянной памяти, и на устройство вывода вычислительной машины выводится соответствующее сообщение, ио шинам 29 в блок сравнения 8 поступают сигналы, исключающие из множеств MI и MS те сегменты, в которые входят неработоспособные ячейки, и присоединяющие эти сегменты к множеству Мз, при необходимости производится корректировка таблицы исправлений. Затем вычислительная машина продолжает выполнение рабочей программы.

Таким образом, предлагаемое устройство допускает внесение необходимого количества изменений и дополнений в микропрограммное обеспечение, фиксированное в блоке постоянной памяти 1, без фактического изменения кодов, записанных в блоке постоянной памяти 2, что позволяет, дополняя ядро микропрограммного обеспечения, фиксированное в блоке постоянной памяти 2, тем или иным комплектом дополнительных микропрограмм, осуществлять проблемную переориентацию вычислительной машины. Обеспечиваются щирокие возможности усовершенствования и расщирения микропрограммного обеспечения, следовательно, повыщения эффективности и расщирения функциональных возможностей вычнслительной машины. Предлагаемое устройство позволяет использовать общее мпкропрограммное обеспеченне в вычпслительных

машинах различного класса, от малых вычислительных машин с небольшнм объемом оперативной н постоянной памяти п невысокой стоимостью до больших вычислительных машин. Достигается высокая жпзпеспособпость

устройств.

Предмет 1 зобретенпя

Устройство для храненпя и формирования микрокоманд, содержащее блок оператпвпой памяти, блок постояииой памяти, регистр микрокоманд, регистр адреса микрокоманд,

регистр номера сегмента, блок ассоциативных регистров, блок управления, прпчем входы блоков оперативпой памятп, внешней памятп и ассоциативных регистров, регистров адреса микрокомаид и номера сегмента соединены с шнной кодовой магистрали, выход регистра номера сегмента соединен с блоками постоянной памяти и ассоциативных регистров, а выход регистра адреса микрокоманд - с блоками оперативной и постояпной памяти,

которые, в свою очередь, соединены с регистром микрокоманд, блок ассоциативных регистров, кроме того, соединен с блоками оперативной памятп и управления, отличающеес я тем, что, с целью увеличения гибкости при

наладке и эксплуатации, в него введены блок сравнения, блок задания множеств сегментов, блок обнаружения смены сегментов, причем выход блока задания множеств сегментов соединен с первым входом блока сравпенпя,

выход регистра номера сегмента - со входом блока обнаружения смены сегментов, а выходы блоков сравнения и обнаруження смены сегментов соединены с соответствующими входами блока управления, регистр номера сегмента, кроме того, соединен со вторым входом блока сравнения, и второй блок ассоциативных регистров, соединенный соответствующими входами с регистром адреса микрокоманд и шиной кодовой магистрали, а выходом - с

блоком управления, выход последнего соедпиен с регистрами адреса микрокоманд и номера сегмента и вторым блоком ассоциативных регистров, кроме того, входы блоков сравиения и управления соединены с шиной контроля и диагностики вычислительной машины.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная машина со структурной интерпретацией входного языка | 1971 |

|

SU513567A2 |

| Вычислительная машина со структурной интерпретацией входного алгоритмического языка | 1966 |

|

SU208353A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Внешнее устройство управления | 1978 |

|

SU736100A1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU1018118A1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Система сбора информации о движущемся транспортном средстве | 1981 |

|

SU1194750A1 |

| Микропрограммное устройство управления с исправлением ошибок | 1981 |

|

SU985789A1 |

Авторы

Даты

1975-06-15—Публикация

1973-03-13—Подача