I Изобретение относится к вычислительной технике, в частности к устройствам микропрограммного управления -повышенной надежности.

. Известно MHKponporpaNWHoe устройство с контролем переходов, содержащее блок памяти микрокоманд, (регистр адреса, регистр микрокоманд, блок сравнения, блок управлеНИН переходами и сдвигакмций регистп

CiJv .

Однако известное устройство не обнаруживает ложные условные переход ды между участками с одинаковой конфигурацией, не контролирует безусловные переходы.

Наиболее близким по технической сущности к изобретению является микропрограммное устройство управления с .контролем переходов, содержащее блок памяти микрокоманд, реристр адреса регистр микрокоманд, блок сравнения, блок управления переходами, блок ассоциативной пймяти, регистр контроля, распределитель датульсов, элемент И . и элемент ..

Данное устройство койтролирует . выполнение только условных переходов в микропрограмме, вследйтвие чего обнаруживаются только пожнце переходы . по условию. Кроме того, если ложными оказываются безусловаые переходы (пропуски, воз вратыJвнутри линейного участка между двумя условными переходами, то они оказываются не обнаруженными.. , Цель изобретения - повншение досто верности койтроля переходов.

поставленная цель достигается тем. что в устройство Мйкропрограьданого управления с контро/юм содержащее блок памяти микрокоманд, регистр адреса, регистр микрокшанд, блок ynpas ленйя.переходами, блок сравнеиия| : блок ассоциативной памяти, распределитель импульсо г элемент И и эле.мент ИЛИ, причем первый вход блока . управления переходами является управ входом устройства, информационный вход блока управления переходами соединен с пёрв1ью выходом регистра микрокоманд, второй и третий выхода которого связаны сортветственнб с входов выбора условия блоIка управления переходами и перзшл входом блока ассоциативной памяти, второй вхон которого соединен с ин фОЕо ационным выходом Олрка управле- - ния п ереходамиГл у 1 щп ехаазяЛ выход ко, торого подключен к управляющему входу блока сраанёняя первый, информационный вход которого связан е вы ходом регистра адреса ц входом блока памяти микрО1с : д выход которого соединен с ййфршадноаным входом гистрамикйж анд, установочный вход которого подключен ко входу начальной установки устройства, к установочному входу блока сравнения и к первому входу элемента ИЛИ. второй вход которого связан с выходом первого элемента И, инверсный вход которого соединен с первым входом блока сравнения, второй вход..элемента .И связан с первым выходом распределителя импульсов, второй, третий И четвертый выходы которого соединены соответственно с- тактовыми входами регистра микрокоманд, блок сравнения и регистра адреса, установочный вход которого соединен с входом начальной установки устройства, управляющий и информационный входырегистра адреса соединены соответственно с управляющим выходом блока управления переходами и вторым входом блока ассоциативной памяти, выход регистра микрокоманд и выход блока сравнения являются соответственно управляющим и сигнальным выходами устройства, введены счетчик контроля и второй элемент И. причем информацион|ный вход счетчика контроля связан ,с выходом блока ассоциативной памяти -ВХОД сброса и счетный вход счетчика контроля соединены соответственно с выходом элемента ИЛИ и выходе второго элемента И, первый и второй входы которого связаны соответственн с управлякйцим выходом блока управле.ния переходами и первым выходом распределителя импульсов, выход счетчика контроля подключен к второму информационному входу блока- сравнения.

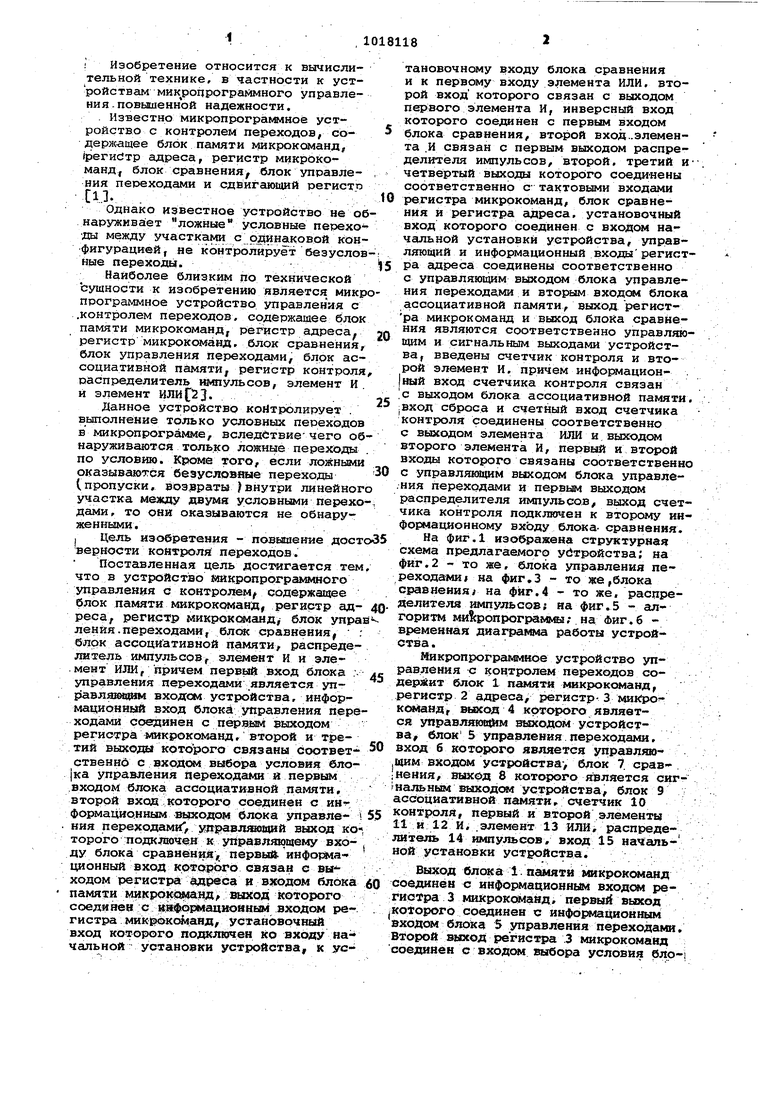

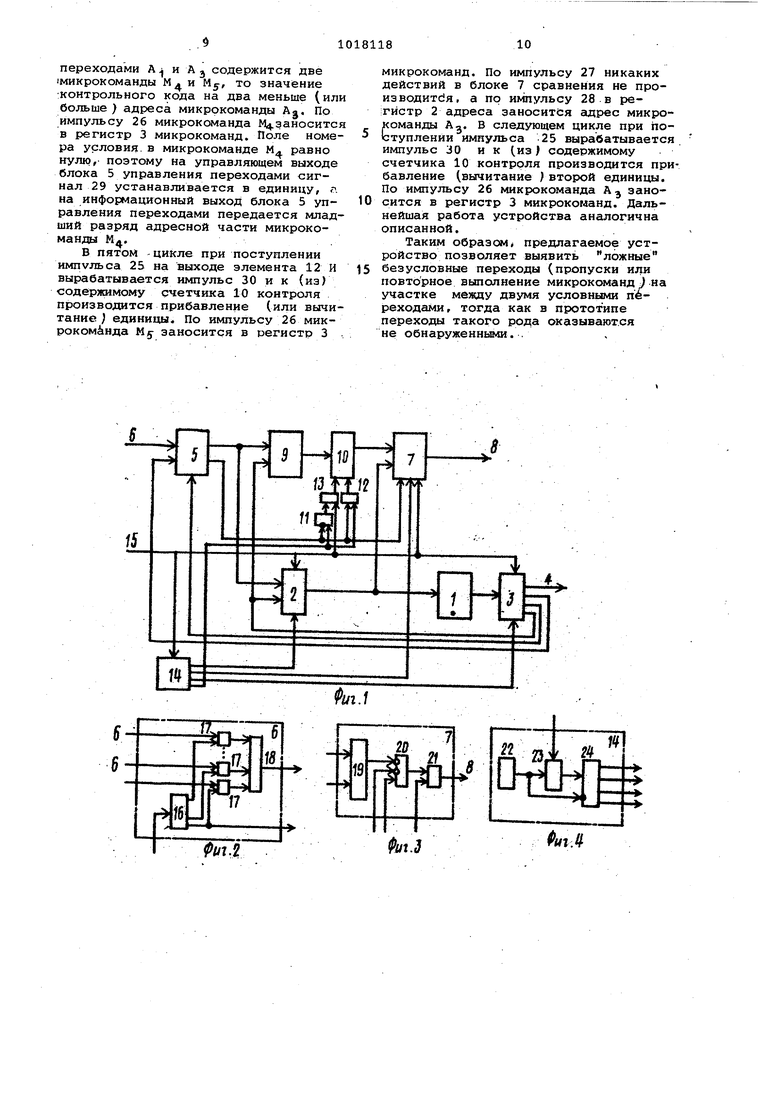

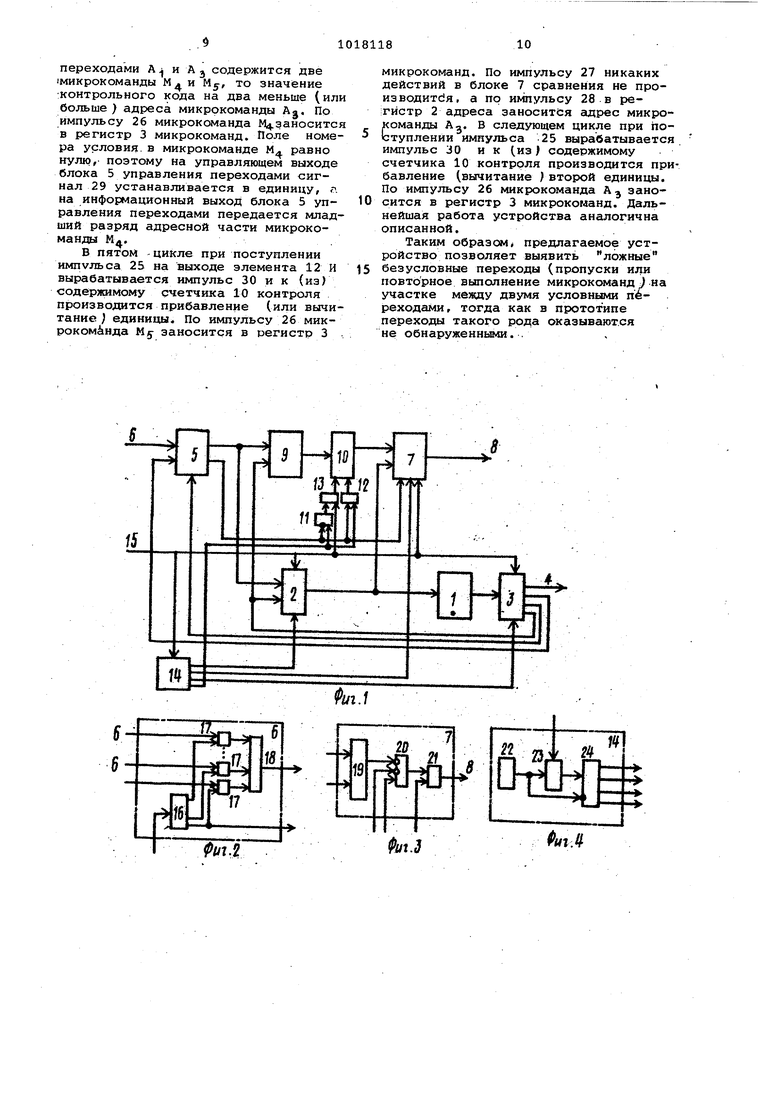

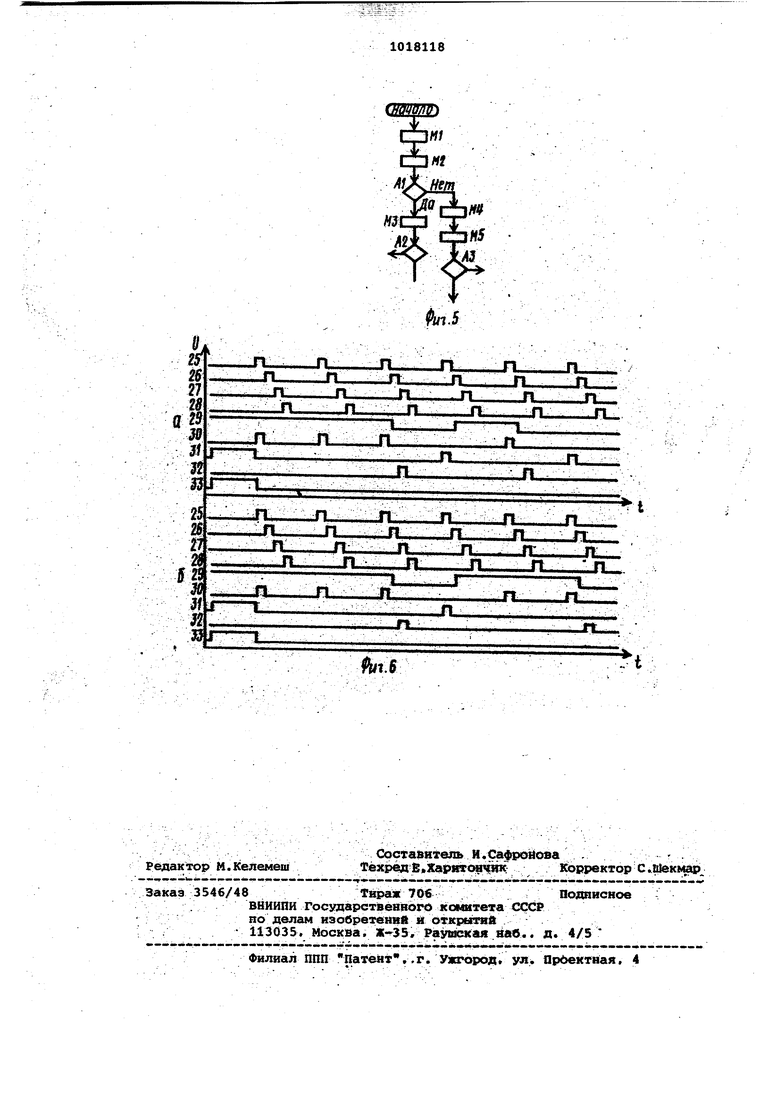

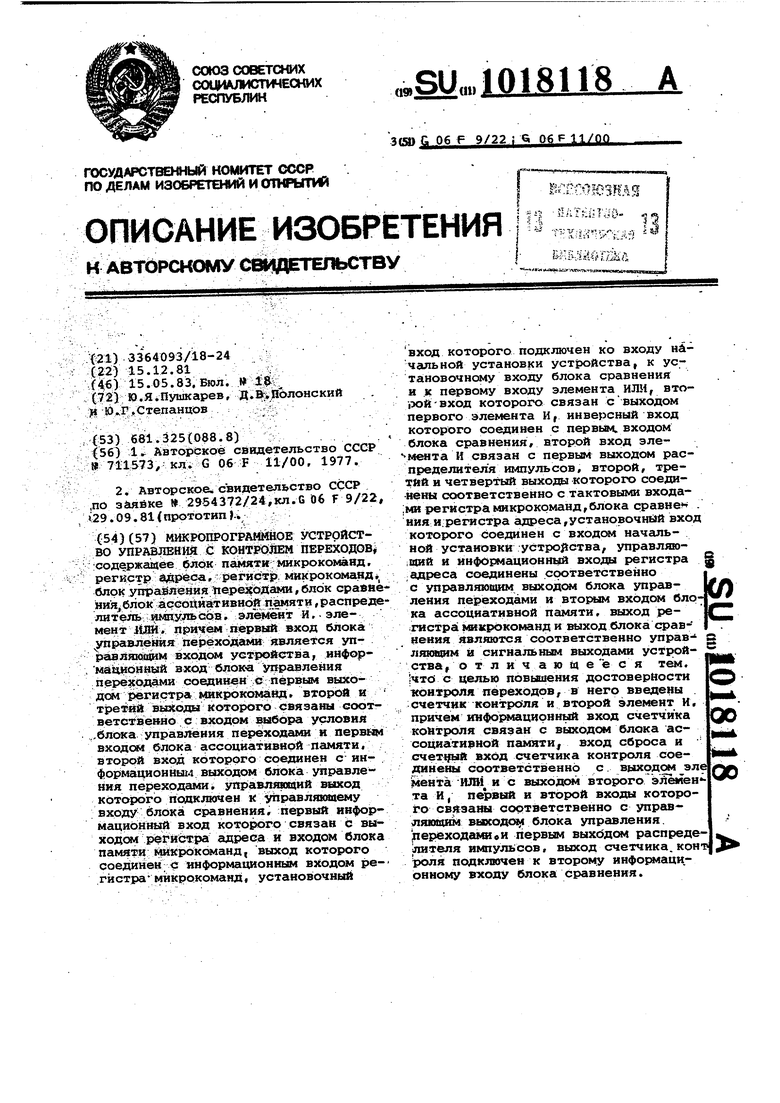

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - то же. блока управления переходами на фиг.З - то же,блока сравнения на фиг.4 - то же, распределителя импульсов; на фиг.5 - алгоритм ми1сропрограммы; на Фиг.б времеНЕШя диаграмма работы устройства. ..;... ;

Йикропрограминое устройство управления с коитролем переходов содерясит блок 1 памяти микрокоманд, регистр 2 адреса, регистр-3 микрокоманд, вьвсод 4 которого является управляювй1м эькодом устройства, блок 5 управления переходами, вход б которого является управляющим входом устройства-, блок 7 срав.нения, аызсбд 8 которого является сигfнальным выходе устройства, блок 9 ассоциативной памяти, счетчик 10 контроля, первый и второй элементы Ни 12 И, .элемент 13 ИЛИ распределитель 14 импульсов, вход 15 начальной установки устройства.

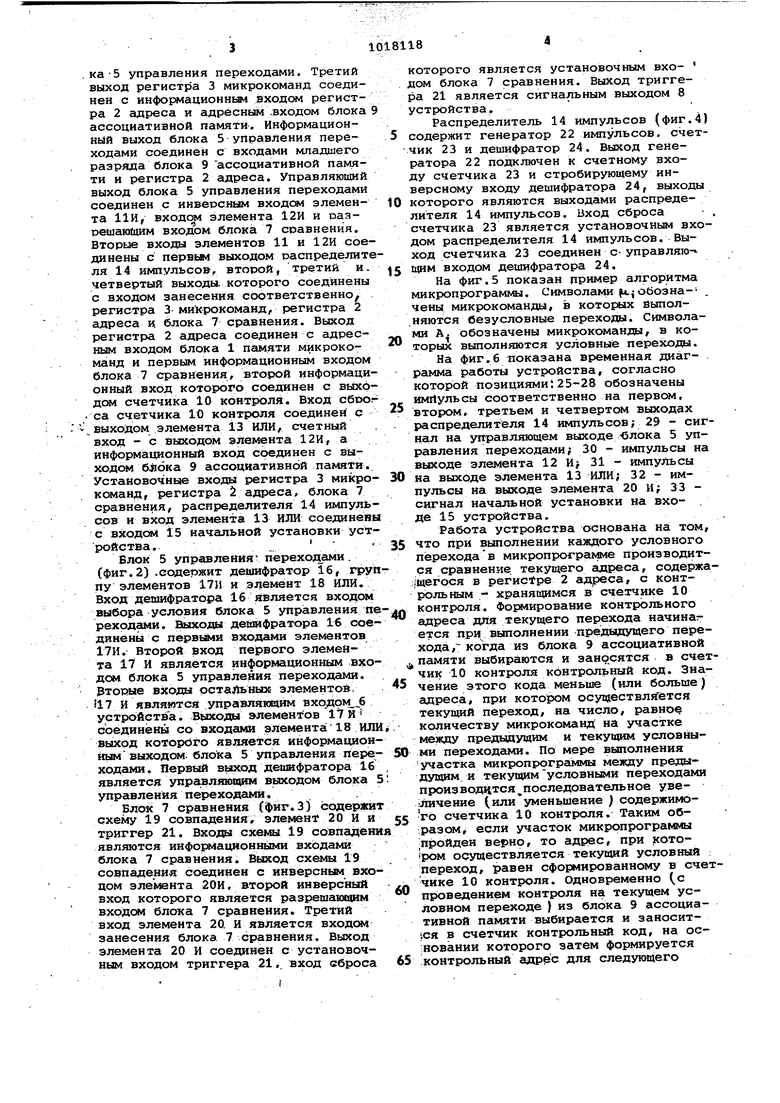

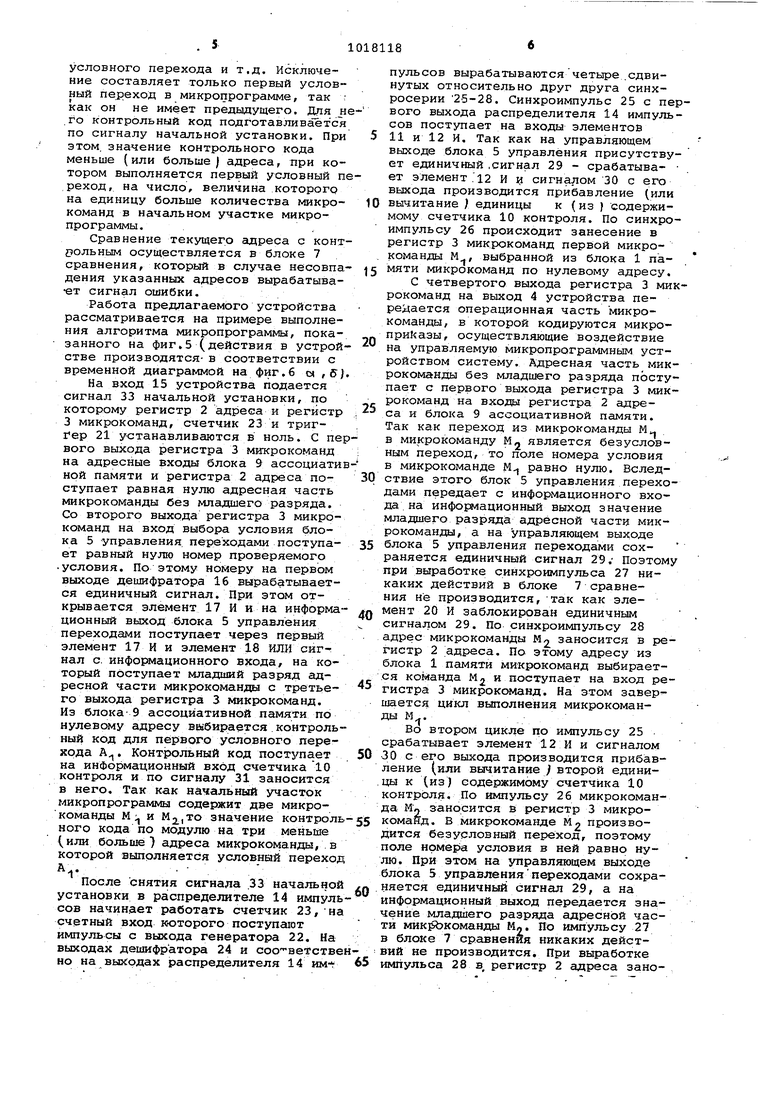

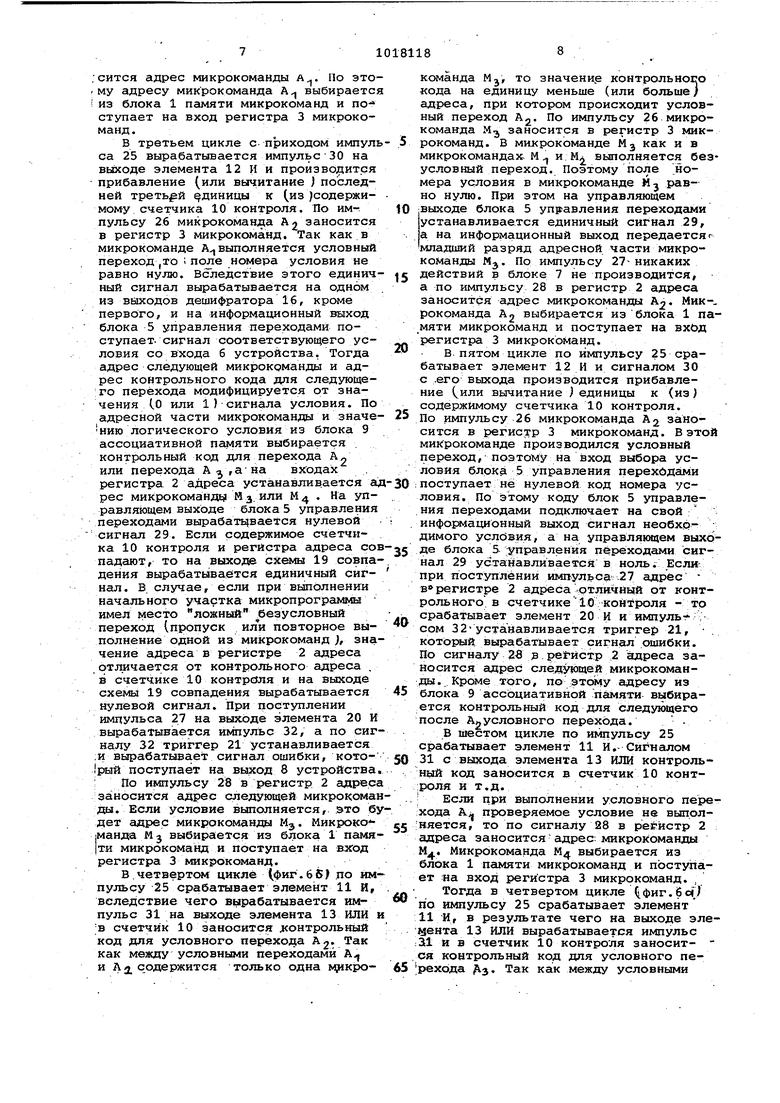

Выход блока 1. памяти микрокс яанд соединен с информационным входе регистра 3 микрокойанд. первый выход |которого соединен с инфЬ я4аЦиониыА4 входсм блока 5 управления переходами Второй выход регистра ,3 микрокоманд соехшнен с входсм выбора условия бло .ка-5 управления переходами. Третий выход регистра 3 микрокоманд соединен с информационным входом регистра 2 адреса и адресным .входом блока ассоциативной памяти. Информационный выход блока 5 управления переходами соединен с входами младшего разряда блока 9 ассоциативной памяти и регистра 2 адреса. Управляющий выход блока 5 управления переходами соединен с инверсным входсм элемента Ни, входсж элемента 12И и оазрешаю(аим входом блока 7 сравнения. Вторые входы элементов 11 и 12И соединены с первьш выходом распределите ля 14 импульсов, ВТОРОЙ, третий и. четвертый выходы, которого соединены с входом занесения соответственно, регистра 3 микрокоманд, регистра 2 адреса и блока 7 сравнения. Выход регистра 2 адреса соединен с адресным входом блока 1 памяти микрокоманд и первым информационным входом блока 7 сравнения, второй информационный вход которого соединен с выходом счетчика 10 контроля. Вход сброг . са счетчика 10 контроля соединен с выходом элемента 13 ИЛИ, счетный вход - с выходом элемента 12И, а информационный вход соединен с выходс 4 б4зрка 9 ассоциативной памяти. Установочные входы регистра 3 микрокоманд, регистра адреса, блока 7 сравнения, распределителя 14 импульсов и вход элемента 13 ИЛИ соединены с входом 15 начальной установки устройства. Блок 5 управления переходами. (фиг.2) .содержит дешифратор 16, груп пу элементов 17И и элемент 18 ИЛИ Вход дешифратора 16 является входом выбора условия блока 5 управления пе рехрдсшя. Выходы дешифратора 16 соединены с первыми входами элементов 17И. Второй вход первого элемейта 17 К является информационным входом блока 5 управления переходами. Вторые входы остальных- элементов. il7 И являмтся управляюЕШм вхо,дом.,.6 устрбйетва. Выходы элементов 17 И соединены со входа в1 элемента 18 ИЛИ выход которого является информащюниымвыходом, блока 5 управления переходами. Первый вшсод деишфратора 16 является управляюпщм выходом блока 5 управления переходами. . Блок 7 сравнения (фиг.3) содержит схему 19 совпадения, элемент 20 И и триггер 21. Входы схемы 19 совпадени являются информационными входами блока 7 сравнения. Выход схемы 19 совпадения соединен с инверсньм входом элемента 20И. второй инверсный вход которого является разрешающим входсм блока 7 сравнения. Третий вход элемента 20. И является входсж эанесения блока 7 сравнения. Выход элемен та 20 И соединен с установочным входом триггера 21,. вход вброса которого является установочным входом блока 7 сравнения. Выход триггера 21 является сигнальным выходом 8 устройства. Распределитель 14 импульсов (фиг.4) содержит генератор 22 импульсов, счетчик 23 и дешифратор 24, Выход генератора 22 подключен к счетному входу счетчика 23 и стробирующему инверсному входу дешифратора 24, выходы которого являются выходами распределителя 14 импульсов. Вход сброса - , счетчика 23 является установочным входом распределителя 14 импульсов. Выход счетчика 23 соединен с-управляю- щим входом дешифратора 24. На фиг.5 покаэан пример алгоритма микропрограммы. Символамиjj,,-обоз начены микрокоманды, в котордх выполняются безусловные переходы. Символами А обозначены микроксяланды, в которых выполняются условны1е переходы. На фиг.6 показана временная диаграмма работы устройства, согласно которой позициями;25-28 обозначены имг1ульсы соответственно на первом, втором, третьем и четвертом выходах распределителя 14 ю«1ульсов; 29 - сигнал на уггравляющем выходе -блока 5 управления переходами; 30 - импульсы на выходе элемента 12 И 31 - импульсы на выходе элемента 13 ИЛИ j 3 2 - импульсы на выходе элемента 20 И; 33 сигнал начальной установки на входе 15 устройства. Работа устройства основана на том, что при вьтолНении каждого условного переходав микропрогракяле производится сравнение, текущего гшреса, содержа|щегося в регис ре 2 ад)реса, с контроль ным - хранящимся в счетчике 10 контроля. Формирование контрольного адреса для текущего перехода начинаг ется прц выполнении предыдущего перехода,- когда из блока 9 ассоциативной памяти выбираются и заносятся в счетчик 10 контроля контрольный код. Значение этого кода меньше (или больше) адреса, при котором осуществляётся текупщй переход, на число, равное количеству микрокомаид на участке между предыдущим и текущим условными переходами. По мере выполнения участка микропрограммы между предыдущим и текущимусловными переходами производится,последовательное уве.Личение (илиуменьшение ) содержимого счетчика 10 контроля. Таким образсяу если участок микропрограммы пройден верно, то адрес, при котоipoM осуществляется текущий условный переход, равен сформированному в счетчике 10 контроля. Одновременно (.с проведением контроля на текущем условном переходе ) из блока 9 ассоциативной памяти выбирается и заносит1ся в счетчик контрольный код, на ос:новании которого затем формируется контрольный адресе для следующего условного перехода и т.д. Исключение составляет только первый условный переход в микропрограмме, так : как он не имеет предыдущего. Для к го контрольный код подготавливаётся по сигналу начальной установки. При этом, значение контрольного кода меньше (или больше) адреса, при котором выполняется первый условный п реход, на число, величина которого на единицу больше количества микрокоманд в начальном участке микропрограммы. Сравнение текущего адреса с конт рольным осуществляется в блоке 7 сравнения, который в случае несовпа дения указанных адресов вырабатывает сигнал ошибки. Работа предлагаемого устройства рассматривается на примере выполнения алгоритма микропрограммы, показанного на фиг.5 (действия в устрой стве производятся- в соответствии с временной диаграммой на фиг,6 о ,5| На вход 15 устройства подается сигнал 33 начальной установки, по которому регистр 2 адреса и регистр 3 микрокоманд, счетчик 23 и триг1ер 21 устанавливаются в ноль. С пе вого выхода регистра 3 микрокоманд на адресные входы блока 9 ассоциати ной памяти и регистра 2 адреса поступает равная нулю адресная часть микрокоманды без младшего разряда. Со второго выхода регистра 3 микрокоманд на вход выбора условия блока 5 -управления, переходами поступает равный нулю номер проверяемого условия. По этому номеру на первом выходе дешифратора 16 вырабатывается единичный сигнал. При этом открывается элемент 17 И и на информа ционный выход блока 5 управления переходами поступает через первый элемент 17 И и элемент 18 ИЛИ сигнал с. информационного вкода, на который поступает младший разряд адресной части микрокоманды с третьего выхода регистра S микрокоманд. Из блока 9 ассоциативной памяти по нулевому адресу )ается .контроль ный код для первого условного перехода А. Контрольный код поступает на информационный вход счетчика 10 контроля и по сигналу 31 заносится в него. Так как начальный участок микропрограммы содержит две микрокоманды М :j и М2,то значение контрол ного кода по модулю на три меньше (или больше) адреса микрокоманды, . в которой выполняется условный перехо А. После снятия сигнала .33 начально установки в распределителе 14 импул сов начин.ает работать счетчик 23, н счетный вход которого поступают импульсы с выхода генератора 22. На выходах дешифратора 24 и соо ветств но на выходах распределителя 14 им пульсов вырабатываются четыре .сдвинутых относительно друг друга синхросерии 25-28. Синхроимпульс 25 с первого выхода распределителя 14 импульсов поступает на входы элементов 11 и 12 И. Так как на управляющем выходе блока 5 управления присутствует единичный .сигнал 29 - срабатыва- ет элемент .12 И i сигналом 30 с его выхода производится прибавление (или вычитание ) единицы к (из ) содержимому счетчика 10 контроля. По синхроимпульсу 26 происходит занесение в регистр 3 микрокоманд первой микрокоманды М, выбранной из блока 1 памяти микрокоманд по нулевому адресу. С четвертого выхода регистра 3 микрокоманд на выход 4 устройства передается операционная часть микрокоманды , в которой кодируются микроприКазы, осуществляющие воздействие на управляемую микропрограммным устройством систему. Адресная часть микрокоманды без младшего разряда поступает с первого выхода регистра 3 микрокоманд на входы регистра 2 адреса и блока 9 ассоциативной памяти. Так как переход из микрокоманды М в микрокоманду М является безусловным переход, то поле номера условия в микрокоманде М равно нулю. Вследствие этого блок 5 управления переходами передает с информационного входа на информационный выход значение млада1его разряда адресной части микрокоманды, а на управляющем выходе блока 5 управления переходами сохраняется единичный сигнал 29 . Поэтому при выработке синхроимпульса 27 никаких действий в блоке 7 сравнения не производится, так как элемент 20 И заблокирован единичным сигналом 29. По синхроимпульсу 28 адрес микрокоманды М2 заносится в регистр 2 адреса. По этому адресу из блока 1 памяти микрокоманд выбирается команда М. и поступает на вход регистра 3 микрокоманд. На этом завершается цикл выполнения микрокоманды М.. Во втором цикле по импульсу 25 срабатывает элемент 12 И и сигналом 30 с его выхода производится прибавление (или вычитание ) второй единицы к (из) содержимому счетчика 10 контроля. По импульсу 26 микрокоманда М2 зано.сится в регистр 3 микрокоманд. В микрокоманде М2 производится безусловный переход, поэтому поле номера условия в ней равно нулю. При этом на управляющем выходе блока 5 управленияпереходами сохраняется единичный сигнал 29, а на информационный выход передается значение младшего разряда адресной части микрЬкоманды М,. По импульсу 27 в блоке 7 сравнения никаких действий не производится. При выработке импульса 28 в регистр 2 адреса заносится адрес микрокоманды А. По это му адресу микрокоманда А выбираетс из блока 1 памяти микрокоманд и по- ступает на вход регистра 3 микрокоманд. В третьем цикле с приходом импул са 25 вырабатывается импульс30 на выходе элемента 12 И и производится прибавление (или вычитание ) последней третьей единицы к (из содержимому счетчика 10 контроля. По им-г пульсу 26 микрокоманда А2 заносится в регистр 3 микрокоманд. Так как в микрокоманде А выполняется условный переход ,то поле номера условия не равно нулю. Вследствие этого единич ный сигнал вырабатывается на одном из выходов дешифратора 16, кроме первого, и на информационный выход блока 5 управления переходами поступает, сигнал соответствующего условия со входа 6 устройства. Тогда адрес следующей микрокоманды и адрес контрольного кода для следующе;го перехода модифицируется от значения (.0 или 1 ) сигнала условия. По адресной части микрокоманды и знача нию логического условия из блока 9 ассоциативной выбирается . контрольный код для перехода А2 или перехода А,ана входах . регистра 2 адреса устанавливается а рее микрокоманде М3. или М . На управляющем выходе блока 5 управления переходами вырабатцвается нулевой сигнал 29. Если содержимое счетчика 10 контроля и регистра адреса со падают, то на выходе схемы 19 совпа дения вырабатывается единичный сигнал. В. случае, если при вьшолненки начального участка микропрограммы имел место ложный Jбeзycлoвный переход (пропуск или повторное выполнение одной из микрокоманд ), зна чение адреса в регистре 2 адреса отличается от контрольного адреса . в счетчике 10 контроля и на выходе схемы 19 совпадения вырабатывается нулевой сигнал. При поступлении импульса 27 на выходе элемента 20 И вырабатьгоается импульс 32, а по сиг налу 32 триггер 21 устанавливается ;и вырабатывает сигнал ошибки, кото рый поступает на выход 8 устройства По импульсу 28 в регистр 2 адрес заносится адрес следующей микрокома ды. Вели условие выполняется,. .&то б дет адрес микрокоманды М. Микрокод манда Мз выбирается из блока 1 памя ти микрокоманд и поступает на вход регистра 3 микрокоманд. В.четвертс цикле (фиг.65) .по им пульсу 25 срабатывает элемент 11 И, вследствие чего вырабатывается импульс 31 на выходе элемента 13 ИЛИ в счетчик 10 заносится д онтрольный код для условного перехода А2. Так как между условными переходами А и Л 2 содержится только одна л крокоманда Mj, то значени.е контрольного кода на единицу меньше (или больше) адреса, при котором происходит условный переход Aj. По импульсу 26 микрокоманда M.J заносится в регистр 3 микрокоманд. В микрокоманде М как ив микрокомандах-М и.м, выполняется безусловный переход. Поэтому поле номера условия в микрокоманде М равно нулю. При этом на управляющем выходе блока 5 управления переходами устанавливается единичный сигнал 29, а на информационный выход передаетсяг младший разряд адресной части микрокоманды Mj. По импульсу 27-никаких действий в блоке 7 не производится, а по импульсу 28 в регистр 2 адреса заносится адрес микрокоманды А2. Мик-. рокрманда А2 выбирается изблока 1 памяти микрокоманд и поступает на вход регистра 3 микрокоманд. В пятом цикле по импульсу 25 срабатывает элемент 12 И и сигналом 30 с .его выхода производится прибавление (или вычитание ) единицы к (из ) содержимому счетчика 10 контроля. По импу.пьсу 26 микрокоманда А2 заносится в регистр 3 микрокоманд. Бэтой микрокоманде производился условный переход, поэтому на вход выбора условия блока 5 управления переходами поступает не нулевой код номера условия. По этому коду блок 5 управления переходг1ми подключает на свой информационный выход сигнал необхр- ; димого условия, а на управляющем выходе блока 5 управления переходами сигнал 29 устанавливаетс)Я в ноль; Еслипри поступлении импульса -27 адрес в регистре 2 адреса-отличный от контрольного в счетчике 10 контроля - тр срабатывает элемент 20 И и импуль-, сом 32-устанавливается триггер 21, который вырабатывает сигнал ошибки. По сигналу 2S э ре Истр 2 адреса заносится адрес следующей микрокоманды .. Кроме того , по aTCMeiy адресу из блока 9 ассоциативной памяти выбирается контрольный код для след5кицего после Алусловного перехода. В шестом цикле по импульсу 25 срабатывает элемент 11 И,- Сигналом 31 с выхода элемента 13 ИЛИ контрольный код заносится в счетчик 10 конт.ррля и т.д. Если при выполнении условного перехода A.;j проверяемое условие не выпрлняется, то по сигналу 28 в регистр 2 адреса заноситсяадрес; микрокоманды Мц.. Микрокоманда М выбирается из блока 1 памяти микрокоманд и nbcTjmaет на вход регистра 3 микрокоманд. , Тогда в четвертом цикле фиг.6с( по импульсу 25 срабатывает элемент 11 И, в результате чего на выходе эле«ента 13 ИЛИ вырабатывается импульс и в счетчик 10 контроля заносит- ся контрольный код для условного перехОда Дз- 1 как между условными

переходами А и А j содержится две микрокоманды М, то значение ;контрольного кода на два меньше (или больше ) адреса микрокоманды Aj. По импульсу 26 микрокоманда |.заносится в регистр 3 микрокоманд. Поле номера условия, в микрокоманде М равно нулю, поэтому на управляющем выходе блока 5 управления переходами сигнал 29 устанавливается в единицу, i. на информационный выход блока 5 управления переходами передается младший разряд адресной части микрокоманды М.

В пятом цикле при поступлении шлпульса 25 на выходе элемента 12 И вырабатывается импульс 30 и к (из) содержимому счетчика 10 контроля производатся прибавление (или вычитание единицы. По импульсу 26 микроком нда Mj заносится в регистр 3

микрокоманд. По импульсу 27 никаких действий в блоке 7 сравнения не производитЬя, а по иктульсу 28 в регистр 2 адреса заносится адрес микрокоманды Ад. В следующем цикле при поЬтупленйи имнульса 25 вырабатывается импульс 30 и к (из содержимому счетчика 10 контроля производится прибавление (вычитание ; второй единицы. По импульсу 26 микрокоманда А эано0 ситея в регистр 3 микрокоманд. Дальнейшая работа устройства аналогична описанной.

Таким образом предлагаемое устройство позволяет выявить ложные

5 безусловные переходы (пропуски иди повторное выполнение микрокомандJ на участке между двумя условньиии переходами, тогда как в прототипе переходы такого рода оказываются не обнаруженными.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Микропрограммное устройство управления с контролем переходов | 1982 |

|

SU1109749A2 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1005051A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1236475A1 |

| Микропрограммное устройство управления | 1981 |

|

SU959078A1 |

| Устройство управления с контролем переходов | 1983 |

|

SU1103238A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1636845A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1211724A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЙ С КОНТРОЛЕМ ПЕРЕХОДОВ содержащее блок памяти микрокоманд, регистр Адреса, регистр микрокоманд блок управления 1tIepexo;taми, блок сраваёния,блок ассоциативно памяти «распределитель импульсов, элЪкйнт и..элемент 1да1. причем первый вход блока управления переходами является управляющим входом устройства, инфор. мационный вход блок-а управления переходами соединен с первым выходом регистра микрокоманд, второй и третий выходы которого связаны соответственно с входом выбора условия „блока управления переходами и первсгм входом блока ассоциативной памяти, второй вход которого соединен с информационмы. выходом блока травлеВИЯ переходили i пра вляивдий выход которого подключен к управляющему ВХОДУ; блока сравнёнияг первый информационный вход которого связан Ь выходсял peiTHCTpa адреса и входом блока памяти глйкрокоманд, выход которого срейийен; с информационным входом регистра- микрокоманд, установочный вход которого подключен ко входу нА:чальной установки устройства, к установочному входу блока сравнения . и к первому входу элемента ИЛЯ, вто|Х)й-вход которого связан свыходом первого элемента И, инверсный вход которого соединен с первым, входом блока сравнения, второй вход эле мента И связан с первым выходом распределителя импульсов, второй, третий и четвертый выходы которого соединены соответственно с тактовыми входа:ми регистра микрокоманд,блока сравне - . иия и.регистра адреса,установочный вход которого соединен с входом начальной установки устро|1ства, управляоS ;ций и информсщионный ВХОДЫ регистра адреса соединены соответственно с управлтощим выходом блока управления переходами и вторым входом блр ка ассоциативной памяти, выход регистра MtxpoKOMaHд и выход блока сравнения являются соответственно управлякяоим и сигнальным выходгили устройства, о т л и ч а ю la е ie с я теян. |что с целью повьоаения достоверности контроля переходов, в него введены счетчик контроля и второй элемент И, причем информационный вход счетчика контроля связан с выходом блока ассоЦиативноЙ памяти, вход сброса и счетный вход счетчика контроля соединены соответственно с. выходом эле мента ИТОГ и с выходом второго эЯейен та И, первый и второй входы которого свезены соответственно с управляющюв выходов блока управления, ререходасшои первым выхбдом распределителя импульсов, выход счетчика, кон-р роля подключен к второму инфо ялационному входу блока сравнения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство с контролем переходов | 1977 |

|

SU711573A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское, свидетельство СССР ,по заявке 2954372/24,кл.С 06 F 9/22, л29.09.81 (прототип ).. | |||

Авторы

Даты

1983-05-15—Публикация

1981-12-15—Подача