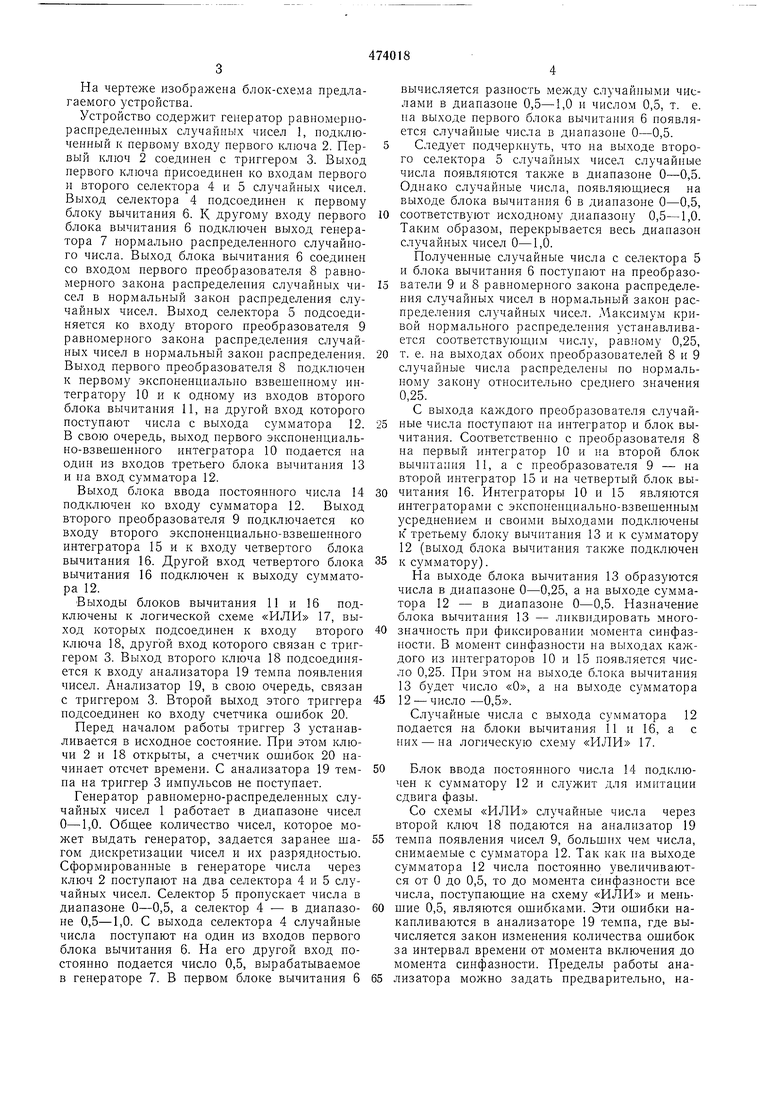

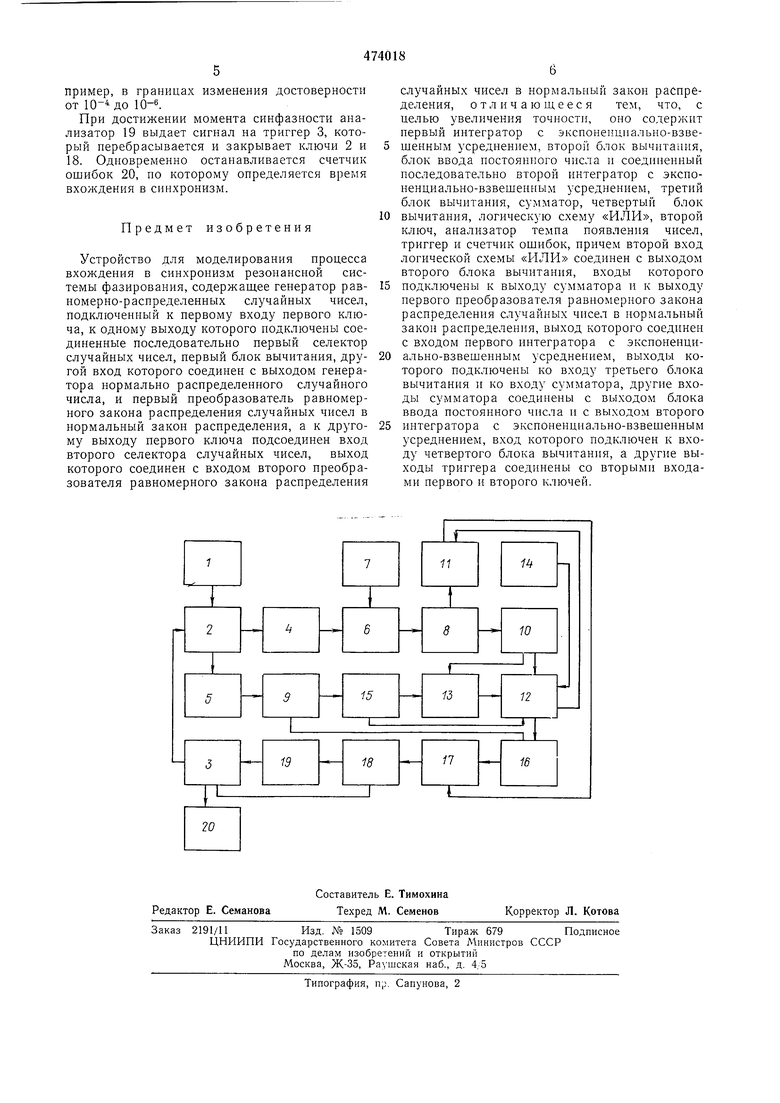

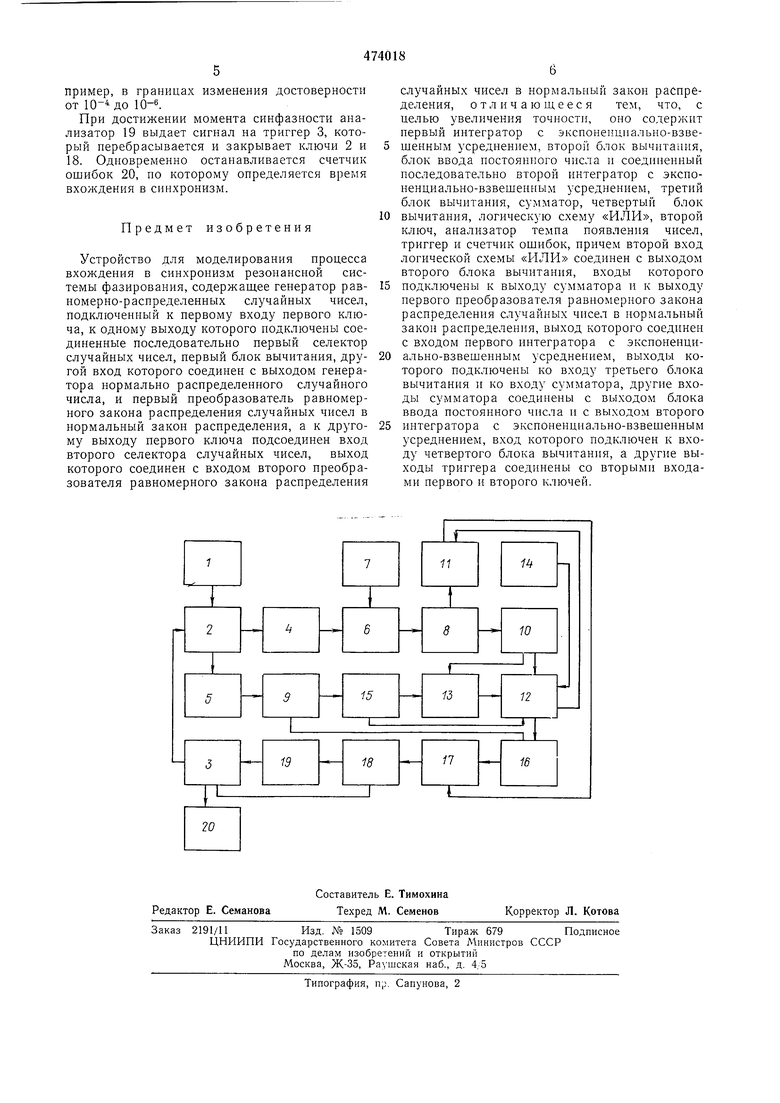

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит генератор равномернораспределенных случайных чисел 1, подключенный к первому входу первого ключа 2. Первый ключ 2 соединен с триггером 3. Выход первого ключа присоединен ко входам первого п второго селектора 4 и 5 случайных чисел. Выход селектора 4 нодсоединен к первому блоку вычитания 6. К другому входу первого блока вычитания 6 подключен выход генератора 7 нормально распределенного случайного числа. Выход блока вычитания 6 соединен со входом первого преобразователя 8 равномерного закона распределения случайных чисел в нормальный закон распределения случайных чисел. Выход селектора 5 подсоединяется ко входу второго преобразователя 9 равномерного закона распределепия случайных чисел в нормальный закон распределения. Выход первого преобразователя 8 подключен к первому экспоненциально взвешенному интегратору 10 и к одному из входов второго блока вычитания 11, на другой вход которого поступают числа с выхода сумматора 12. В свою очередь, выход первого экснонепциально-взвешенного интегратора 10 подается на один из входов третьего блока вычитания 13 и на вход сумматора 12.

Выход блока ввода постоянного числа 14 подключен ко входу сумматора 12. Выход второго преобразователя 9 подключается ко входу второго экспоненциально-взвешенного интегратора 15 и к входу четвертого блока вычитания 16. Другой вход четвертого блока вычитания 16 подключен к выходу сумматора 12.

Выходы блоков вычитания 11 и 16 подключены к логической схеме «ИЛИ 17, выход которых подсоединен к входу второго ключа 18, другой вход которого связан с триггером 3. Выход второго ключа 18 подсоединяется к входу анализатора 19 темпа появления чисел. Анализатор 19, в свою очередь, связан с триггером 3. Второй выход этого триггера подсоединен ко входу счетчика ошибок 20.

Перед началом работы триггер 3 устанавливается в исходное состояние. При этом ключи 2 и 18 открыты, а счетчик ошибок 20 начинает отсчет времени. С анализатора 19 темпа на триггер 3 импульсов не поступает.

Генератор равномерно-распределенных случайных чисел 1 работает в диапазоне чисел О-1,0. Общее количество чисел, которое может выдать генератор, задается заранее шагом дискретизации чисел и их разрядностью. Сформированные в генераторе числа через ключ 2 ноступают на два селектора 4 и 5 случайных чисел. Селектор 5 пропускает числа в диапазоне О-0,5, а селектор 4 - в диапазоне 0,5-1,0. С выхода селектора 4 случайные числа поступают на один из входов первого блока вычитания 6. На его другой вход постоянно подается число 0,5, вырабатываемое в генераторе 7. В первом блоке вычитания 6

вычисляется разность между случайными числами в диапазоне 0,5-1,0 и числом 0,5, т. е. на выходе первого блока вычитания 6 появляется случайные числа в диапазоне О-0,5. Следует подчеркнуть, что на выходе второго селектора 5 случайных чисел случайные числа появляются также в диапазоне О-0,5. Однако случайные числа, появляющиеся на выходе блока вычитания 6 в диапазоне О-0,5,

соответствуют исходному диапазону 0,5-1,0. Таким образом, перекрывается весь диаиазон случайных чисел О-1,0.

Полученные случайные числа с селектора 5 и блока вычитания 6 ностунают на преобразователи 9 и 8 равномерного закона распределения случайных чисел в нормальный закон распределения случайных чисел. д 1аксимум кривой нормального распределепия устанавливается соответствующим числу, равному 0,25,

т. е. на выходах обоих преобразователей 8 и 9 случайные числа распределены по нормальному закону относительно среднего значения 0,25. С выхода каждого преобразователя случайные числа поступают на иптегратор и блок вычитания. Соответственно с преобразователя 8 на первый интегратор 10 и на второй блок вычитания 11, а с преобразователя 9 - на второй интегратор 15 и на четвертый блок вычитания 16. Интеграторы 10 и 15 являются интеграторами с экспопенциальпо-взвещенным усреднением и своими выходами подключены ктретьему блоку вычитания 13 и к сумматору

12(выход блока вычитания также подключен к сумматору).

На выходе блока вычитания 13 образуются числа в дианазоне О-0,25, а па выходе сумматора 12 - в диапазоне О-0,5. Назначение блока вычитания 13 - ликвидировать многозначность при фиксировапии момента синфазности. В момент синфазности на выходах каждого из интеграторов 10 и 15 появляется число 0,25. При этом на выходе блока вычитания

13будет число «О, а на выходе сумматора 12 - число-0,5.

Случайные числа с выхода сумматора 12 подается на блоки вычитания 11 и 16, а с них - иа логическую схему «ИЛИ 17.

Блок ввода ностояиного числа 14 подключен к сумматору 12 и служит для имитации сдвига фазы.

Со схемы «ИЛИ случайные числа через второй ключ 18 подаются на анализатор 19

темна иоявления чисел 9, больших чем числа, снимаемые с сумматора 12. Так как на выходе сумматора 12 числа постоянно увеличиваются от О до 0,5, то до момента синфазности все числа, поступающие на схему «ИЛИ и меньшие 0,5, являются ошибками. Эти ошибки накапливаются в анализаторе 19 темпа, где вычисляется закон изменения количества ошибок за интервал времени от момента включения до момента синфазности. Пределы работы анализатора можно задать предварительно, на

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования стартстопной системы поэлементной синхронизации | 1973 |

|

SU478328A1 |

| Устройство для моделирования процесса синхронизации коротковолновой радиолинии | 1982 |

|

SU1073892A1 |

| Анализ случайных процессов | 1974 |

|

SU526908A1 |

| Устройство для перемножения функций распределения | 1987 |

|

SU1474677A1 |

| Статический анализатор | 1985 |

|

SU1305731A1 |

| Адаптивный статический анализатор | 1985 |

|

SU1305730A1 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 1991 |

|

RU2012052C1 |

| Устройство для моделирования отказов с изменяющимся временным шагом | 1981 |

|

SU991433A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

Авторы

Даты

1975-06-15—Публикация

1973-01-08—Подача