Изобретение относится к автоматике.

Известен имлульспый фазовращатель, содержащий генератор опорных колебаний, соединенный с первым делителем частоты, вентиль, выход которого соединен со счетным входом второго делителя частоты, выход которого и установочные входы, кроме первого, подключены к первому входу и выходам ключевого перезаписывающего блока соответственно, управляющие входы ключевого блока соеди 1епы с выходами реверсивного счетчика.

Однако известное устройство характеризуется изменением фазы выходного сиг}1ала в ограниченном интервале.

Целью изобретения является расщирение интервала управления фазой (выходного сигнала.

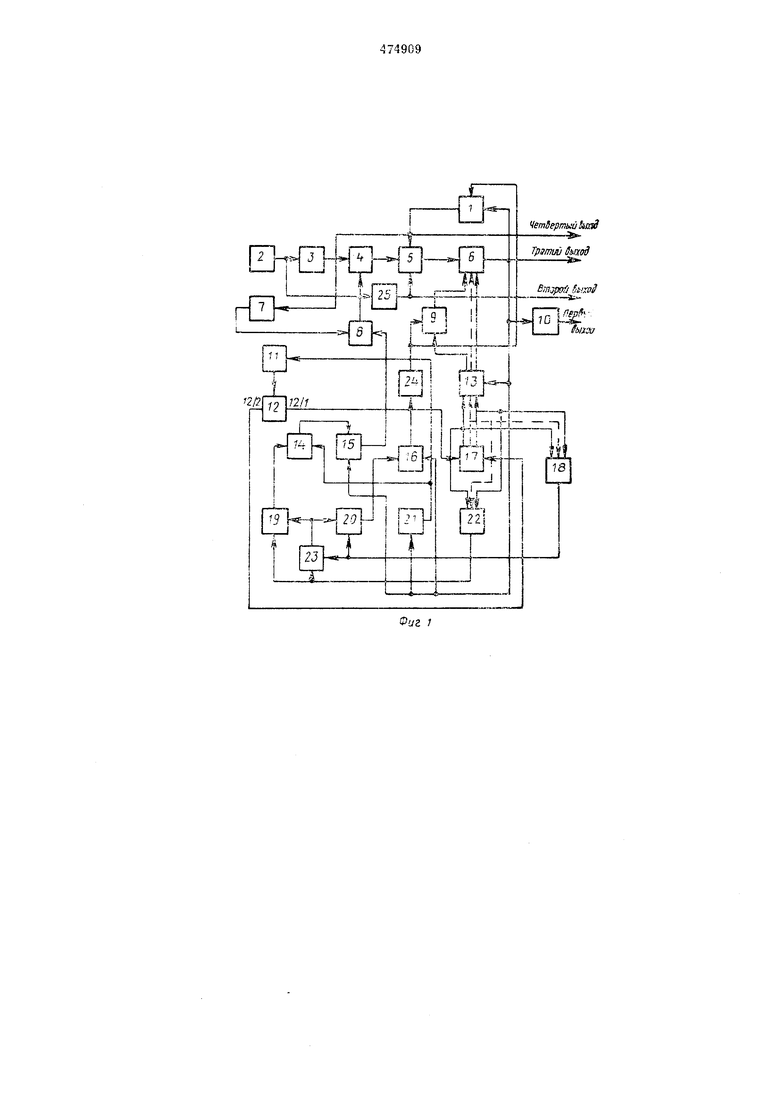

Для этого в фазовращатель введены три линии задержки, щееть вентилей, три триггера, управляющее устройство, третий делитель частоты, устройство, суммирующее производные, два дещифратора и два умножителя, причем второй вентиль включен между выходом второго делителя частоты и запирающим входо.м первого вентиля, отпирающий вход которого подключен к выходу третьего вентиля, счетный вход которого соединен с выходом первого делителя частоты, а управляющий вход - с ВЫХОДОМ первого триггера,

первый вход которого через первую лишпо задерЖКи подсоединен к выходу первого делителя частоты, а второй вход - к выходу четвертого вентиля, счетный вход которого соединен с выходом второго делителя частоты а у;фавляющий вход-свыходо.м .второго триггера, первый вход которого подключен к выходу пятого :вентиля, а второй вход - к выходу второй линии задержки, вход которой соединен с выходо.м второго делителя частоты, при этом выходы реверсивного счетчика подключены к входам первого и второго дешифраторов, выходы которых подключены к входам устройства, суммирующего производные, н входам пятого и щестого вент; лей, вторые входы которых соединены с выходом устройства, суммирующего производные, выход щестого вентиля подсоединен к первому входу третьего триггера, второй вход которого соеди;1ен с выходом второго делителя, а выход - через третью линию задержки с управляющими входами второго и седьмого вентилей, из 1которых последний включен между первым выходом ключевого перезаписывающего блока и Первым установочным входом второго делнтеля частоты, причел: вход )правля ощего устройства управления через TpeTiHi делитель частоты подключен к выходу второй задержки, а выход - к входу реверсивного счетчика, первый умножитель частоты иодключен к выходу второго делителя частоты, а второй умножитель частоты включен между выходом генератора опорных колебаний и счетным входом первого вентиля.

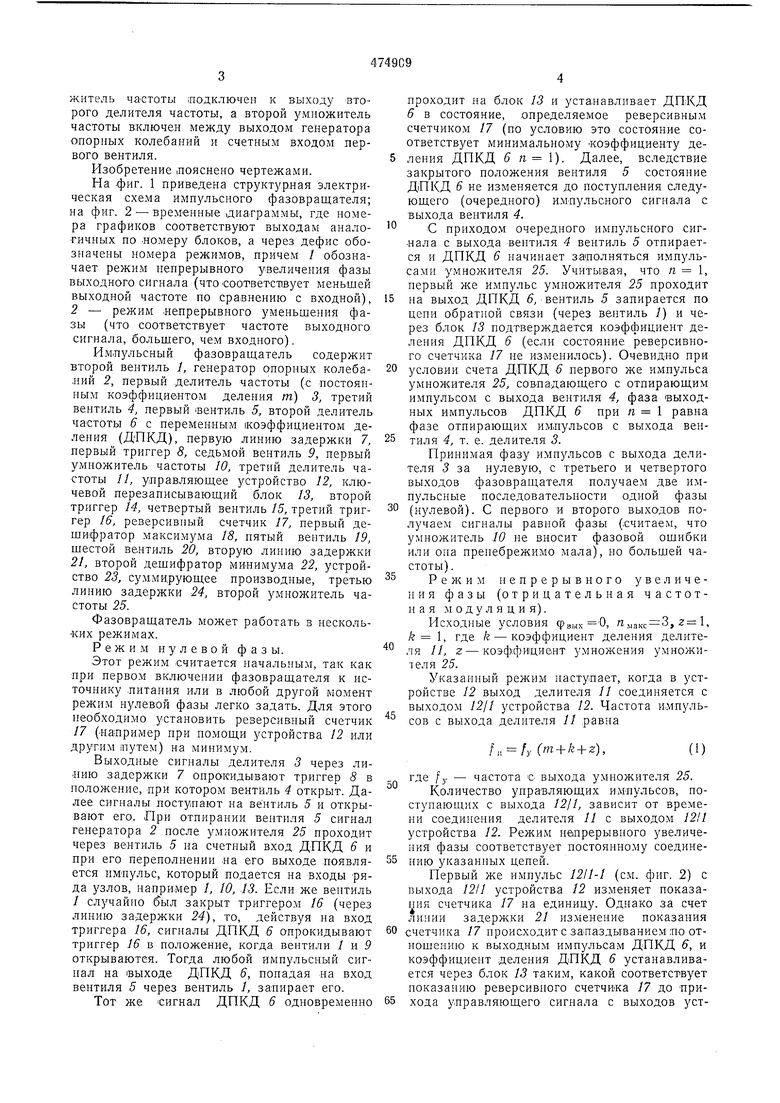

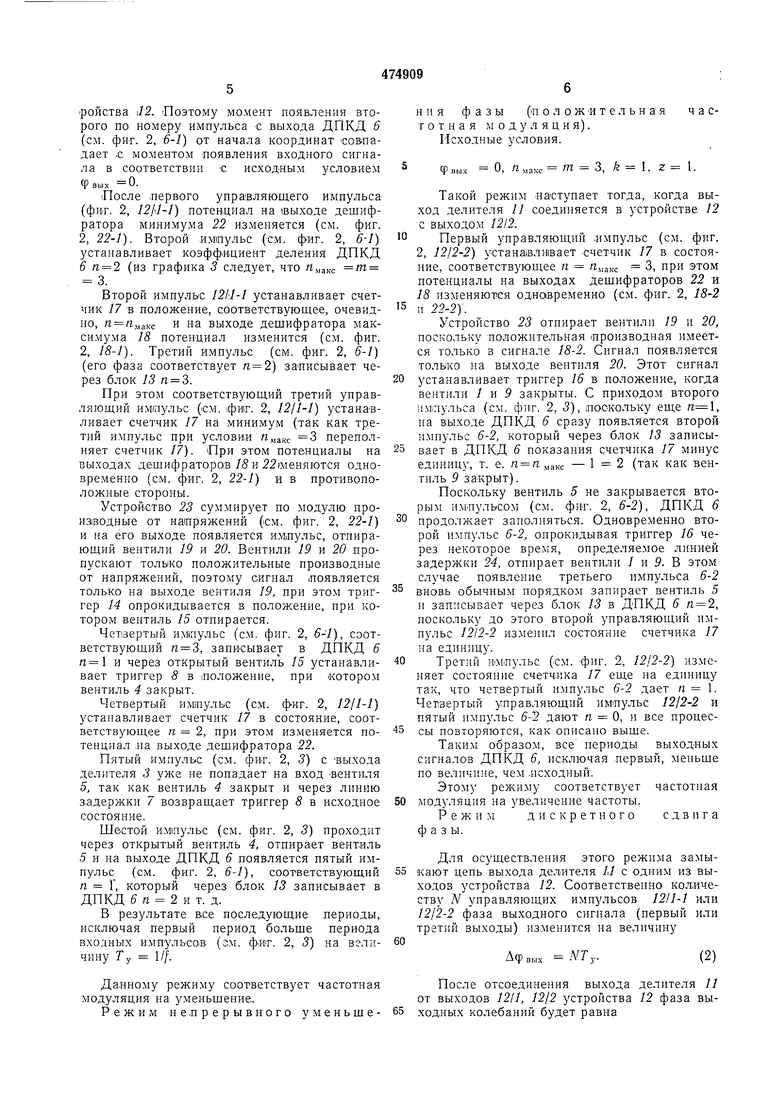

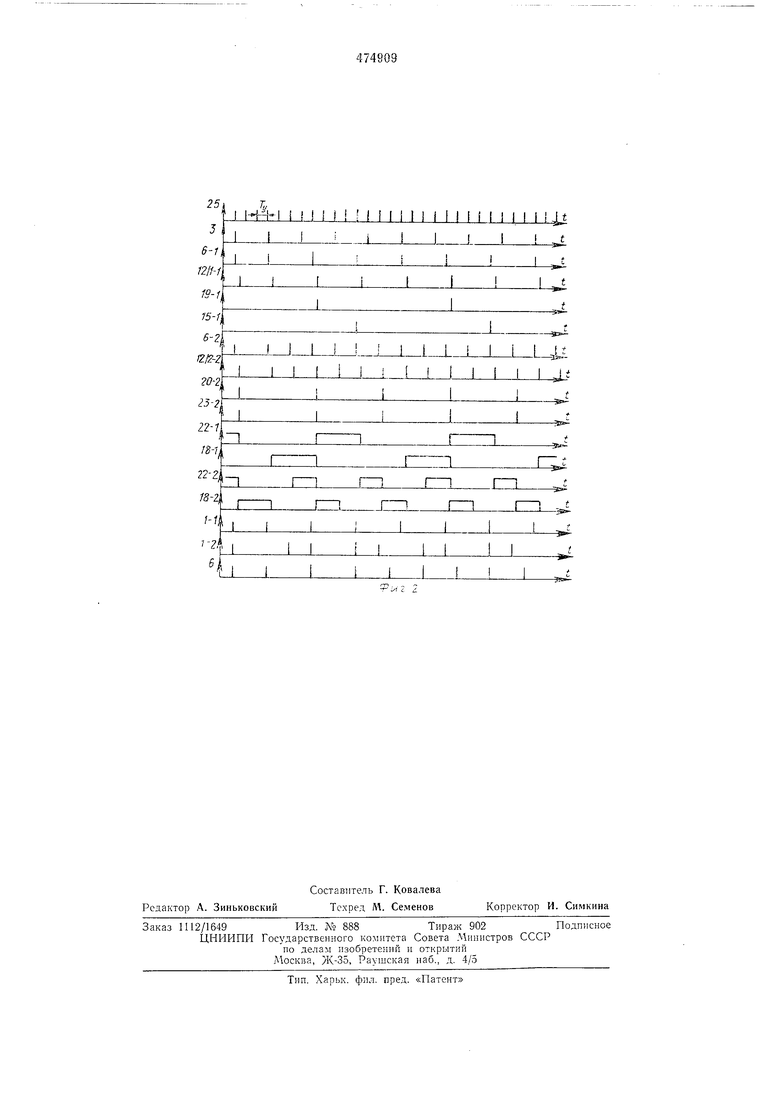

Изобретение лояснено чертежами. На фиг. 1 приведена структурная электрическая схема импульсного фазовращателя; на фиг. 2 - временные диаграммы, где номера графиков соответствуют выходам аналогичных по Номеру блоков, а через дефис обозначены номера режимов, причем / обозначает режим непрерывного увеличения фазы выходного сигнала (чтосоответст1вует меньшей выходной частоте по ,сра1внению с входной), 2 - режим .непрерывного уменьшения фазы (что соответствует частоте выходного сигнала, большего, чем входного).

Имлульсный фазовраш;атель содержит второй вентиль 1, генератор опорных колебалий 2, первый делитель частоты (с постоянным коэффициентом деления т) 3, третий вентиль 4, первый вентиль 5, второй делитель частоты 6 с переменным коэффициентом деления (ДПКД), первую линию задержки 7, первый триггер 8, седьмой вентиль 9, первый умножитель частоты 10, третий делитель частоты II, управляющее устройство 12, ключевой перезаписывающий блок 13, второй триггер 14, четвертый вентиль 15, третий триггер 16, реверсивный счетчик 17, первый дешифратор максимума 18, пятый вентиль 19, шестой вентиль 20, вторую линию задержки 21, второй дешифратор минимума 22, устройство 23, сумми,руюш,ее производные, третью линию задержки 24, второй умножитель частоты 25.

Фазовращатель может работать в нескольких режимах.

Режи.м нулевой фазы. Этот режим считается начальным, так как при первом включении фазовращателя к источнику .питания или в любой другой момент режим нулевой фазы легко задать. Для этого необходимо установить реверсивный счетчик 17 (например прн помощи устройства 12 или другим тутем) на минимум.

Выходные сигналы делителя 3 через ли.нию задержки 7 опрокидывают триггер 8 в положение, при котором вентиль 4 открыт. Далее сигналы поступают на вентиль 5 и открывают его. При отпирании вентиля 5 сигнал генератора 2 после умножителя 25 проходит через вентиль 5 на счетный вход ДПКД 6 и при его переполнении .на его выходе появляется импульс, который подается на входы ряда узлов, например 1, 10, .13. Если же вентиль / случайно ыл закрыт триггером 16 (через линию задержки 24), то, действуя на вход триггера 16, сигналы ДПКД 5 опрокидывают триггер 16 в положение, когда вентили 1 н 9 открываются. Тогда любой импульсный сигнал на выходе ДПКД б, попадая на в.код вентиля 5 через вентиль /, запирает его. Тот же Сигнал ДПКД 6 одновременно

проходит на блок 13 и устанавливает ДПКД 6 в состояние, .определяемое реверсивным счетчиком 17 (по условию это состояние соответствзет мини.мальному коэффициенту деления ДПКД 6 п 1). Далее, вследствие закрытого положения вентиля 5 состояние ДПКД 6 не изменяется до поступления следующего (очередного) илтульсного сигнала с выхода вентиля 4.

С приходом очередного импульсного сиг.нала с выхода вентиля 4 вентиль 5 отпирается и ДПКД 6 начинает заполняться импульсами умножителя 25. Учитьшая, что л 1, первый же импульс умножителя 25 проходит

на выход ДПКД б, вентиль 5 запирается по цепи обратной связи (через вентиль 1) и через блок /5 подтверждается коэффициент деления ДПКД 6 (если состояние реверсивного счетчика 17 не изменилось). Очевидно при

условии счета ДПКД 6 первого же импульса умнол ителя 25, совла.дающего с отпирающим импульсом с выхода вентиля 4, фаза выходных импульсов ДПКД 6 при п 1 равна фазе отпирающих имлульсов с выхода вентиля 4, т. е. делителя 3.

Принимая фазу импульсов с выхода делителя 3 за нулевую, с третьего и четвертого выходов фазовращателя получаем две импульсные последовательности одной фазы

(нулевой). С первого и второго выходов получаем сигналы равной фазы (считаем, что умножитель 10 не вносит фазовой ошибки или она пренебрежимо мала), но больщей частоты).

непрерывного увеличения фазы (отрицательная частотная модуляция).

Исходные условия , „3 3, 2 1,

k , где /е - коэффициент деления делителя //, Z-коэффициент умножения умножителя 25.

Указанный режим наступает, когда в устройстве 12 выход делителя // соединяется с выходом 12/1 устройства 12. Частота и.мпульсов с выхода делителя 11 равна

(I)

/и А.- (m + k + z),

где fy - частота с выхода умножителя 25.

К оличество управляющих им-пульсов, поступающих с выхода 12/1, зависит от времени соединения делителя 11 с выходом устройства 12. Режим непрерывного увеличения фазы соответствует постоянному соединеиию указанных цепей.

Первый же импульс 1211-1 (см. фиг. 2) с выхода 12/1 устройства 12 изменяет показания счетчика 17 на единицу. Однако за счет лннни задержки 21 изменение показания

четчика /7 происходите запаздыванием:по отношению к выходным импульсам ДПКД 6, и коэффициепт деления ДПКД б устанавливается через блок 13 таким, какой соответствует показанию реверсивного счетчика 17 до прихода управляющего сигнала с выходов устройства 1/2. Поэтому момент появления второго по номеру импульса € выхода ДПКД 6 (см. фИГ. 2, 6-1) от начала координат совпадает ,с моментом появления входного сигнала в соответствии € исходным условием

фвых 0.

После .первого управляющего импульса (фиг. 2, ) потенциал на (выходе дешифратора минимума 22 изменяется (см. фиг. 2, 22-1). Второй имтульс (см. фИг. 2, 6-1) устанавливает коэффициент деления ДПКД 6 п 2 (из графика 3 следует, что «макс т 3.

Второй импульС 12/J-1 устанавливает счетчик 17 в положение, соответствуюи1ее, очевидно, л п.,,акс и на выходе дешифратора максимума 18 потенциал изменится (см. фиг. 2, 18-1). Третий импульс (см. фиг. 2, 6-1) (его фаза соответствует п 1) записывает через блок 13 п 3.

При этом соответствующий третий управляющий им1пульс (см. 1ФИ1Г. 2, 12/1-1) устанавливает счетчик 17 на минимум (так как третий импульс при условии Плате 3 переполняет счетчик /7). При этом потенциалы на выходах дешифраторО(В/5 и 22|меняют€я одновременно (см. фиг. 2, 22-1) и в противоположные стороны.

Устройство 23 суммирует по модулю производные от напряжений (см. фиг. 2, 22-7) и на его выходе появляется импульс, отпирающий вентили 19 и 20. Вентили 19 и 20 пропускают только положительные производные от напряжений, поэтому сигнал .появляется только на выходе вентиля 19, при этом триггер 14 опрокидывается в положение, при котором вентиль 15 отпирается.

Четвертый имиульс (см. фиг. 2, 6-1), соответствующий п 3, записывает в ДПКД 6 п и через открытый вентиль 15 устанавливает триггер 8 в 1положение, при котором вентиль 4 закрыт.

Четвертый илшульс (см. фиг. 2, 12/1-1) устанавливает счетчик 17 в состояние, соответствующее п 2, при этом изменяется потенциал .на выходе дешифратора 22.

Пятый импульс (см. фиг. 2, 3) с выхода делителя Л уже не попадает на вход вентиля 5, так как вентиль 4 закрыт и через линию задержки 7 возвращает триггер 8 в исходное состояние.

Шестой им1пульс (см. фиг. 2, 3) проходит через открытый вентиль 4, отпирает вентиль 5 и на выходе ДПКД 6 появляется пятый импульс (см. фиг. 2, 6-1), соответствующий л Г, который через блок 13 записывает в ДПКД б п 2 и т. д.

В результате все последующие периоды, исключая первый период больше периода входных импульсоБ (см. ф-ит. 2, 3) на величину Ту lf.

Да.нному режиму соответствует частотная модуляция на уменьшение.

Режим не,прерывного уменьшения фазы (л о л о ж И т е л ь н а я

ч а стот на я модуляция). Исходные условия.

0, п макс г 3, k I, Z 1.

фвь

Такой режим наступает тогда, когда выход делителя 11 соединяется в устройстве 12 с выходом /2/2.

Первый управляющий .импульс (см. фиг. 2, 12/2-2) устана1вли1вает счетчик 17 в состояние, соответствующее п 3, при этом потенциалы на выходах дешифраторов 22 и 18 изменяются одновременно (см. фиг. 2, 18-2

и 22-2).

Устройство 23 отпирает вентили 19 и 20, поскольку положительная 1производная 1меется только в сигнале 18-2. Сигнал появляется только на вы.ходе вентиля 20. Этот сигнал

устанавливает триггер 16 в положение, когда вентили / и Р закрыты. С приходом второго имаульса (см. фиг. 2, 3), поскольку еще п, на выходе ДПКД 6 сразу появляется второй импульс 6-2, который через блок 13 записывает в ДПКД 6 показания счетчика 17 минус единицу, т. е. п п „акс - (так как вентиль 9 закрыт).

Поскольку вентиль 5 не закрывается вторым импульсом (см. фиг. 2, 6-2), ДПКД 6

продолжает заполняться. Одновременно второй импульс 6-2, опрокидывая триггер 16 через некоторое время, определяемое линией задержки 24, отпирает вентили 1 и 9. В этом случае появление третьего импульса 6-2

вновь обычным порядком запирает вентиль 5 и записывает через блок 13 в ДПКД 6 /1 2, поскольку до этого второй управляющий импульс /2/2-2 из.менил состояние счетчика 17 на един1щу.

Третий импульс (см. фиг. 2, 12/2-2) изменяет состояние счетч, 17 еще на единицу так, что четвертый импульс 6-2 дает п . Четвертый управляющий импульс 12/2-2 и пятый импульс 6-12 дают п О, и все процессы повторяются, как описано выше.

Таким образом, все периоды выходных сигналов ДПКД 6, исключая первый, меньше по величине, чем исходный.

Этому режиму соответствует частотная

модуляция на увеличение частоты.

Режим дискретного сдвига фазы.

Для осуществления этого режима замыкают цепь выхода делителя // с одним из выходов устройства /2. Соответственно количеству Л управляющих импульсов 12/1-1 или /2/2-2 фаза выходного сигнала (первый или третий выходы) изменится на величину

АФЗЫ.Х ЛТ,.(2)

После отсоединения выхода делителя // от выходов 12/1, 12/2 устройства /2 фаза выходных колебаний будет равна вых Фвых.о - у где знак плюс соответствует управлению по цепи 1211 устройства 12, а знак минус - по цепи 1212, Фвых.о начальная фаза выходных сигналов. Частота выходных сигналов после размыкания цепей равна частоте опорных колебаний. В качестве примера показан случай, когда ,при Фвых.о О (см. . 2, 6, первый нмпульс) Z 1, п ,,акс - m 3, 1, на вход счетчика 17 было подано два управляющих импульса по цепи 1211 устройства 12. При этом Афзых 2r,, а начиная с четвертого периода частота выходного сигнала равна частоте опорного сигнала (см. фиг. 2, 3). После умножителя 10 частота выходного сигнала, очевидно, будет равна частоте опорного сигнала (см. фит. 4, 25). При Z 1 фаза сигналов с третьего выхода фазовращателя изменяется на долю периода с каждым управляющим импульсом, а с Первого выхода - на один период. Поэтому, если фазовращатель должен обеспечивать управление фазой с дискретностью, меньщей .периода Го генератора 2, коэффициент умножения Z должен быть больще единицы. В предельном случае, когда т , а 2 йцакс дискретность управления фазой выходного сигнала по отнощению к фазе опорного генератора 2 будет равна Т о Of вых Управление фазовращателем можно вести не только импульсами посредством устройства 12, но и КОДОВЫМИ ко.мбинациями через счетчик 17. При выборе т, z, п„акс в любом случае необходимо выполнить условие т. г л„аксУчитывая, что фвых линейно связано с /V (см. формулу (.2), (Предложенный фазо вращатель можно .применить как преобразо ватель числа импульсов в фазу. Точность пре образования, KaiK видно из формулы (3), за виоит от постоянства начальной фазы фвых.о и стабильности генератора 2. (Предмет изобретения Импульсный фазовращатель, содержащий енератор опорных колебаний, соед 1ненный с первым делителем частоты, вентиль, выход которого соединен со счетным входом второго делителя частоты, а его выход и уста1Ювочные входы, кро,ме первого, подключены к первому входу и выходам ключевого перезаписывающего блока соответственно, управляющее входы ключевого перезаписывающего блока соединены с выходами реверсивного счетчика, отличающийся тем, что, с целью расширения интервала управления фазой выходного сигнала, в него введены три линии задержки, щесть вентилей, три триггера, управляющее устройство, третий делитель частоты, устройство, суммирующее производные, два дешифратора -и два умножителя, приче.м второй вентиль включен между выходом второго делителя частоты и запираюп им входом первого вентиля, отпирающий вход которого подключен к выходу третьего вентиля, а его счетный вход -соединен с выходом первого делителя частоты, приче.м управляющий вход соединен с выходом первого триггера, первый вход которого через первую линию задержки подсоединен к выходу первого делителя частоты, а второй вход - к выходу четвертого вентиля, счетный вход которого соединен с выходом второго делителя частоты, а управляющий вход - с выходом второго триггера, первый вход которого подключен к выходу пятого вентиля, а второй вход- к выходу второй линии задержки, вход которой Соединен с выходо.м второго делителя частоты, при этом выходы реверсивного счетчика подключены к входам первого и второго дешифраторов, выходы которых подключены к входам устройства, суммирующего лроизводные, и входам пятого и шестого вентилей, вторые входы которых соединены с выходом устройства, суммирующего производные, выход шестого вентиля подсоединен к первому входу третьего триггера, второй вход которого соединен с выходом второго дел.ителя, а выход - через третью линию задержки с управляющими входами второго и седьмого вентилей, из которых последний включен между первым выходом ключевого перезаписывающего блока и первым установочным входом второго делителя частоты, причем вход управляющего устройства через третий делитель частоты подключен к вгэьходу второй линии задержки, а выходы - к входам реверсивного счетчика; первый умножитель частоты подключен к выходу второго делителя частоты, а второй умножитель частоты включен между выходом генератора опорных колебаний ,и счетным входом первого вентиля.

Eh€}

Четйертый iosi

71 --

Трзтий

5j

n I T

Bmjpfffj &/./

-ii-j.

rti i|

FL

I /4//Я/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Двухканальный стробоскопический осциллограф | 1980 |

|

SU879479A2 |

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| Цифроаналоговый генератор периодических функций | 1987 |

|

SU1418685A1 |

| Умножитель частоты | 1982 |

|

SU1061236A1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1990 |

|

SU1823137A1 |

| Умножитель частоты | 1983 |

|

SU1167692A2 |

| Устройство для поверки преобразователей фаза-код | 1990 |

|

SU1774298A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

.«c.

f5 L

5

2J

П

4и4

дИ

78

J

Li.

r

25

LJ±ifh± UJ

5 I 6-li 12IH 19-1,

IZI2-Z 0-2 23-2

22-1

ZL B-n

22-2

I3

18-Zi

1I -U

M i i I I I J.t

JZ

n

-dl

.ГЦ

.EH

Авторы

Даты

1975-06-25—Публикация

1972-11-29—Подача