3

леиии, схем задержки, схем «И, «ИЛИ, причем информационные нходи блока связаны с информационными входами узла jiej-HCTpaiuni повторений наборов, вход разрешения нерестройкн блока связан с входом разрешения нерестройки узла регистрации новторений наборов, входом сброса реверсивного счетчика и через нервую схему «ИЛИ с входом «Сложение триггера уиравления, а второй вход нервой схемы «ИЛИ соединен с входом синхронизации блока через нервую схему «И, второй вход которой связан с выходом «Вычитание триггера уиравления, вход унравления блоком соединс с входом «В111читание триггера уи 1авления через вторую схему «И, второй вход которой через нервую схему задержки соединен с выходом узла регистрации цовторений наборов, выходы триггера управления через вторую и третью схемы задержки связаны с входами управления реверсивного счетчика, выход переполнения которого связан с выходом блока, а счетный вход соединен с выходом узла регистрации повторений наборов через вторую схему «ИЛИ, второй вход которой через нервую схему «И соединен с входом синхронизации блока.

Блок запоминания запретных наборов состоит из узла регистрации повторений наборов, схемы задержки и схемы «И, причем информационные входы узла регистрации повторений наборов связаны с информационными входами блока, вход синхронизации блока связан с входом разрешения перестройки узла регистрации повторений наборов, вход которого связан с выходом блока через схему «И, второй вход которой через схему задержки связан с входом сигнализации о запретном наборе.

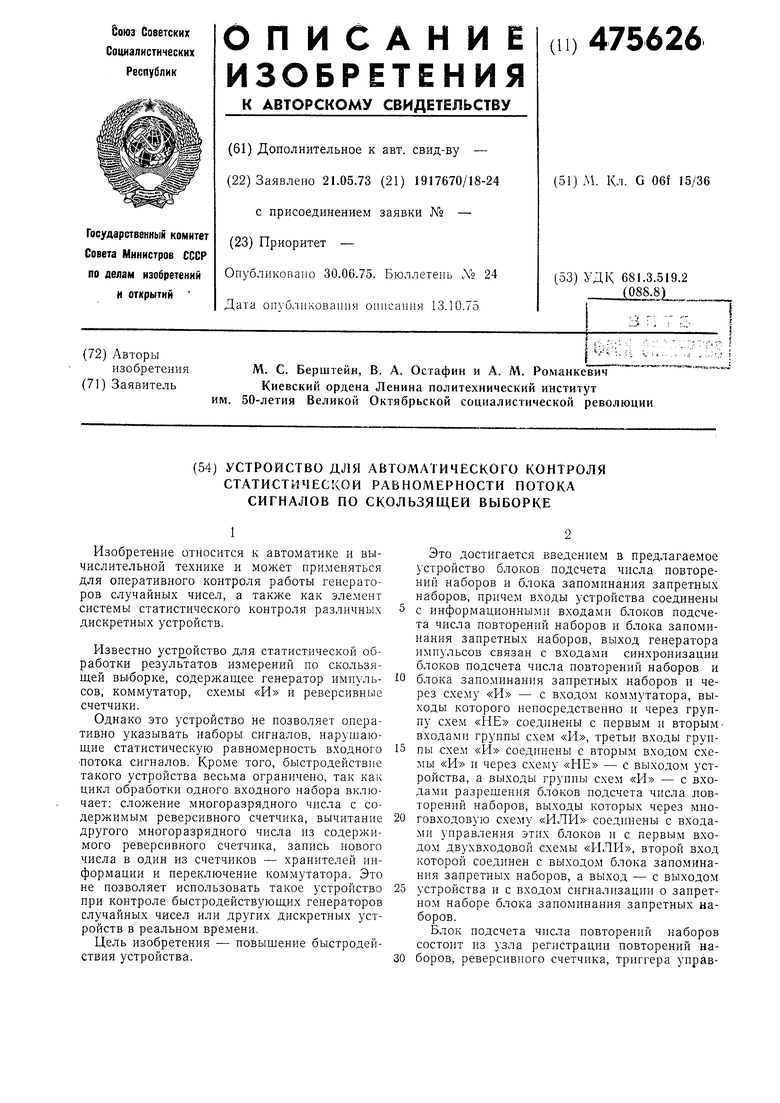

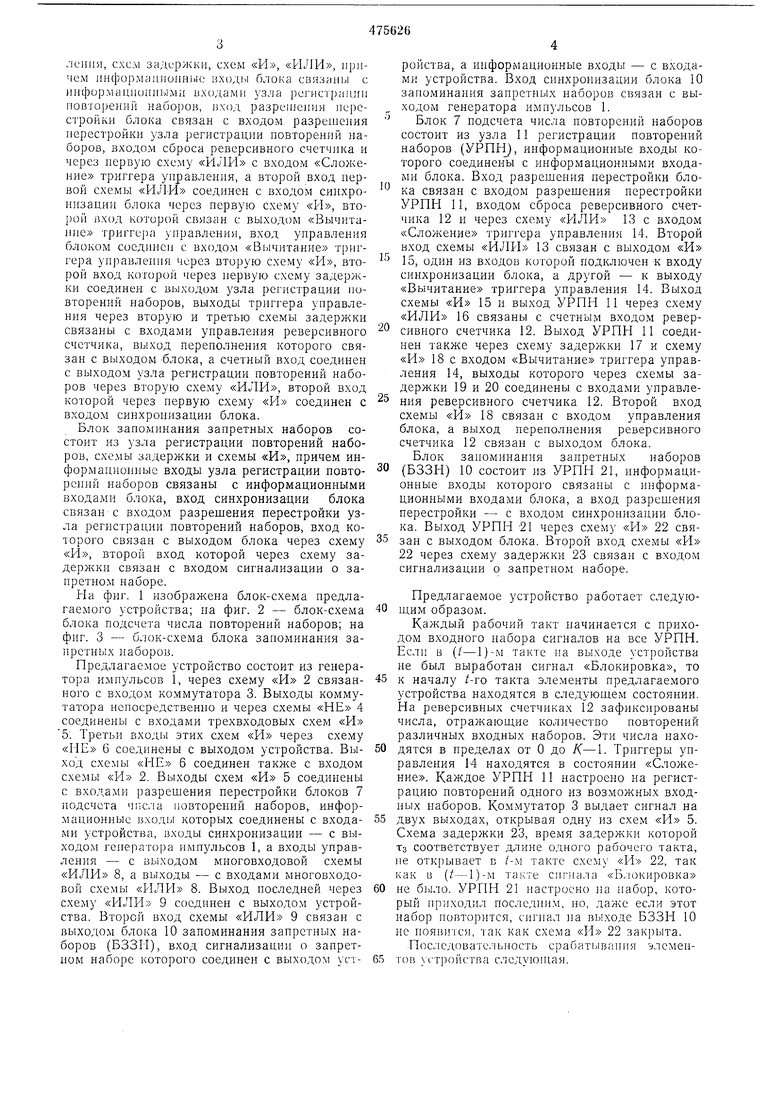

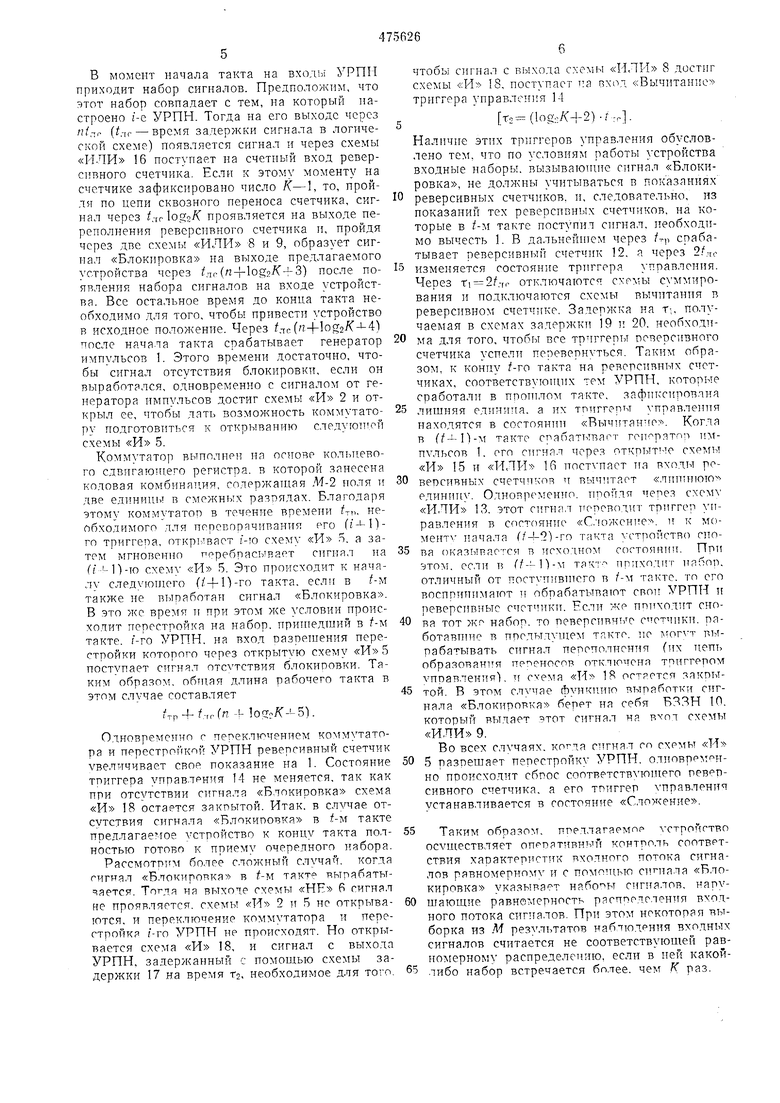

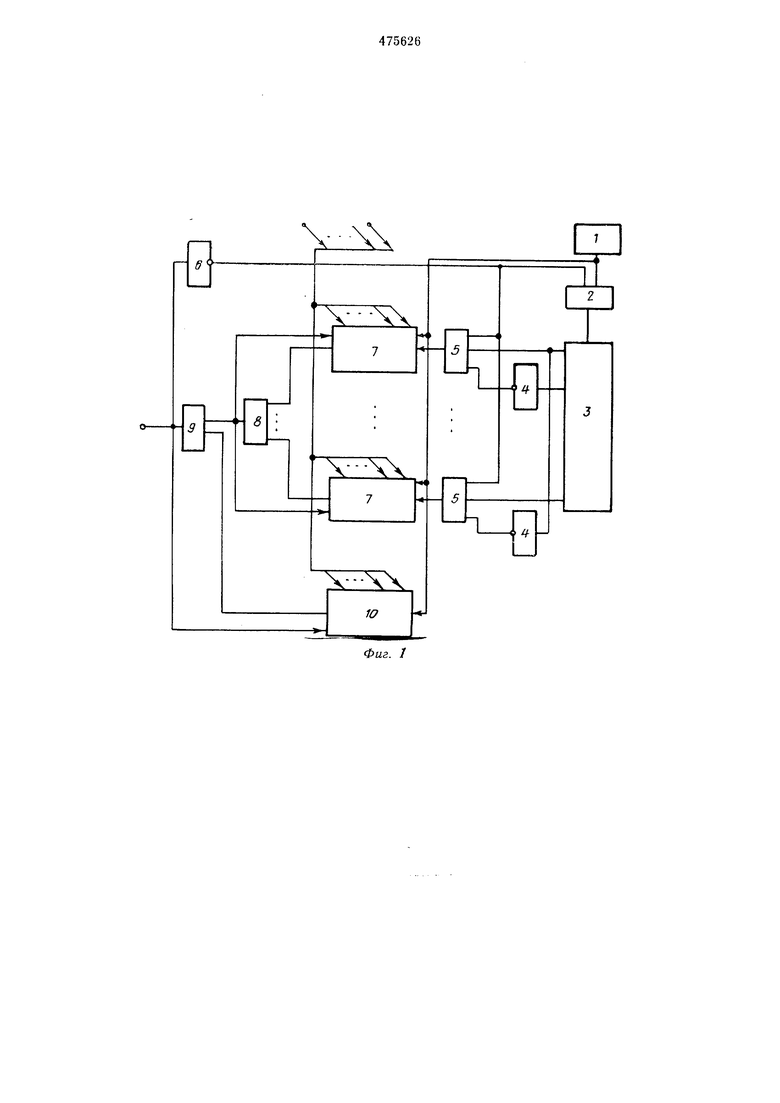

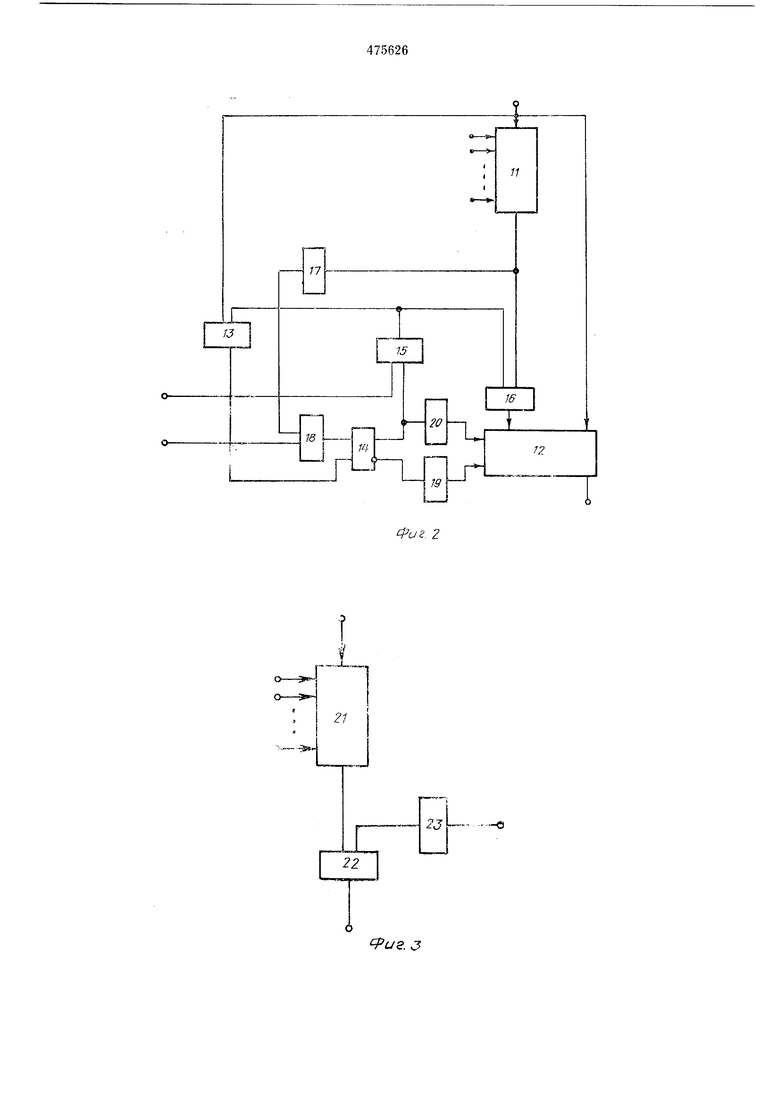

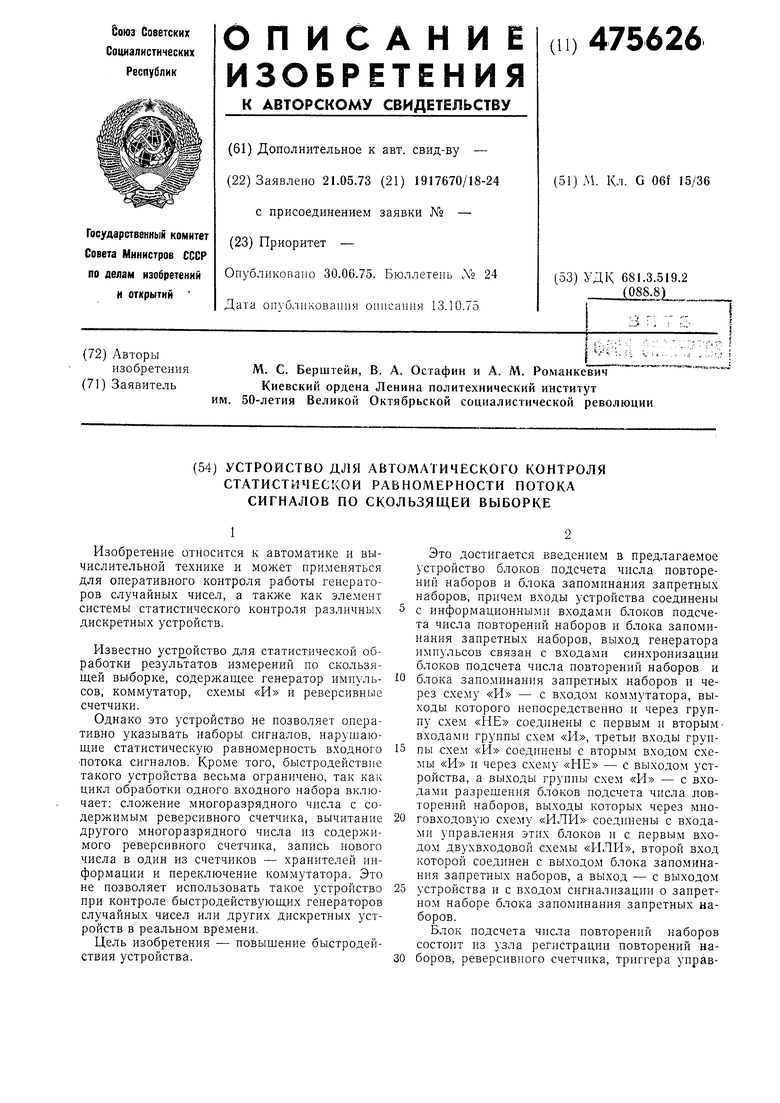

На фиг. 1 изображена блок-схема предлагаемого устройства; па фиг. 2 - блок-схема блока подсчета числа повторений наборов; на фиг. 3 - блок-схема блока запоминания запретных наборов.

Предлагае.мое устройство состоит из генератора импульсов 1, через схему «И 2 связанного с входом коммутатора 3. Выходы коммутатора непосредственно и через схемы «НЕ 4 соединены с входами трехвходовых схем «И 5. Третьи входы этих схем «И через схему «НЕ 6 соединены с выходом устройства. Выход схемы «НЕ 6 соединен также с входом схемы «И 2. Выходы схем «И 5 соединены с входами разрешения перестройки блоков 7 подсчета числа повторений наборов, информационные входы которых соединены с входами устройства, входы синхронизации - с выходом генератора импульсов 1, а входы управления - с выходом многовходовой схемы «ИЛИ 8, а выходы - с входами многовходовой схемы «ИЛИ 8. Выход последней через схему «ИЛИ 9 соединен с выходом устройства. Второй вход схемы «ИЛИ 9 связан с выходом блока 10 запоминания запретных наборов (БЗЗИ), вход сигнализации о запретном наборе которого соединен с выходом устройства, а информационные входы - с входами устройства. Вход синхронизации блока 10 запоминания занретных наборов связан с выходом генератора импульсов 1. Блок 7 подсчета числа повторений наборов состоит из узла 11 регистрации повторений наборов (УРИН), информационные входы которого соединены с информационными входами блока. Вход разрешения нерестройки блока связан с входом разрешения перестройки УРНН 11, входом сброса реверсивного счетчика 12 и через схему «ИЛИ 13 с входом «Сложение триггера управления 14. Второй вход схемы «ИЛИ 13 связан с выходом «И

15, один из входов которой подключен к входу синхронизации блока, а другой - к выходу «Вычитание триггера управления 14. Выход схемы «И 15 и выход УРНН 11 через схему «ИЛИ 16 связаны с счетны.м входом реверсивного счетчика 12. Выход УРНН 11 соединен также через схему задержки 17 и схему «И 18 с входом «Вычитание триггера управления 14, выходы которого через схемы задержки 19 и 20 соединены с входами управления реверсивного счетчика 12. Второй вход

схемы «И 18 связан с входом управления

блока, а выход переполнения реверсивного

счетчика 12 связан с выходом блока.

Блок запоминания запретных наборов

(БЗЗН) 10 состоит из УРНН 21, информационные входы которого связаны с информационными входами блока, а вход разрешения перестройки - с входом синхронизации блока. Выход УРНН 21 через схему «И 22 связан с выходом блока. Второй вход схемы «И 22 через схему задержки 23 связан с входом сигнализации о запретном наборе.

Нредлагаемое устройство работает следуюшим образом.

Каждый рабочий такт начинается с приходом входного набора сигналов на все УРНН. Если в (/-1)-м такте на выходе устройства не был выработан сигнал «Блокировка, то

к началу /-го такта элементы предлагаемого устройства находятся в следуюше.м состоянии. На реверсивных счетчиках 12 зафиксированы числа, отражающие количество повторений различных входных наборов. Эти числа находятся в пределах от О до К-1. Триггеры управления 14 находятся в состоянии «Сложение. Каждое УРНН И настроено на регистрацию повторений одного из возможных входных наборов. Коммзтатор 3 выдает сигнал на

двух выходах, открывая одну из схем «И 5. Схема задержки 23, время задержки которой Тз соответствует длине одного рабочего такта, не открывает с /-м такте схему «И 22, так как в (/-1)-м cnriuna «Б юкировка

пе было. УРНН 21 настроено па набор, который приходил последним, }ю, даже если этот набор повторится, сигнал па выходе БЗЗН 10 не появится, так как схема «И 22 закрыта. Носледовательпость срабат1лвапия элементов чтройства следующая.

В момент начала такта на входы УРПМ приходит набор сигналов. Предположим, что этот набор совпадает с тем, на который настроено г-е УРПН. Тогда на его выходе через ni.r (trie - время задержки сигнала в логической схеме) появляется сигнал и через схемы «ИЛИ 16 поступает на счетный вход реверсивного счетчика. Если к этому моменту на счетчике зафиксировано число К-1, то, нройля по цепи сквозного переноса счетчика, сигнал через глг проявляется на выходе переполнения реверсивного счетчика и, пройдя через две схемы «ИЛИ 8 и 9, образует сигнал «Блокировка на выходе предлагаемого устройства через t,ic(n-{- og2K-3 после появления набора сигналов на входе устройства. Все остальное время до конца такта необходимо для того, чтобы привести устройство в исходное положение. Через /лс («+log2 --4-) после начала такта срабатывает генератор импульсов 1. Этого времени достаточно, чтобы сигнал отсутствия блокировки, если он выработался, одновременно с сигналом от генератора импульсов достиг схемы «И 2 и открыл ее, чтобы дать возможность коммутатору подготовиться к открыванию следующей схемы «И 5.

Коммутатор выполнен на основе кольпевого сдвигаюп1,его регистра, в которой занесена кодовая комбинация, содержащая М-2 ноля TI две единицы в смежных разрядах. Благодаря этому коммутатор в течение времени t-r-,-,. необходилтого для переворачивания его ( триггера, открьдвает г-ю схему «И п. а затем мгновенно перебрасывает сигнал на ((--1)-ю схему «И 5. Это происходит к началу след ютего (/-|-П-го такта, если в м также не выработан сигнал «Блокировка. В это же время и при этом же условии происходит перестройка на набор, притнедший в /-м такте, г-го УРПИ. на вход разрешения перестройки которого через открытую схему «И 5 поступает сигнал ОТСУТСТВИЯ блокировки. Таким образом, обитая длина рабочего такта в этом случае составляет

f,p4-/.-, 1о5;гК- 5).

Одновременно с переключением коммутатора и перестройкой УРПН реверсивный счетчик увеличивает свое показание на 1. Состояние триггера управлрния 14 не меняется, так как при отсутствии сигнала «Блокировка схема «И 18 остается закрытой. Итак, в случае отсутствия сигнала «Блокировка в t-w такте предлагаемое УСТРОЙСТВО к концу такта полностью готово к приему очередного набора.

Рассмотрим более сложный случай, когда гигнал «Блокировка в t-w такте вырабатьт чается. Тогдя на выхоте схемы «НЕ 6 сигнал не проявляется, схелты «И 2 и 5 не открываются, и переключение коммутатора и перестройка /-ГО УРПН не происходят. Но открывается схема «И 18, и сигнал с выхо.да УРПН, задержанный с помощью схемы задержки 17 на время То, необходимое для того.

чтобы сигнал с выхо.да схемы «ИЛИ 8 достиг схемы «И 18, поступает Tia oxiy- «Вычитание триггера управлсгия 14

T2-(logo/(4-2).f:..

Наличие этих триггеров управления обусловлено тем, что по условиям работы устройства входные наборы, вызывающие сигнал «Блокировка, не должны учитываться в показаниях

реверсивных счетчиков, и, следовательно, из показаний тех реверсивных счетчиков, на которые в /-м такте ноступил сигнал, необходимо вычесть 1. В дальнейнтем через срабатывает реверсивный счетчнк 12. а через 2.c

изменяется состояние триггера управления. Через ti 2/.-rr отключаются с ммирования и подключаются схемы вычитания в реверсивном счетчике. Задержка на г. получаемая в схемах задержки 19 ц 20. необходнма для того, чтобы все триггеры реверсивного счетчика успели перевернуться. Таким образом, к концу /-ГО такта на реверсивных счетчиках, соответствующих тем УРПН, которые сработали в прошлом такте, зафпксировлна

лишняя единица, а их тпт5ггеры управления находятся в состоянии «Вычитание. Когда в (-П-м такте спабатывает генорятп; тптпульсов 1, его сигнал через открыт-те схемы «И 15 и «ИЛИ 16 пост пает па входы ренерсивных счетчиков ч вычитает «лишнюю единицу. Oднoвl). иройдя через «ИЛИ 13. этот сцгнал тереводит триггер иравления в состоян ге «С.южение. и к моменту начала ()-го такта устройство снова оказывается в исходном согтоянит. При этом, если в (/--П-м такт- прихпдит нябпр, отличный от поступившего в такте, то его восирипимают TI обрабатывают свои УРПН и реверсивные счетчики. Если же ппттходит снова тот ж набор, то реверсивнье счетчики, работавтиие в предыдущем такте. ис г ырабатывать сигнал переполнения (их ттепь образовантя пепеносов отключена триггером управления), и схема «И 18 остается закрытой. В этом сллчае функцию выработки сигнала «Б.чокировка берет на себя 10. который выдает этот сигнал на вхол схемы «ИЛИ 9. Во всех случаях, когда сттгнал со схемы «И

5 разрещает перестройку УРПН, одновре Т1 нно ПРОИСХОДИТ сброс соответствующего реверсивного счетчика, а его триггер управления устанавливается в состояние «Сложение.

Таким oбpaзo т. преллагаемп,° лттронгтво осуществляет оперативный КОНТРОЛЬ соответствия характергтстик входного потока сигналов равномерному и с помощью стгнала «Блокировка указывает набо ьт сигналов, нарушающие равнот-герность распределенття входного потока сигналов. При этом некоторая выборка из .М результатов наблюдрния входных сигналов считается не соответствующей равнол ерному распределеттию, если в ней какойдибо набор встречается бп.ггее. чем К раз.

Предмет изобретения

1.Устройство для автоматического контроля статистической равномерности потока сигналов по скользящей выборке, содержащее генератор импульсов, коммутатор, схемы «И и реверсивные счетчики, отличающееся тем, что, с целью повышения быстродействия, в него введены блоки подсчета числа повторений наборов и блок запоминания запретных наборов, причем входы устройства соединены с информационными входами блоков подсчета числа Повторений наборов и блока запоминания запретных наборов, выход генератора импульсов соединен с входами синхронизации блоков подсчета числа повторений наборов н блока запоминания запретных наборов и через схему «И - с входом коммутатора, выходы которого непосредственно и через группу схем «НЕ соединены с первым и вторым входами группы схем «И, третьи входы группы схем «И соединены с вторым входом схемы «И и через схему «НЕ - с выходом устройства, а выходы группы схем «И - с входами разрешения блоков подсчета числа повторений наборов, выходы которых через многовходовую схему «ИЛИ соединены с входами управления этих блоков и с первым входом двухвходовой схемы «ИЛИ, второй вход которой соединен с выходом блока запоминания запретных наборов, а выход - с выходом устройства и с входом сигнализации о запретном наборе блока запоминания запретных наборов.

2.Устройство цо п. 1, отличающееся тем, что блок подсчета числа повторений наборов состоит из узла регистрации повторений наборов, реверсивного счетчика, триггера управления, схем задержки. схем «И,

«ИЛИ, причем информационные входы блока связаны с информационными входами узла регистрации повторений наборов, вход разрешения перестройки блока связан с входом разрешения перестройки узла регистрации повторений наборов, входом сброса реверсивного счетчика п через первую схему «ИЛИ с входом «Сложение триггера управления, а второй вход первой схемы «ИЛИ соединен с входом синхронизации блока через первую схему «И, второй вход которой связан с выходом «Вычитание триггера управления, вход управления блоко.м соединен с входом «Вычитание триггера управления через вто5 ) ю схему «И, второй вход которой через пе)вую схему задержки соединен с выходом узла регистрации повторений наборов, выхо;1Ы триггера управления через вторую и третью схемы задержки связаны с входами

управления реверсивного счетчика, выход переполнения которого связан с выходом блока, а счетный вход соединен с выходом узла регистрации повторений наборов через вторую схему «ИЛИ, второй вход которой через

5 первую схему «И соединен с входом синхронизации блока.

3. Устройство гю п. 1, от л и ч а ю П1, е е с я ic.i, что блок запоминания запретных наборов состоит из узла регистрации повторений

0 наборов, схемы задержки и схемы «И, причем информационные входы узла регистрации повторений наборов связаны с информа11иоииыми входами блока, вход синхронизаи,ии блока связан с входом разрешения перестройки узла регистрации повторений наборов, вход которого связан с. выходом блока через схему «И, второй вход которой через схему задержки связан с входом сигнализации о запретном наборе.

Фиг. 1

/J

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления последствий сбоев | 1981 |

|

SU1005062A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Устройство управления | 1983 |

|

SU1166108A1 |

| Многоканальный генератор последовательностей импульсов | 1983 |

|

SU1228232A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для обработки экспериментальных данных | 1982 |

|

SU1206811A1 |

п

8 -

2

иг. 2

2J

-О

Авторы

Даты

1975-06-30—Публикация

1973-05-21—Подача