Изобретение относится к вычислительной технике и может быть использовано при создании цифровых вычислительных машин (ЦВМ) повышенной надежности.

Известно устройство для исправле ния последствий сбоев, содержащее блок управления операциями, вход и первый выход которого соответственно соединены с выходом и входом блока повторения команд, а второй выход с входом блока контроля, и обеспечивающее контроль исправной работы ЦВМ и перевод ее в режим диагностирования в случае выхода из строя .

Недостатком этого устройства являются ограниченные возможности по диагностированию случайных сбоев и ycTpaHeHtno их последствий.

Известно также устройство выполнения повторных операций, содержащее блок памяти, М регистров передачи данных, причем выход блока памяти соединен с входом первого регистра , передачи данных и является первым выходом устройства, выход каждого регистра передачи данных связан с входом последующего регистра, а первым входом устройства служит вход блока памяти 23.

Недостатком этого устройства является необходимость начинать цикл повторения операции с чтения команды, выполнение которой прервано в результате появления ошибки, что приводит к излишним затратам времени.

Наиболее близким к предлагаемому является устройство, содержащее блок памяти, М регистров передачи данных, М триггеров признака, группу элементов И, узел блокировки, счетчик, блок, блок выдачи данных СЗ.

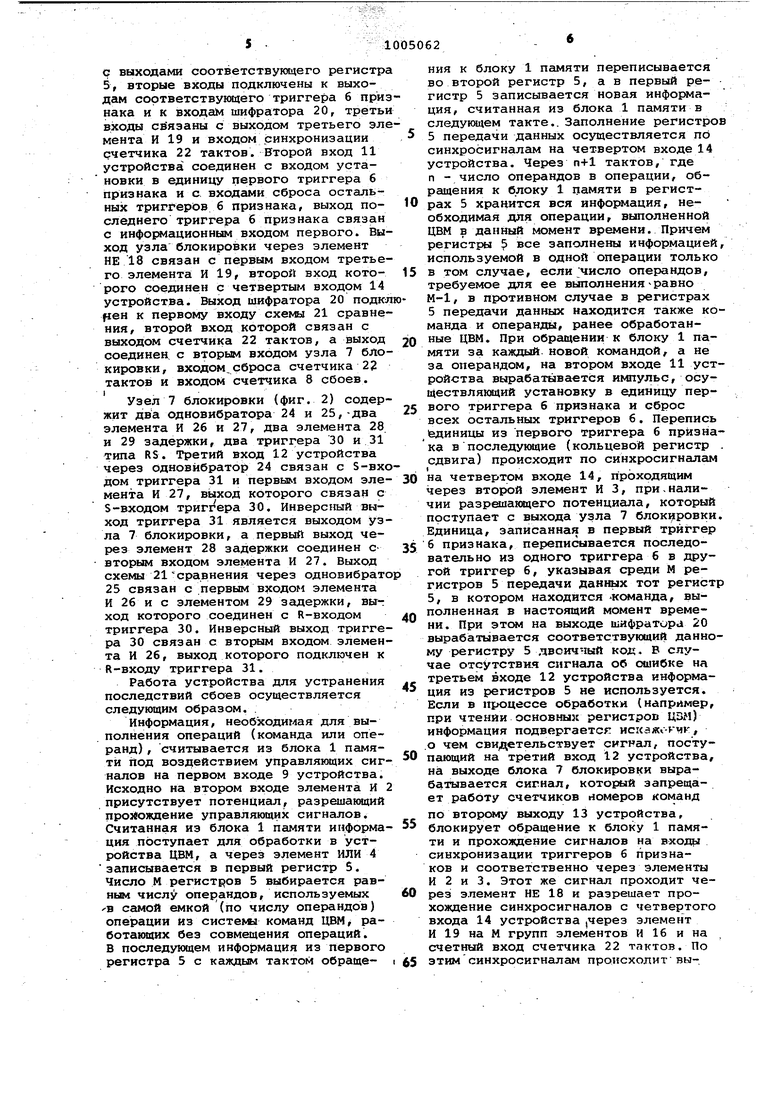

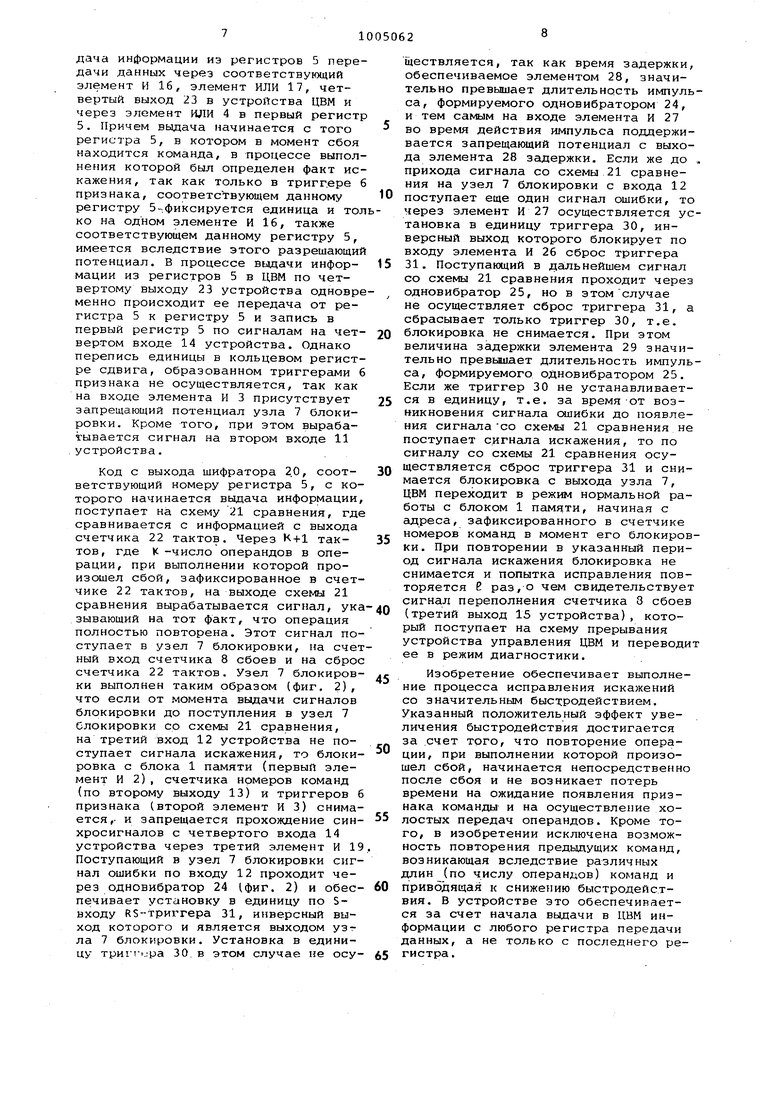

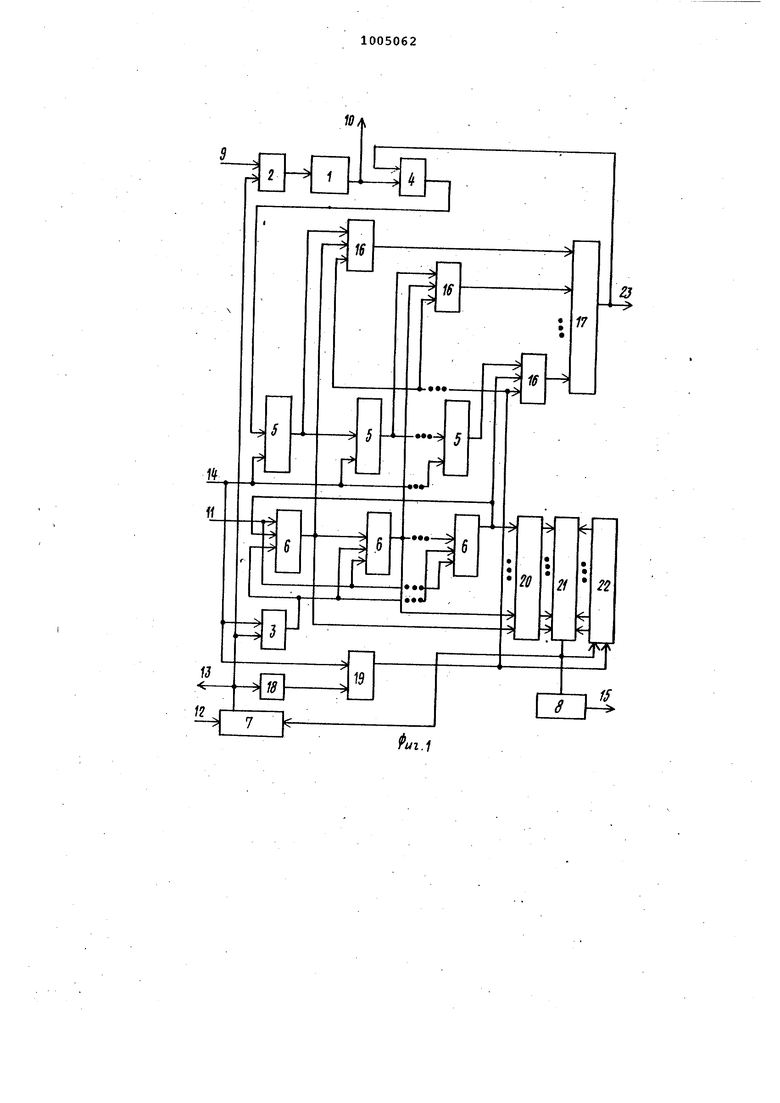

Недостатком устройства является Низкое быстродействие исправления искажений для ЦВМ, работающих безз совмещения операций. При выполнении команд ЦВМ подвергается обработке разное количество операндов, так как используются различные виды адресации (непосредственная, относительная,, косвенная) и операций (короткие, ; двойные, длинные). При этом число М регистров передачи данных выбирается равным максимальному количеству операндов, используемлх при выполнении ЦВМ. В режимах работы без смещения операций возможны ситуации, когда в регистрах передачи хранится не только информация, подвергающаяся обработке в данной момент времени (при выполнении данной команды), но и информация ,,обр&ботанная в предыдущих командах и эти команды. При возникновении сбоя в известном устройстве начинается либо повторение не команды, в процессе выполнения которой произошел сбой, а одной из предыдущих команд, либо возникает необходимость ожидать появление признака команды и осуществлять холостые передачи, воз((южно также в целом ряде случаев ошибочное решение задачи. Цель изобретения -.повышение быст родействия устройства. Поставленная цель достигается тем что в устройство для исправления пос ледствий сбоев, содержащее блок памяти, два злемента И, первый элемент ИЛИ, М регистров, где М - максимальное количество операндов самой длинной команды, М триггеров признака, узел блокировки и счетчик сбоев, при чем вход управления устройства соеди нен с первым входом первого элемента И, выход которого соединен с входом блока памяти, выход блока памяти соединен с первым входом первого элемента ИЛИ и является информационным выходом устройства, вход при знака команды устройства соединен с единичным входом первого триггера признака и с нулевым входом {м-1) триггеров признака, единичный выход каждого i-го триггера признака, где i- t-{M-l) соединен с единичным входом (i+l)-ro триггера признака, выход триггера признака соединен с вторым единичным входом первого триггера признака, вход признака сбоя устройства соединен с первым входом узла блокировки, выход которого соединен с вторым входом первого элемента И, первым входом второго элемента И и является выходбм блокировки устройства, тактовый вход устройства соединен с управляющими входами всех М регистров и.с вторым входом второго элемента И, выход которого соединен с тактовЕЛМи входами всех триггеров признака, выход первого элемента ИЛИ соединен с информа ционным входом первого регистра, информационный выход каждого i-ro ре гистра соединен с информационным входом (i+l)-ro регистра, выход счет чика сбоев является выходом прерывания работы устройства,введены второй элемент ИЛИ, элемент НЕ, третий элемент И, шифратор, схема сравнения счетчик тактов и группа элементов И, причем информационный выход i-го регистра и единичный выход i-ro тригге ра признака соединены соответственно с первым и вторым входами соответствующего элемента И группы, выход которого соединен с соответствующим входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с вторым входом первого элемента ИЛИ и является вторым информационным выходом устройства, единичный выход каждого i-ro триггера признака соединен с соответствующим входом шифратора, выходы которого соединены с первой группой входов блока сравнения, выход узла блокировки через элемент НЕ соединен с первым входом третьего элемента И, выход которого соединен с нулевыми входами элементов И группы и со счетным входом счетчика тактов, информационные выходы счетчика тактов соединены с второй группой схемы сравнения, выход которой соединен с управляющим входом счетчика тактов, с вторым входом узла блокировки и со счетным входом счетчика сбоев, тактовый вход устройства соединен с вторым входом третьего элемента И. На фиг. 1 представлена схема устройства для исправления последствий сбоев; на фиг. 2 - блок-схема узла блокировки устройства. Устройство для исправления последствий сбоев содержит блок 1 памяти, два элемента И 2 и 3, элемент ИЛИ 4, М регистров 5 и М триггеров б признака, узел 7 блокировки и счетчик 8 сбоев. Первым входом 9 устройства является вход элемента И 2, Выход блока 1 памяти через элемент ИЛИ 4 соединен с информационныгл входом первого регистра 5 и является первым выходом 10 устройства. Выход, каждого регистра 5 соединен с входом последующего регистра 5. Второй вход 11 устройства соединен с триггерами 6 признака, выход каждого из которых связан с информационным входом последующего триггера 6 признака. Первый вход узла 7 блокировки является третьим входом 12 устройства, выход узла 7 блокировки связан с вторым выходом 13 устройства, с вторым входом элемента И 2 и с первым входом элемента ИЗ. Второй, вход элемента И 3 соединен с тактовыми входами регистров 5 и с четвертым входом 14 устройства, а выход подключен к тактовым входам триггеров 6 признака. Выход счетчика 8 сбоев является третьим выходбм 15 устройства. Устройство, кроме того, содержит М групп элементрв И 16, второй элемент ИЛИ 17, элемент НЕ 18, третий элемент И 19, шифратор 20, схему 21 сравнения, счетчик 22 тактов. Выходы групп элементов И 16 связаны с входами элемента ИЛИ 17, выход которого подключен через первый элемент ИЛИ 4 к информационному входу первого регистра 5 и является четвертым выходом 23 устройства. Первые входы каждой из групп элементов И 16 соединены С выходами соответствукяцего регистр 5, вторые входы подключены к выходам соответствующего триггера 6 при нака и к входам шифратора 20, треть входы сбяэаны с выходом третьего эл мента И 19 и входом синхронизации счетчика 22 тактов. Второй вход 11 устройства соединен с входом установки в единицу первого триггера 6 признака и е входами сброса остальных триггеров 6 признака, выход последнего триггера б признака связан с информационным входом первого. Вы ход узла блокировки через элемент НЕ 18 связан с первым входом третье го элемента И 19, второй вход которого соединен с четвертым входом 14 устройства. Выход шифратора 20 подк рен к первому входу схемы 21 сравне ния, второй вход которой связан с выходом счетчика 22 тактов, а выход соединен, с вторым входом узла 7 бло кировки, входом,сброса счетчика 22 тактов и входом счетчика 8 сбоев. Узел 7 блокировки (фиг. 2) содер жит два одновибратора 24 и 25,-два элемента И 26 и 27, два элемента 28 и 29 задержки, два триггера 30 и 31 типа RS. Третий вход 12 устройства через Одновйбратор 24 связан с S-вхо дом триггера 31 и первым входом элемента И 27, выход которого связан с S-входом триггера 30. Инверсный выход триггера 31 является выходом узла 7 блокировки, а первый выход через элемент 28 задержки соединен свторым входом элемента И 27. Выход схемы 21 сравнения через одновибрато 25 связан с первым входом элемента И 26 и с элементом 29 задержки, выход которого соединен с R-входом триггера 30. Инверсный выход триггера 30 связан с BTOfftiM входом элемента И 26, выход которого подключен к R-входу триггера 31. Работа устройства для устранения последствий сбоев осуществляется следующим образом. . Информация, необходимая для выполнения операций (команда или операнд) , считывается из блока 1 памятй под воздействием управляющих сигНсшов на первом входе 9 устройства. Исходно на втором входе элемента И 2 присутствует потенциал, разрешающий ПРО} ождение управляющих сигналов. Считанная из блока 1 памяти информация поступает для обработки в устройства ЦВМ, а через элемент ИЛИ 4 записывается в первый регистр 5. Число М регистров 5 выбирается равным числу операндов, используемых В самой емкой (по числу операндов) операции из систекы команд ЦВМ, работающих без совмещения операций. В последующем информация из первого регистра 5 с каждым тактом обращения к блоку 1 памяти переписывается во второй регистр 5, а в первый ре- гистр 5 записывается новая информация, считанная из блока 1 памяти в следуиицем такте.. Заполнение регистров 5 передачи данных осуществляется по синхросигналам на четвертом входе 14 устройства. Через п+1 тактов, где п - число операндов в операции, обращения к блоку 1 памяти в регистрах 5 хранится вся информация, необходимая для операции, выполненной ЦВМ в данный момент времени. Причем регистры 5 все заполнены информацией, используемой в одной операции только в том случае, если число операндов, требуемое для ее выполнения равно М-1, в противном случае в регистрах 5передачи данных находится также команда и операнды, ранее обработанные ЦВМ. При обращении к блоку 1 памяти за каждый новой командой, а не за операндом, на втором входе 11 устройства вырабатывается импульс, осуществлякидий установку в единицу первого триггера 6 признака и сброс всех остальных триггеров 6. Перепись единицы из первого триггера 6 признака впоследующие (кольцевой регистр . сдвига) происходит по синхросигналам на четвертом входе 14, проходящим через второй элемент И 3, при-наличии разрешакадего потенциала, который поступает с выхода узла 7 блокировки. Единица, записанная в первый триггер 6признака, переписывается последовательно из одного триггера 6 в другой триггер 6, указывая среди М регистров 5 передачи данных тот регистр 5, в котором находится Команда, выполненная в настоящий момент времени. При этсяи на выходе шифратора 20 вырабатывается соответствующий данному регистру 5 двоиччый код. В случае отсутствия сигнала об ошибке на третьем входе 12 устройства информация из регистров 5 не используется. Если в процессе обработки (например, при чтении основных регистров ЦЗМ) информация подвергается ис1 аж1-кчк, о чем свидетельствует сигнал, поступающий на третий вход 12 устройства, на выходе блока 7 блокировки вырабатывается сигнал, который запрещает работу счетчиков номеров команд по второму выходу 13 устройства, блокирует обращение к блоку 1 памяти и прохождение сигналов на входы синхронизации триггеров 6 признаков и соответственно через элементы И 2 и 3. Этот же сигнал проходит через элемент НЕ 18 и разрешает прохождение синхросигналов с четвертого входа 14 устройства ,через элемент И 19 на М групп элементов И 16 и на счетный вход счетчика 22 тактов. По этимсинхросигналам происходит выдача информации из регистров 5 передачи данных через соответствующий элемент И 16, элемент ИЛИ 17, четвертый выход 23 в устройства ЦВМ и через элемент Ш1И 4 в первый регистр 5. Причем выдача начинается с того регистра 5, в котором в момент сбоя находится команда, в процессе выполнения которой был определен факт искажения, так как только в триггере 6 признака, соответствующем данному регистру 5-;фиксируется единица и толко на одном элементе И 16, также соответствующем данному регистру 5, имеется вследствие этого разрешающий потенциал. В процессе выдачи информации из регистров 5 в ЦВМ по четвертому выходу 23 устройства одновременно происходит ее передача от регистра 5 к регистру 5 и запись в первый регистр 5 по сигналам на четвертом входе 14 устройства. Однако перепись единицы в кольцевом регистре сдвига, образованном триггерами 6 признака не осуществляется, так как на входе элемента И 3 присутствует запрещающий потенциал узла 7 блокировки. Кроме того, при этом вырабатывается сигнал на втором входе 11 устройства.

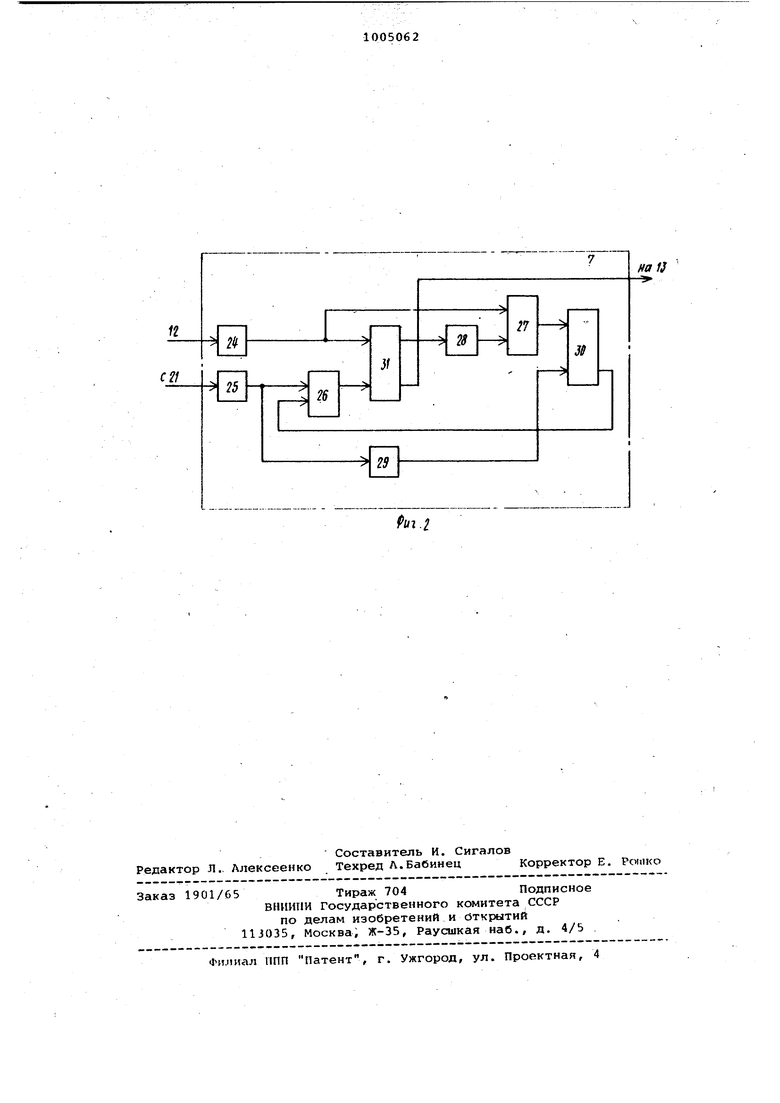

Код с выхода шифратора 2.0, соответствующий номеру регистра 5, с которого начинается вьвдача информации, поступает на схему 21 сравнения, где сравнивается с информацией с выхода счетчика 22 тактов. Через К+1 тактов, где К-число операндов в операции, при выполнении которой произошел сбой, зафиксированное в счетчике 22 тактов, на выходе схемы 21 сравнения вырабатывается сигнал, ука зывающий на тот факт, что операция полностью повторена. Этот сигнал поступает в узел 7 блокировки, на счетный вход счетчика 8 сбоев и на сброс счетчика 22 тактов. Узел 7 блокировки выполнен таким образом (фиг. 2), что если от момента выдачи сигналов блокировки до поступления в узел 7 блокировки со схемы 21 сравнения, на третий вход 12 устройства не поступает сигнала искажения, то блокировка с блока 1 памяти (первый элемент И 2), счетчика номеров команд (по второму выходу 13) и триггеров 6 признака (второй элемент И 3) снимается,- и запрещается прохождение синхросигналов с четвертого входа 14 устройства через третий элемент И 19 Поступающий в узел 7 блокировки сигнал ошибки по входу 12 проходит через одновибратор 24 (фиг. 2) и обеспечивает установку в единицу по Sвходу К5--триг-гера 31, инверсный выход которого и является выходом узг ла 7 блокировки. Установка в единицу тригт-ира 30 в этом случае не осуществляется, так как время задержки, обеспечиваемое элементом 28, значительно превышает длительность импульса, формируемого одновибратором 24, и тем самым на входе элемента И 27 во время действия импульса поддерживается запрещающий потенциал с выхода элемента 28 задержки. Если же до прихода сигнала со схемы 21 сравнения на узел 7 блокировки с входа 12 поступает еще один сигнал ошибки, то через элемент И 27 осуществляется установка в единицу триггера 30, инверсный выход которого блокирует по входу элемента И 26 сброс триггера 31. Поступающий в дальнейшем сигнал со схемы 21 сравнения проходит через одновибратор 25, но в этомслучае не осуществляет сброс триггера 31, а сбрасывает только триггер 30, т.е. блокировка не снимается. При этом величина задержки элемента 29 значительно превьшает длительность импульса, формируемого одновибратором 25. Если же триггер 30 не устанавливается в единицу, т.е. за время от возникновения сигнала сшибки до появления сигнала СО схемы 21 сравнения не поступает сигнаша искажения, то по сигналу со схемы 21 сравнения осуществляется сброс триггера 31 и снимается блокировка с выхода узла 7, ЦВМ переходит в режим нормальной работы с блоком 1 памяти, начиная с адреса, зафиксированного в счетчике номеров команд в момент его блокировки. При повторении в указанный период сигнала искажения блокировка не снимается и попытка исправления повторяется Е раз,о чем свидетельствует сигнал переполнения счетчика 8 сбоев (третий выход 15 устройства), который поступает на схему прерывания устройства управления ЦВМ и переводи ее в режим диагностики.

Изобретение обеспечивает выполнение процесса исправления искажений со значительным быс1:родействием. Указанный положительный эффект увеличения быстродействия достигается за .счет того, что повторение операции, при выполнении которой произошел сбой, начинается непосредственно после сбоя и не возникает потерь времени на ожидание появления признака команды и на осуществление холостых передач операндов. Кроме того, в изобретении исключена возможность повторения предьщущих команд, возникающая вследствие различных длин (по числу операндов) команд и приводящая к снижению быстродействия. В устройстве это обеспечивается за счет начала выдачи в ЦВМ информации с любого регистра передачи данных, а не только с последнего регистра .

Формула изобретения

Устройство для исправления последствий сбоев, содержащее блок памяти, два элемента И, первый элемент ИЛИ, АА регистров, где t - максимальное количество операндов самой длинной команды, fA триггеров признака, узел блокировки и счетчик сбоев, причем вход управления, устройства соединен с первым входом первого элемента И, выход которого соединен с входом блока памяти, выход блока памяти соединен с первым входом первого элемента ИЛИ и является информационным выходом устройства, вход признака команды устройства соединен с единичным входом первого триггера и с нулевым входом (-l) триггеров признака, единичный выход каждого i-ro триггерапризнака, где i - 1-(ЛЛ-1 соединен с единичным входом Ci+l)-ro триггера признака, выход триггера признака соединен с вторым единичным входом первого триггера признака, вход признака сбоя устройства соединен с первым входом узла блокировки, выход которого соединен с вторым входом первого элемента И, первым входом второго элемента И и является выходом блокировки устройства, тактовый вход устройства соединен с управляющими входами всех М регистров и с вторы входом второго элемента И, выход которого соединен с тактовыми входами всех триггеров признака, выход первого элемента, ИЛИ соединен с информационным входом первого регистра, информационный каждого i-ro регистра соединен с информационным входом U+l)-ro регистра, выход счетчика сбоев является выходом прерывания работы устройства, о т л и ч аК) щ е е е с я тем, что, с целью повышения быстродействия, в устройство введены второй элемент ИЛИ, элемент НЕ, третий элемент Н, шифратор, схема сравнения, счетчик тактов и группа элементов И, причем информационный выход t-го регистра и единичный выход -i-ro триггера признака соединены соответственно с первым и вторым входами соответствующего

0 элемента И группы, выход которого соединен с соответствующим входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с вТорыги вхо.дом первого элемента ИЛИ и является

5 вторым информационным выходом устройства, единичный выход каждого i го триггера признака соединен с соответствующим входом шифратора, выходы которого соединены с первой

0 группой входов блока сравнения, выход узла блокировки через элемент НЕ соединен с перВЕлм входом третьего элемента И, выход которого соединен с нулевыми входами элементов Н груп5пы и со счетным входом счетчика тактов, инфор)Мационные выходы счетчика тактов соединены с второй группой входов схемы сравнения, выход которой соединен с управляющим входом

0 счетчика тактов, с вторым входом узла блокировки и со счетным входом счетчика сбоев, тактовый вход устройства соединен с вторым входом треть- . его элемента И,

Источники информации,

5 принятые во внимание при экспертизе

1.Авторское свидетельство СССР 279172, кл, G 06 F 11/00, 1972.

2.Авторское свидетельство СССР № 1В9621, кл. С- 06 F 11/00, 1968.

0

3.Авторское свидетельство СССР 552608, кл. G 06 F 11/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Устройство для устранения последствий случайных сбоев | 1980 |

|

SU886002A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Устройство для устранения последствий сбоев | 1975 |

|

SU552608A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для восстановления информации при сбоях в блоках ЦВМ | 1983 |

|

SU1124314A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Вычислительное устройство для ранговой фильтрации | 1989 |

|

SU1656554A1 |

Авторы

Даты

1983-03-15—Публикация

1981-08-31—Подача