Изобретение относится к импульсной технике и может быть использован для контроля систем цифровой связи, цифровых интегральных схем, блоков памяти, систем диагностики.

Цель изобретения - расширение функциональных возможностей за счет изменения положения импульсов в такт последовательности.

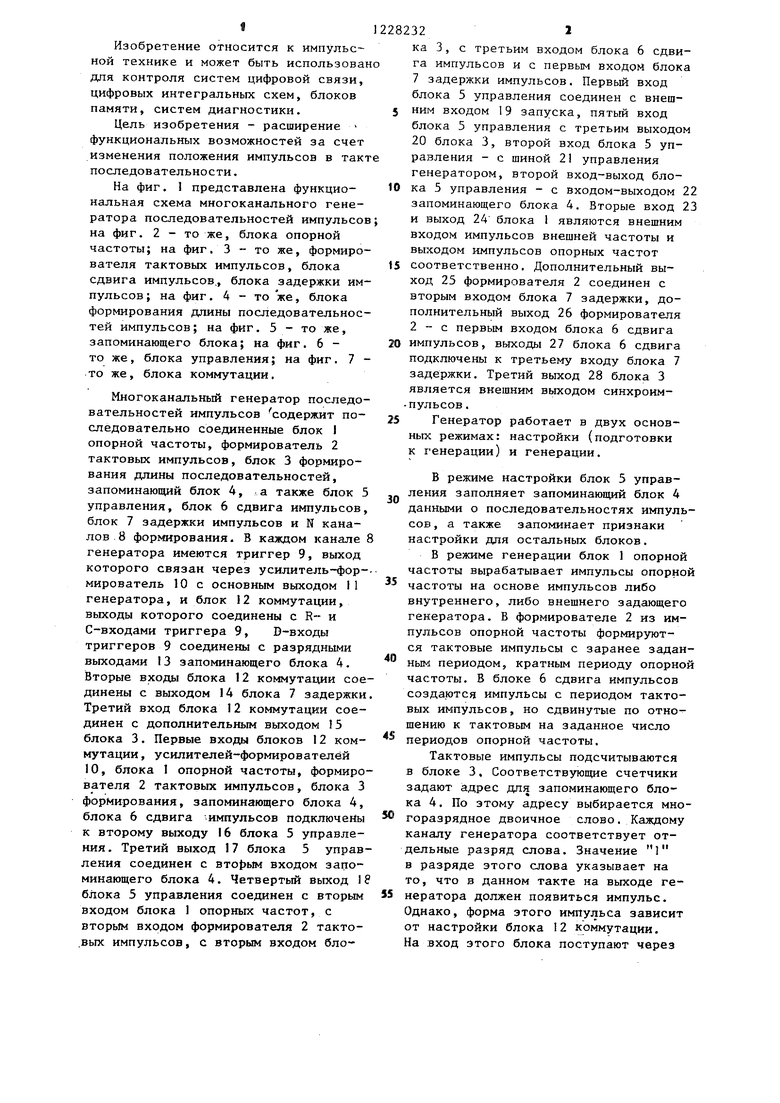

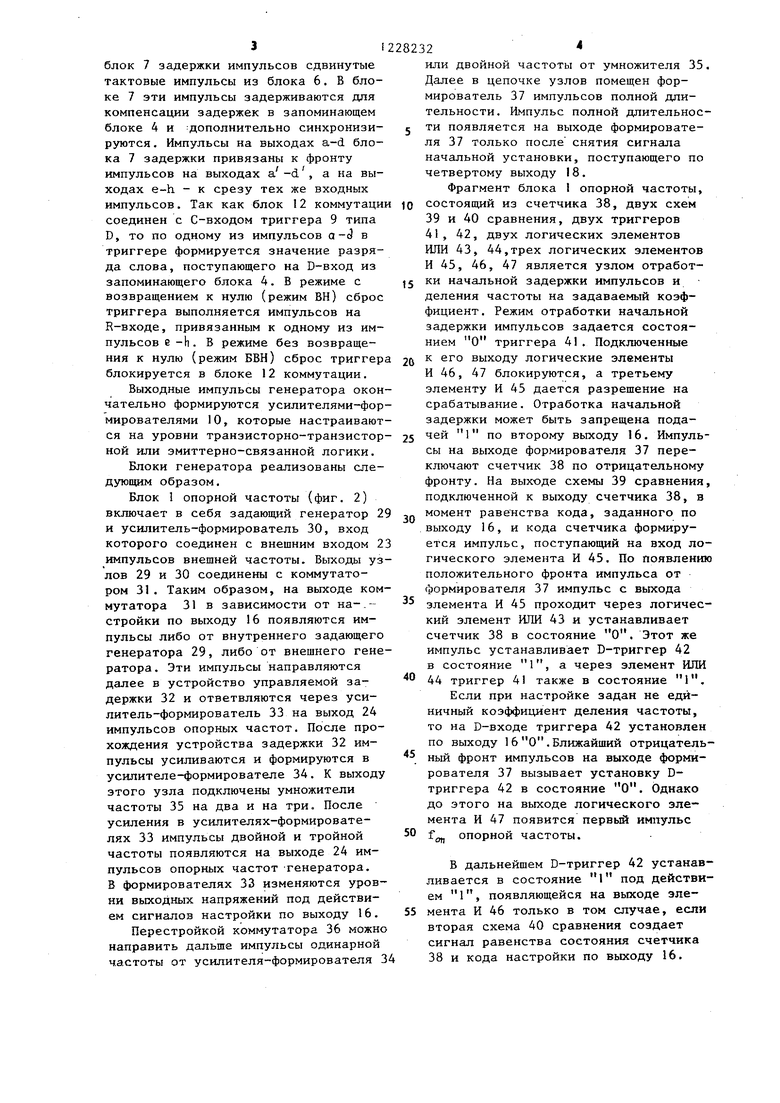

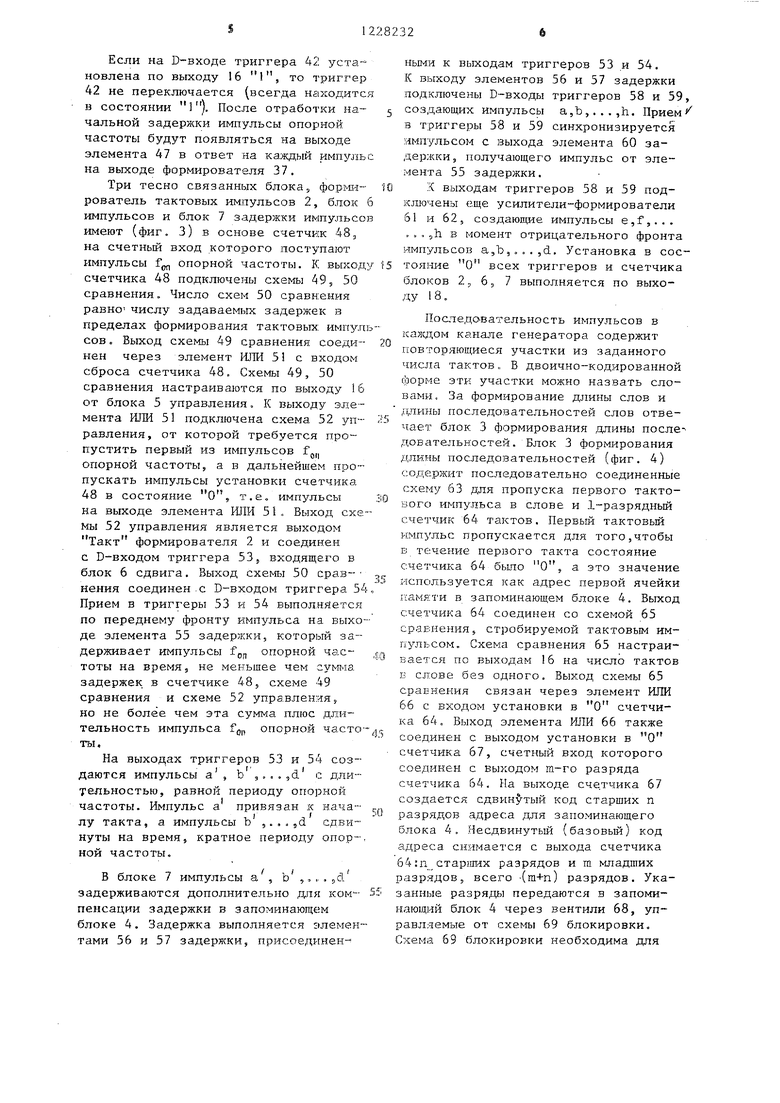

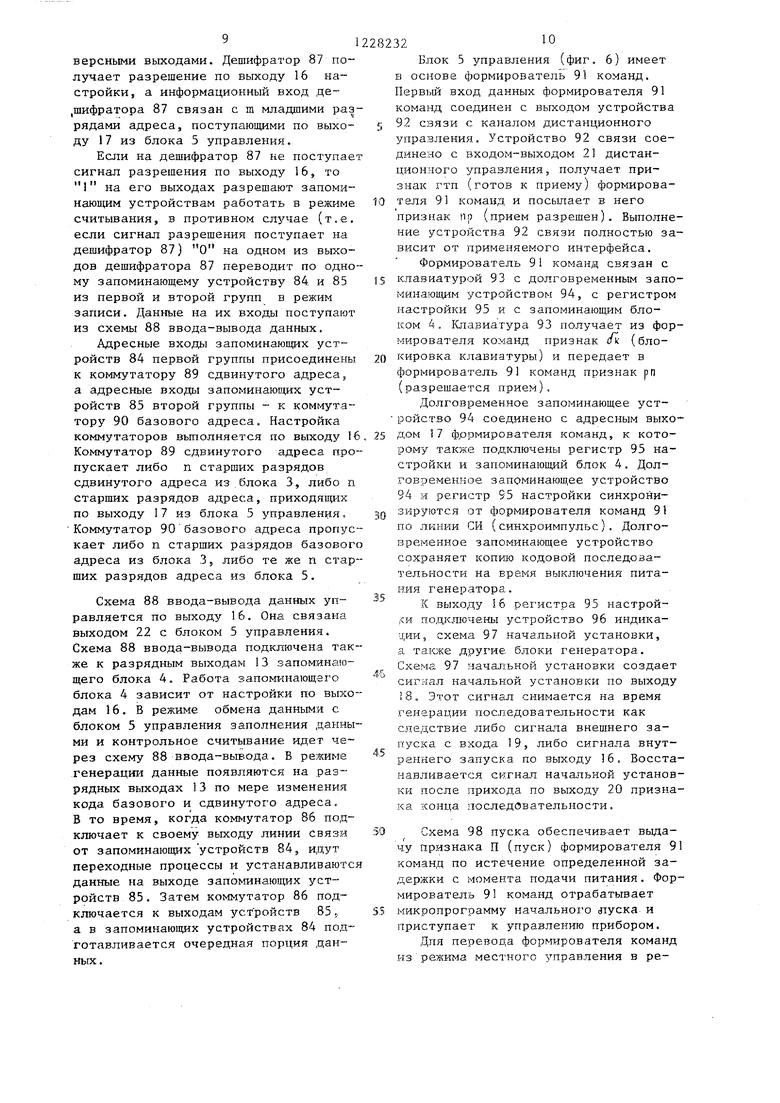

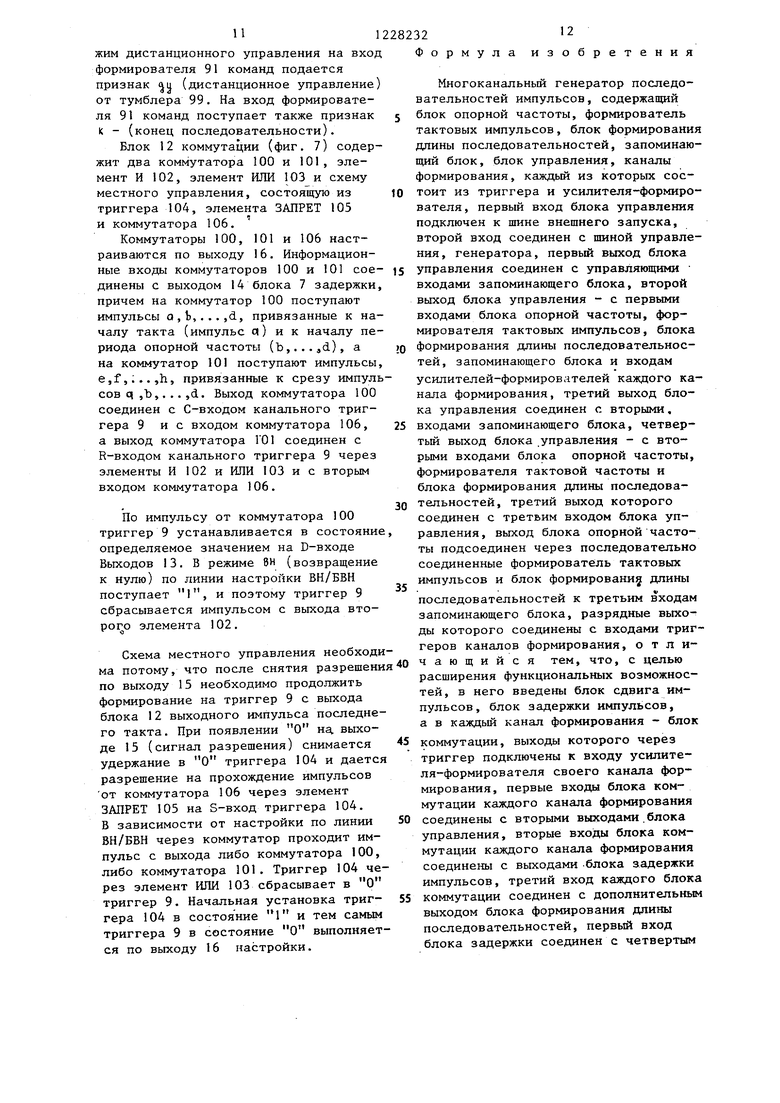

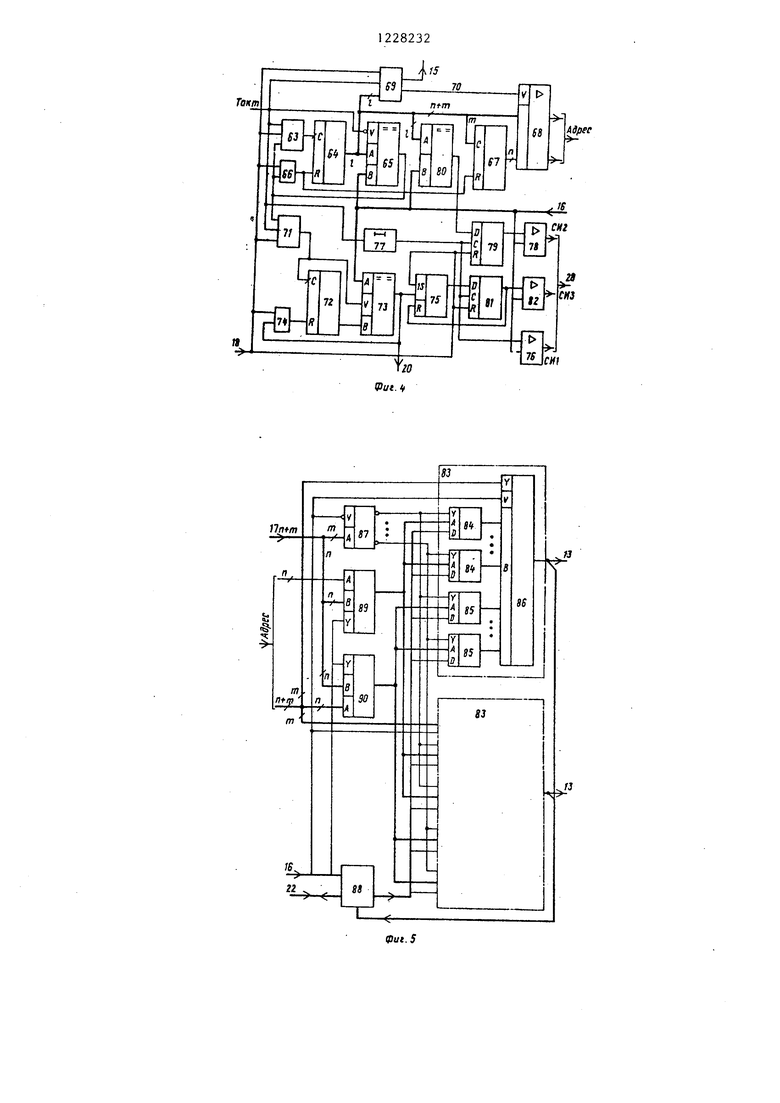

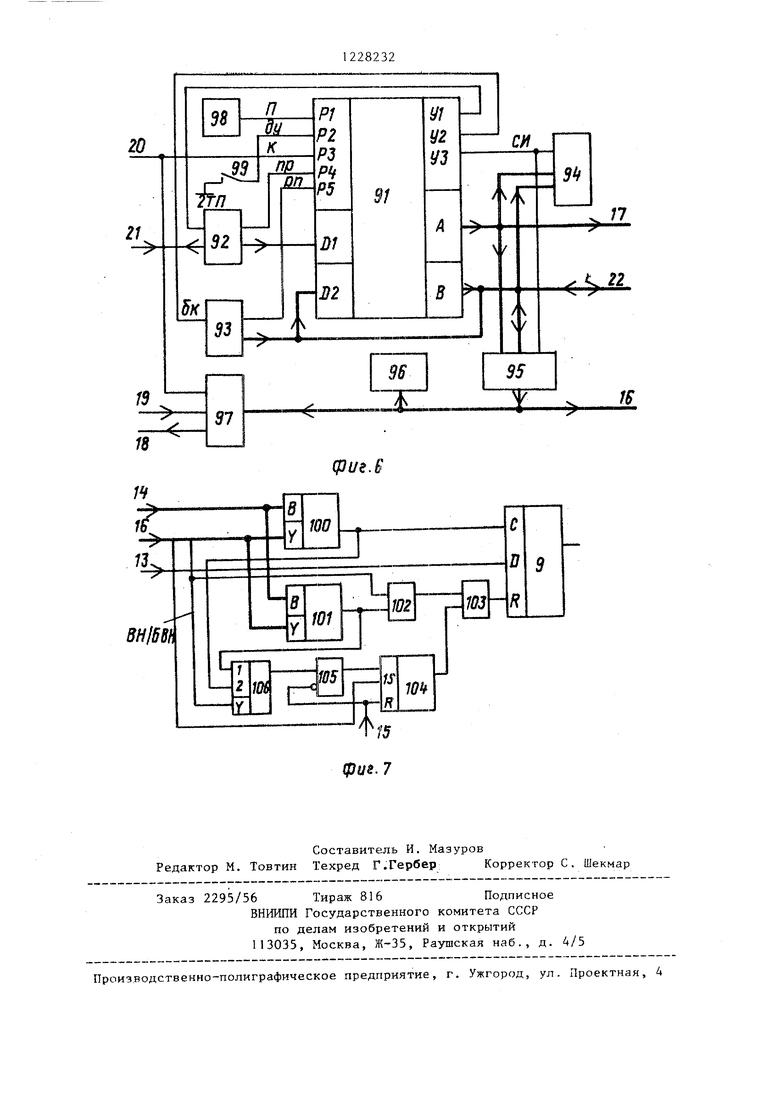

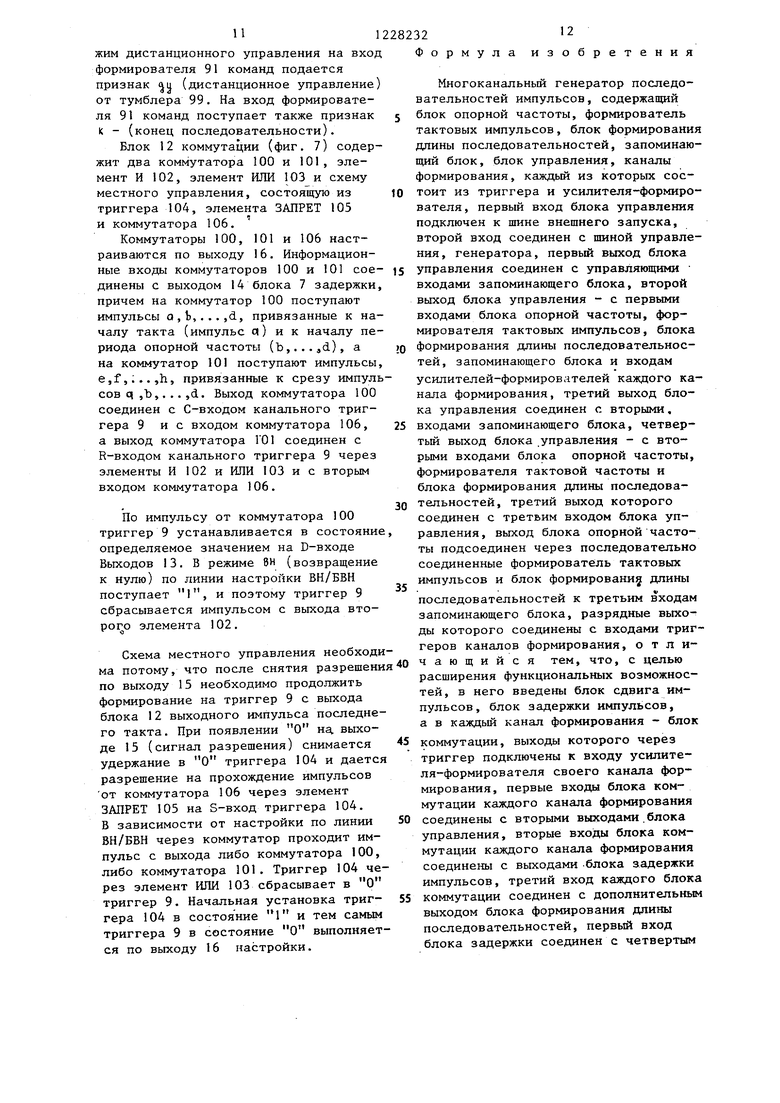

На фиг. 1 представлена функциональная схема многоканального генератора последовательностей импульсов на фиг. 2 - то же, блока опорной частоты; на фиг. 3 - то же, формирователя тактовых импульсов, блока сдвига импульсов,, блока задержки импульсов ; на фиг, 4 - то же, блока формирования длины последовательностей импульсов; на фиг. 5 - то же, запоминающего блока; на фиг. 6 - то же, блока управления; на фиг. 7 - то же, блока коммутации.

Многоканальный генератор последовательностей импульсов содержит последовательно соединенные блок I опорной частоты, формирователь 2 тактовых импульсов, блок 3 формирования длины последовательностей, запоминающий блок 4, а также блок 5 управления, блок 6 сдвига импульсов, блок 7 задержки импульсов и N каналов 8 формирования. В каждом канале генератора имеются триггер 9, выход которого связан через усилитель-формирователь 10 с основным выходом 11 генератора, и блок 12 коммутации, выходы которого соединены с R и С-входами триггера 9, D-входы триггеров 9 соединены с разрядными выходами I3 запоминающего блока 4, Вторые входы блока 12 коммутации соединены с выходом 14 блока 7 задержки Третий вход блока 12 коммутации соединен с дополнительным выходом 15 блока 3. Первые входы блоков 12 коммутации, усилителей-формирователей 10, блока 1 опорной частоты, формирователя 2 тактовых импульсов, блока 3 формирования, запоминающего блока 4, блока 6 сдвига импульсов подключены к второму выходу I6 блока 5 управления . Третий выход 17 блока 5 управления соединен с входом запоминающего блока 4. Четвертый выход I блока 5 управления соединен с вторым входом блока 1 опорных частот, с вторым входом формирователя 2 такто- .вых импульсов, с вторым входом блока 3 , с третьим входом блока 6 сдвига импульсов и с первым входом блока 7 задержки импульсов. Первый вход блока 5 управления соединен с внешним входом 19 запуска, пятый вход блока 5 управления с третьим выходом 20 блока 3, второй вход блока 5 управления - с шиной 21 управления генератором, второй вход-выход блока 5 управления - с входом-выходом 22 запоминающего блока 4. Вторые вход 23 и выход 24 блока 1 являются внешним входом импульсов внешней частоты и выходом импульсов опорных частот

соответственно. Дополнительный выход 25 формирователя 2 соединен с вторым входом блока 7 задержки, дополнительный выход 26 формирователя 2-е первым входом блока 6 сдвига

импульсов, выходы 27 блока 6 сдвига подключены к третьему входу блока 7 задержки. Третий выход 28 блока 3 является внешним выходом синхроим- пульсов.

Генератор работает в двух основных режимах: настройки (подготовки к генерации) и генерации.

В режиме настройки блок 5 управления заполняет запоминающий блок 4 данными о последовательностях импульсов , а также запоминает признаки настройки для остальных блоков.

В режиме генерации блок 1 опорной частоты вырабатывает импульсы опорной

частоты на основе импульсов либо

внутреннего, либо внешнего задающего генератора. В формирователе 2 из импульсов опорной частоты формируются тактовые импульсы с заранее заданньт периодом, кратным периоду опорной частоты. В блоке 6 сдвига импульсов создаются импульсы с периодом тактовых импульсов, но сдвинутые по отно шению к тактовым на заданное число

периодов опорной частоты.

Тактовые импульсы подсчитываются в блоке 3, Соответствующие счетчики задают адрес дпя запоминающего блока 4 . По этому адресу выбирается многоразрядное двоичное слово. Каждому каналу генератора соответствует отдельные разряд слова. Значение 1 в разряде этого слова указывает на то, что в данном такте на выходе генератора должен появиться импульс. Однако, форма этого импульса зависит от настройки блока I2 коммутации. На вход этого блока поступают через

блок 7 задержки импульсов сдвинутые тактовые импульсы из блока 6, В блоке 7 эти импульсы задерживаются для компенсации задержек в запоминающем блоке 4 и дополнительно синхронизи- руются. Импульсы на выходах a-d блока 7 задержки привязаны к фронту импульсов на выходах a -d , а на выходах e-h - к срезу тех же входных импульсов. Так как блок 12 коммутации соединен с С-входом триггера 9 типа D, то по одному из импульсов а-А в триггере формируется значение разряда слова, поступающего на D-вход из запоминающего блока 4. В режиме с возвращением к нулю (режим ВН) сброс триггера выполняется импульсов на R-входе, привязанным к одному из импульсов e-h. В режиме без возвращения к нулю (режим БВН) сброс триггера блокируется в блоке 12 коммутации.

Выходные импульсы генератора окончательно формируются усилителями-формирователями 10, которые настраиваются на уровни транзисторно-транзистор- ной или эмиттерно-связанной логики.

Блоки генератора реализованы следующим образом.

Блок 1 опорной частоты (фиг. 2) включает в себя задающий генератор 29 и усилитель-формирователь 30, вход которого соединен с внещним входом 23 импульсов внешней частоты. Выходы узлов 29 и 30 соединены с коммутатором 31. Таким образом, на выходе коммутатора 31 в зависимости от на-.- стройки по выходу 16 появляются импульсы либо от внутреннего задающего генератора 29, либо от внешнего генератора. Эти импульсы направляются далее в устройство управляемой задержки 32 и ответвляются через усилитель-формирователь 33 на выход 24 импульсов опорных частот. После прохождения устройства задержки 32 импульсы усиливаются и формируются в усипителе-формирователе 34. К выходу этого узла подключены умножители частоты 35 на два и на три. После усиления в усилителях-формирователях 33 импульсы двойной и тройной частоты появляются на выходе 24 импульсов опорных частот генератора. В формирователях 33 изменяются уровни выходных напряжений под действием сигналов настройки по выходу 16.

Перестройкой коммутатора 36 можно направить дальше импульсы одинарной частоты от усилителя-формирователя 3

0

5

Q 0 5

0

5

или двойной частоты от умножителя 35. Далее в цепочке узлов помещен формирователь 37 импульсов полной длительности. Импульс полной длительности появляется на выходе формирователя 37 только после снятия сигнала начальной установки, поступающего по четвертому выходу 18.

Фрагмент блока I опорной частоты, состоящий из счетчика 38, двух схем 39 и 40 сравнения, двух триггеров 41, 42, двух логических элементов ИЛИ 43, 44,трех логических элементов И 45, 46, 47 является узлом отработки начальной задержки импульсов и деления частоты на задаваемый коэффициент. Режим отработки начальной задержки импульсов задается состоянием О триггера 41. Подключенные к его выходу логические элементы И 46, 47 блокируются, а третьему элементу И 45 дается разрешение на срабатывание. Отработка начальной задержки может быть запрещена подачей 1 по второму выходу 16. Импульсы на выходе формирователя 37 переключают счетчик 38 по отрицательному фронту. На выходе схемы 39 сравнения, подключенной к выходу счетчика 38, в момент раве нства кода, заданного по выходу 16, и кода счетчика формируется импульс, поступающий на вход логического элемента И 45. По появлению положительного фронта импульса от формирователя 37 импульс с выхода элемента И 45 проходит через логический элемент ИЛИ 43 и устанавливает счетчик 38 в состояние О. Этот же импульс устанавливает D-триггер 42 в состояние 1, а через элемент ИЛИ 44 триггер 4 также в состояние 1.

Если при настройке задан не единичный коэффициент деления частоты, то на D-входе триггера 42 установлен по выходу .Ближайший отрицательный фронт импульсов на выходе формирователя 37 вызывает установку D- триггера 42 в состояние О. Однако до этого на выходе логического элемента И 47 появится первьй импульс ff опорной частоты.

В дальнейшем D-триггер 42 устанавливается в состояние 1 под действием 1, появляющейся на выходе элемента И 46 только в том случае, если вторая схема 40 сравнения создает сигнал равенства состояния счетчика 38 и кода настройки по выходу 16.

Если на D-входе триггера 42 уста- новлена по выходу 6 1, то триггер 42 не переключается (всегда находится в состоянии I). После отработки на- чальной задержки импульсы опорной частоты будут появляться на выходе элемента 47 в ответ на каждый импз/ льс на выходе формирователя 37,

Три тесно связанных блока, форми- рователь тактовых импульсов 2, блок 6 импульсов и блок 7 задержки импульсов имеют (фиг. 3) в основе счетчик 48з на счетный вход которого поступают импульсы fpp опорной частоты. К выхо-ду счетчика 48 подключены схемы 49, 50 сравнения. Число схем 50 сравнения равно числу задаваемых задержек в пределах формирования тактовых; импульсов . Выход схемы 49 сравнения соеди- нен через элемент ИЛИ 5i с входом сброса счетчика 48. Схемы 49, 50 сравнения настраиваются по выходу 16 от блока 5 управления. К выходу элемента ИЛИ 51 подключена схема 52 уп- равления, от которой требуется пропустить первый из импульсов fg,, опорной частоты, а в дальнейшем пропускать импульсы установки счетчика 48 в состояние 0 % т.е. импульсы на выходе элемента ШШ 51 , Выход схеМы 52 управления является выходом Такт формирователя 2 и соединен с D-входом триггера 53, входящего в блок 6 сдвига. Выход схемы 50 орав- нения соединен-С D-входом триггера 54 Прием в триггеры 53 и 54 выполнйется по переднему фронту импульса на выходе элемента 55 задержки, который задерживает импульсы fpj, опорной час- тоты на время, не меньшее чем сумма задержек, в счетчике 48, схеме 49 сравнения и схеме 52 управления, но не более чем эта сумма плюс длительность импульса Гд|, опо рной частоты.

На выходах триггеров 53 и 54 создаются импульсы а , b ,,..,d с длительностью, равной периоду опорной частоты. Импульс а привязан к нача- лу такта, а импульсы Ъ .,, d сдвинуты на время, кратное периоду опорной частоты,

В блоке 7 импульсы а , b ,, „ . pCl задерживаются дополнительно для ком- пенсации задержки в запоминающем блоке 4. Задержка выполняется ;шемен тами 56 и 57 задержки, присоединенными к выходам триггеров 53 и 54. К выходу элементов 56 и 57 задержки подключены D-входы триггеров 58 и 59 создающих импульсы a,b,...,h. Прием в триггеры 58 и 59 синхронизируется импульсом с выхода элемента 60 задержки, получающего импульс от элемента 55 задержки.

X выходам триггеров 58 и 59 подключены е.ще усилители-формирователи 61 и 62, создающие импульсы e,f,... .,,jh в момент отрицательного фронта импульсов а,,Ъ,, . . ,d. Установка в состояние О всех триггеров и счетчика блоков 2., 6 5 7 выполняется по выходу 18.

Последовательность импульсов в кажд,ом канале генератора содержит повторяющиеся участки из заданного числа тактов„ В двоично-кодированной форме эти участки можно назвать словами. За формирование длины слов и лпины последовательностей слов отвечает блок 3 формирования длины после довательностей. Блок 3 формирования длины последовательностей (фиг. 4) содержит последовательно соединенньге схему 63 для пропуска первого тактового импульса в слове и 1-разрядный счетчик 64 тактов. Первый тактовый импульс пропускается для того,чтобы в течение nepijoro такта состояние счетчика 64 было О, а это значение используется как адрес первой ячейки памяти в запоминающем блоке 4. Выход счетчика 64 соединен со схемой 65 сраЕ;нения, стробируемой тактовым импульсом. Схема сравнения 65 настраивается по выходам 16 на число тактов в слове без одного. Выход схемы 65 сравнения связан через элемент ИДИ 66 с входом установки в О счетчика 64. Выход элемента ИЛИ 66 также соединен с выходом установки в О счетчика 67, счетный вход которого соединен с выходом т-го разряда счетчика 64. На выходе сче.тчика 67 создается сдвинутый код старших п разрядов адреса для запомина ощего блока 4. Несдвинутый (базовый) код адреса снимается с выхода счетчика 64:п CTapinHx разрядов и m младших разрядов, всего -(m+n) разрядов. Указанные разряды передаются в запоминающий блок 4 через вентили 68, управляемые от схемы 69 блокировки. Слема 69 блокировки необходима для

того, что длина последовательностей, заданная числом тактов, может превышать емкость запоминающего блока 4. Сигнал разрешения на выходе 15 схемы 69 блокировки появляется только при снятом сигнале установки по выходу 18 и удерживается пока код на выходе счетчика 64 изменяется от О до кода адреса последней ячейки памяти запоминающего блока. Сигнал разрешения на втором выходе 70 схемы 69 блокировки, поступающий на вентили 68, удерживается дольше чем на выходе 15 на длительность одного такта. Это необходимо для того, чтобы запоминающий блок 4 выдал данные по последнему адресу. Схема 69 блокировки присоединена к выходу счетчика 64, к линии Такт и к выходу 18 начальной установки.

К выходу стробируемой схемы сравнения 65 присоединена также схема 63 для пропуска первого тактового импульса в слове и схема 71 управления, выход которой подключен к счетному входу счетчика 72 слов и к входу разрешения схемы сравнения 73. Схема 71 управления соединена по входам также с линией Такт и с выходом 18 начальной установки. Функция схемы 71 управления состоит в том, чтобы пропустить первьш тактовый импульс и далее пропускать тактовые импульсы, ближайшие к импульсам на выходе схемы 65 сравнения.

Схема 73 сравнения подключена к выходу счетчика 72 и к выходу 16 настройки. Через элемент ИЛИ 74 выход схемы 73 сравнения связан с входом начальной установки счетчика 72. Выход схемы 73 сравнения соединен и с S-входом триггера 75, на котором выполняется промежуточное запоминание импульса сравнения. Кроме того, им- пульс на выходе схемы 73 сравнения является признаком конца последовательности и передается по выходу 20 в блок 5 управления.

Остальные узлы блока 3 необходимы для создания синхроимпульсов. Наибольшую частоту имеет импульс СИ1 на выходе усилителя-формирователя 76, получающего задержанный тактовый импульс от элемента.77 задержки.

Усилитель-формирователь 78 создает импульс СИ2, привязанный к заданному такту. Вход формирователя 78 присоединен к выходу триггера 79, D-вход которого соединен с выходом схемы 80

282328

сравнения. Эта схема создает импульс в момент равенства кода состояния счетчика 64 и кода настройки на выходе 16. Прием в триггер 79 синхрос низируется импульсом на выходе эле мента 77 задержки. Время задержки подбирается большим, чем сумма задержек в схеме 63, счетчике 64 и схеме 80 сравнения, но меньшим чем эта

to сумма плюс длительность тактового импульса.

Выход элемента 77 задержки соединен также с синхровходом триггера 81, D-вход которого подключен к выJ5 ходу триггера 75. Выход триггера 81 соединен с входом установки в О триггера 75 и с входом усилителя- формирователя 82, на выходе которого образуются импульсы СИЗ.

2Q Вследствие начальной установки в 1 триггера 75 (по выходу 18) импульс СИЗ появляется по первому тактовому импульсу и в моменты окончания всей последовательности. Длительнос25 ти импульсов СИ2 и СИЗ равны длительности такта.

Усилители-формирователи 76, 78, 82 настраиваются на уровни транзисторно-транзисторной или эмиттерно- связа|1ной логики по выходу 16 на30

стройки.

Сигналом по выходу 18 устанавливаются в состояние О триггеры 79 и 81, в состояние 1 триггер 75, и

через схемы ИЛИ 66, 74 - счетчики 64, 67, 72 в состояние О.

Запоминающий блок 4 содержит N субблоков 83, каждый из которых хранит кодовую последовательность для

одного канала. Для увеличения скорости выдачи данных в субблоках 83 осуществляется преобразование параллельного кода в последовательный. В субблок 83 входят две группы запоминающих устройств 84, 85 и коммутатор 86. Выход коммутатора 86 является разрядным выходом запоминающего блока 4.- Информационный вход коммутатора 86 соединен с разрядными выходами.запоминающих устройств 84 и 85. Коммутатор 86 получает разрешение по выходу 16. К выходам настройки коммутатора 86 присоединены m младших разрядов адреса, поступающих по линиям

Адрес из блока 3.

Запоминающие- устройства 84 и 85 (микросхемы памяти) управляются по входу режима от дешифратора 87 с инверсными выходами. Дешифратор 87 получает разрешение по выходу 16 настройки, а информационный вход де- шифратора 87 связан с m младшими разрядами адреса, поступающими по выходу 17 из блока 5 управления.

Если на дешифратор 87 не поступает сигнал разрешения по выходу 16, то на его выходах разрешают запоми- наюлщм устройствам работать в режиме считывания, в противном случае (т.е. если сигнал разрешения поступает на дешифратор 87) О на одном из выходов дешифратора 87 переводит по одному запоминающему устройству 84 и 85 из первой и второй групп в режим записи. Данные на их входы поступают из схемы 88 ввода-вывода данных.

Адресные входы запоминающих устройств 84 первой группы присоединены к коммутатору 89 сдвинутого адреса, а адресные входы запоминаюпщх устройств 85 второй группы - к коммутатору 90 базового адреса. Настройка коммутаторов вьтолняется по выходу 16 Коммутатор 89 сдвинутого адреса пропускает либо п старших разрядов сдвинутого адреса из,блока 3, либо п старших разрядов адреса, приходящих по выходу 17 из блока 5 управления. Коммутатор 90 базового адреса пропускает либо п старших разрядов базового адреса из блока 3, либо те же п старих разрядов адреса из блока 5.

Схема 88 ввода-вывода данных управляется по выходу 16. Онс1 связана выходом 22 с блоком 5 управления. Схема 88 ввода-вывода подключена также к разрядным выходам 13 запоминающего блока 4. Работа запоминающего блока 4 зависит от настройвги по выходам 16. В режиме обмена данными с блоком 5 управления заполнения данными и контрольное считывание идет через схему 88 ввода-вывода. В режиме генерации данные появляются на разрядных выходах 13 по мере изменения кода базового и сдвинутого адреса. В то время, когда коммутатор 86 подключает к своему выходу линии связи от запоминающих устройств 84, идут переходные процессы и устанавливаются данные на выходе запоминаюа №1Х устройств 85. Затем коммутатор 86 подключается к выходам устройств 85 ,. а в запоминающих устройствах 84 подготавливается очередная порция данных.

10

20

22823210

Блок 5 управления (фиг. 6) имеет в основе формирователь 91 команд. Первый вход данных формирователя 91 команд соединен с выходом устройства 92 связи с каналом дистанционного управления. Устройство 92 связи соединено с входом-выходом 21 дистанционного управления, получает признак гтп (готов к приему) формирователя 91 команд и посылает в него признак пр (прием разрешен). Выполнение устройства 92 связи полностью зависит от применяемого интерфейса.

Формирователь 91 команд связан с клавиатурой 93 с долговременным запоминающим устройством 94, с регистром настройки 95 и с запоминающим блоком 4. Клавиатура 93 получает из формирователя команд признак t/k (блокировка клавиатуры) и передает в формирователь 91 команд признак рп (разрешается прием).

Долговременное запоминающее устройство 94 соединено с адресным выходом 17 фррмирователя команд, к которому также подключены регистр 95 настройки и запоминающий блок 4. Долговременное запоминающее устройство 94 и регистр 95 настройки синхронизируются от формирователя команд 91 п;о линии СИ (синхроимпульс). Долговременное запоминающее устройство сохраняет копию кодовой последовательности на время выключения питания генератора.

К выходу 16 регистра 95 настройки подключены устройство 96 индика- и,ии, схема 97 начальной установки, а TaicKe другие блоки генератора. Схема 97 начальной установки создает сигнал начальной установки по выходу 1.8. Этот сигнал снимается на время генерации последовательности как следствие либо сигнала внешнего запуска с входа 19, либо сигнала внутреннего запуска по выходу 16. Восстанавливается сигнал начальной установки после прихода по выходу 20 признака конца последовательности.

.25

30

35

Схема 98 пуска обеспечив-ает выдачу признака П (пуск) формирователя 91 команд по истечение определенной задержки с момента подачи питания. Формирователь 91 команд отрабатывает микропрограмму начального луска и приступает к управлению прибором.

Для перевода формирователя команд из режима местного управления в ре11

жим дистанционного управления на вход формирователя 91 команд подается признак 1 (дистанционное управление) от тумблера 99. На вход формирователя 91 команд поступает также признак К - (конец последовательности).

Блок 12 коммутации (фиг. 7) содержит два коммутатора 100 и 101, элемент И 102, элемент ИЛИ 103 и схему местного управления, состоящую из триггера 104, элемента ЗАПРЕТ 105 и коммутатора 106.

Коммутаторы 100, 101 и 106 настраиваются по выходу 16. Информационные входы коммутаторов 100 и 101 соединены с выходом 14 блока 7 задержки, причем на коммутатор 100 поступают импульсы а , Ь,. .. ,d., привязанные к началу такта (импульс q) и к началу периода опорной частоты (b,...jd), а на коммутатор 101 поступают импульсы, e,f,;..,h, привязанные к срезу импульсов q ,Ъ,. ..,d. Выход коммутатора 100 соединен с С-входом канального триггера 9 и с входом коммутатора 106, а выход коммутатора Г01 соединен с R-входом канального триггера 9 через элементы И 102 и ИЛИ 103 и с вторым входом коммутатора 106.

По импульсу от коммутатора 100 триггер 9 устанавливается в состояние определяемое значением на D-входе Вьжодов 13. В режиме 8Н (возвращение к нулю) по линии настройки ВН/БВН поступает 1, и поэтому триггер 9 сбрасывается импульсом с выхода второго элемента 102.

Схема местного управления необходима потому, что после снятия разрешени по выходу 15 необходимо продолжить формирование на триггер 9 с выхода блока 12 выходного импульса последнего такта. При появлении О на. выходе 15 (сигнал разрешения) снимается удержание в О триггера 104 и дается разрешение на прохождение импульсов от коммутатора 106 через элемент ЗАПРЕТ 105 на S-вход триггера 104. В зависимости от настройки по линии ВН/БВН через коммутатор проходит импульс с выхода либо коммутатора 100, либо коммутатора 101. Триггер 104 через элемент ИЛИ 103 сбрасывает в О триггер 9. Начальная установка триггера 104 в состояние 1 и тем самым триггера 9 в состояние О выполняется по выходу 16 настройки.

)

122823212

Формула изобретения

Многоканальный генератор последовательностей импульсов, содержащий

блок опорной частоты, формирователь тактовых импульсов, блок формирования длины последовательностей, запоминающий блок, блок управления, каналы формирования, каждый из которых состоит из триггера и усилителя-формирователя , первый вход блока управления подключен к шине внешнего запуска, второй вход соединен с шиной управления, генератора, первый выход блока

управления соединен с управляющими входами запоминающего блока, второй выход блока управления - с первыми входами блока опорной частоты, формирователя тактовых импульсов, блока

формирования длины последовательностей, запоминающего блока и входам усилителей-формирователей каждого канала формирования, третий выход блока управления соединен с вторыми,

входами запоминающего блока, четвертый выход блока управления - с вторыми входами блока опорной частоты, формирователя тактовой частоты и блока формирования длины последовательностей, третий выход которого соединен с третьим входом блока управления, выход блока опорной частоты подсоединен через последовательно соединенные формирователь тактовых импульсов и блок формированид длины

последовательностей к третьим входам запоминающего блока, разрядные выходы которого соединены с входами триггеров каналов формирования, о т л и- чающийся тем, что, с целью расширения функциональных возможностей, в него введены блок сдвига импульсов, блок задержки импульсов, а в каждый канал формирования - блок

коммутации, выходы которого через триггер подключены к входу усилителя-формирователя своего канала формирования, первые входы блока коммутации каждого канала формирования соединены с вторыми выходами.блока управления, вторые входы блока коммутации каждого канала формирования соединены с выходами -блока задержки импульсов, третий вход каждого блока коммутации соединен с дополнительным выходом блока формирования длины последовательностей, первый вход блока задержки соединен с четвертым

3122823214

выходом блока управления, второйвход которого соединен с вторым до- вход блока задержки - с дополнитель-полнительным выходом формирователя ным выходом формирователя тактовыхтактовьгх импульсов, а второй и тре- импульсов, третьи входы блока за-тий входы блока сдвига импульсов - держки импульсов соединены с выхода- gсоответственно с вторым и четвертым ми блока сдвига импульсов, первьгй выходами блока управления.

-ЧИ ГТ

i «

Г-Г « 1 НСёУ;

л

Го/r/n

Adiife

СН

| название | год | авторы | номер документа |

|---|---|---|---|

| Ультразвуковое сканирующее и фокусирующее устройство | 1987 |

|

SU1539647A1 |

| Устройство для регистрации ритма сердечной деятельности и характера его изменений | 1978 |

|

SU784867A1 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

Изобретение мо5кет быть использовано для контроля систем цифровой связи, цифровых интегральных схем, блоков памяти, систем диагностики. Цель изобретения - расширение функциональных возможностей. Устройство содержит блок 1 опорной частоты, формирователь 2 тактовых импульсов, блок 3 формирования длины последовательностей, запоминающий блок 4, блок 5 управления, блок 6 сдвига импульсов, блок 7 задержки импульсов, каналы 8 формирования. Каждый канал 8 содержит триггер 9,- усилитель-формирователь 10 и блок 12 коммутации. Расширение функциональных возможностей достигается за счет введения блока 6 сдвига импульсов, блока 7 задержки импульсов, а в каждый канал 8 формирования введен блок 12 коммутации, что позволит дополнительно изменять положение импульсов в такте последовательности. В описании также приведены примеры конкретного выполнения блока 1 опорной частоты, формирователя 2 тактовых импульсов, блока 6 сдвига импульсов, блока 7 задержки импульсов, блока 3 формирования длины последовательностей импульсов, запоминающего блока 4, блока 5 управления, блока 12 коммутации. 7 ил. (Л iV N3 ю 30 го : ю

| Многоканальное устройство для формирования последовательностей импульсов переменной длительности | 1979 |

|

SU788358A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-30—Публикация

1983-10-27—Подача