I

Изобретение относится к области электротехники и может быть применено в устройствах для контроля и испытаний, например в устройствах для контроля электрических соединений.

Известны устройства для формирования импульсов, папример, в устройствах совмещения записи и считывания, содержащие параллельно соединенные регистры сдвига, выходной блок и распределитель.

Однако такие устройства не могут быть использованы в системах контроля электриче.ских соединений для формирования импульсов дополиения, «проталкивающих опросные коммутаторы, подключенные к проверяемым цепям, на одну из которых подключается обычно источник сигнала. Такое «проталкивание позволяет значительно сократить время контроля объекта и исключить повторные опросы цепей.

Целью изобретения является расщирение функциональных возможностей и увеличение быстродействия устройства.

С этой целью в предложенное устройство для формирования импульсов в системе контроля электрических соединений введены блок ламяти и три схемы задержки. Входы записи блока .памяти подсоединены к выходам второго регистра, входы считывания - к выходам первого регистра и ключа, входы перезаписи - к выходу первой схемы задержки, а выходы - ко входам выходного блока. Вход первой схемы задержки соединен с выходом выходного блока, а выход - со входом второй схемы задержки, выход которой подключен к тактовому входу первого регистра и к первому входу распределителя, второй вход которого соединен с опросным входом устройства и через третью схему задержки - со вторым входом первого регистра. Кроме того, блок памяти устройства содержит основные и дополнительные ячейки памяти. Входы основных ячеек памяти подключены ко входам записи и считывания блока паамяти, а дополнительных - к выходам основных ячеек и ко входам перезаписи блока памяти. Выход дополнительных ячеек подключен ко входам перезаписи основных ячеек памяти.

Это позволяет сократить общее время испытаний. Эффективность предлагаемого устройства возрастает со сложностью проверяемого объекта, например с увеличением числа разветвлений в соединении электрических цепей.

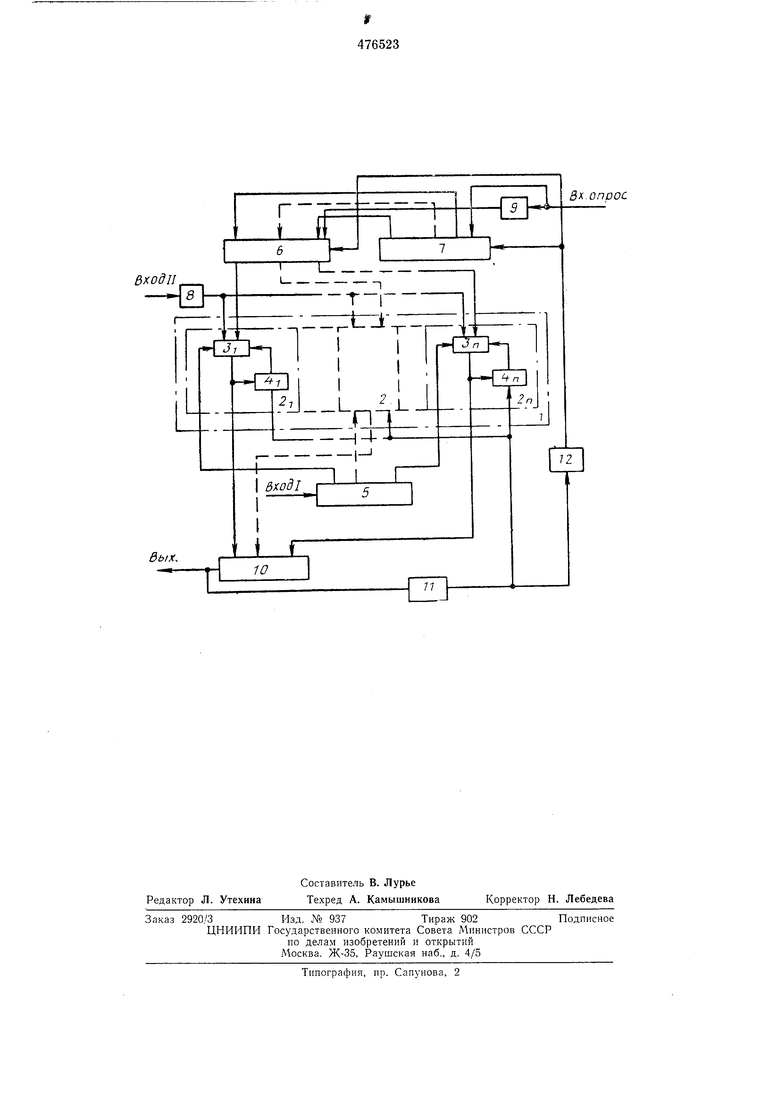

На чертеже представлена блок-схема устройства.

Устройство содержит блок .памяти 1 из Я разрядов 2, каждый из которых выполнен из основной 3 и дополнительной 4 ячеек, регистр записи 5, регистр считывания 6, распределитель 7, ключ 8, схему задержки 9, выходной блок 10 и схемы задержки 11 и 12.

Устройство работает следующим образом.

После подачи питания по команде «Сброс блок памяти 1, регистр записи 5, регистр считывания 6 и распределитель 7 устанавливаются в «О.

При появлении тактовых сигналов на входе 1 запускается регистр записи 5, выдающий команды записи поразрядно в блок 1, и в ячейки 3 записывается «полусигнал «1. Если при этом присутствует .входной сигнал на входе II, запускающий ключ 8, который управляет записью «полусигналов «1 ячеек 3 блока 1, то в ячейки 3 блока 1, на обоих входах которых окажутся «полусигналы «1, запищутся «1.

По окончании команд на входах I и II приходит сигнал «Онрос, поступающий на вход распределителя 7, который поразрядно управляет записью разрещающей «1 в регистре считывания 6, запускает схему задержки 9, и последняя выдает сигнал на тактовый вход регистра 6.

Выходной сигнал соответствующего разряда регистра 6 списывает в «О ячейку 3 блока 1, которая, срабатывая, записывает «1 в соответствующую ячейку 4 блока 1 и запускает выходной блок 10, выдающий импульсный сигнал на выход. Одновременно выходной блок 10 запускает схему задержки И, списывающую в «О все ячейки 4 блока 1. В результате ячейка 4 блока 1, в которой была записана «1, срабатывает и восстанавливает «1 в соответствующей ячейке 3 блока 1. Одновременно схема задержки 11 запускает схему задержки 12, которая выдает задержанный сигнал на второй тактовый вход регистра 6. На выходе следующего разряда регистра 6 появляется сигнал, описывающий следующую по номеру ячейку 3 блока 1 и, если в ней была ранее записана «1, устройство работает аналогично.

Импульсы с выхода схемы задержки 12, поступают на второй вход распределителя 7 и просчитываются. Если в этой ячейке 3 блока 1

не была ранее записана «1, работа прекращается до появления сигналов на входах I и II.

Таким образом, на выходе устройства при опросе .формируются одиночные (или серия) импульсы, функционально зависимые от совпадения сигналов на входах I и II. При этом число их за одну команду опроса соответствует числу непрерывных совпадений сигналов на входах I и II (без пропуска разрядов).

Блок 1 опрашивается со следующего «пустого разряда этого блока, что сокращает общее время его полного опроса.

Предмет изобретения

1.Устройство для формирования импульсов в системах контроля электрических соединений, содержащее распределитель, выходы которого соединены со входами первого регистра, выходной блок, второй регистр и ключ, отличающееся тем, что, с целью расщирения функциональных возможностей и увеличения быстродействия устройства, в него введены блок памяти и три схемы задержки; входы записи блока памяти подсоединены к выходам второго регистра, входы считывания - к выходам первого регистра и ключа, входы перезаписи - к выходу первой схемы задержки, а выходы - ко входам выходного блока; вход

первой схемы задержки соединен с выходом выходного блока, а выход - со входом второй схемы задержки, выход которой подключен к тактовому входу первого регистра и к первому входу распределителя, второй вход которого соединен с опросным входом устройства и через третью схему задержки - со вторым входом первого регистра.

2.Устройство по п. 1, отличающееся тем, что блок памяти содержит основные и дополнительные ячейки памяти; причем входы основных ячеек подключены ко входам записи и считывания блока памяти, а даполнительных - к выходам основных ячеек и ко входам перезаписи блока памяти; выход дополнительных ячеек подключен ко входам перезаписи основных ячеек памяти.

476523

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| ПЕРЕДАЮЩЕЕ УСТРОЙСТВО СИСТЕМЫ ТЕЛЕИЗМЕРЕНИЯ | 1973 |

|

SU387414A1 |

| Устройство для опроса информационных каналов | 1980 |

|

SU955067A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| СЛЕДЯЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2085026C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ СТАРТСТОПНЫХ ТЕЛЕГРАФНЫХ АППАРАТОВ С АППАРАТУРОЙ ТЕЛЕГРАФНЫХ КАНАЛОВ СВЯЗИ | 1967 |

|

SU224555A1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ИНФОРМАЦИИ | 1967 |

|

SU222908A1 |

| Устройство для тактильного восприятия информации | 1982 |

|

SU1080188A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1481862A1 |

Авторы

Даты

1975-07-05—Публикация

1973-01-05—Подача