соединены соответственно с входом шифратора адреса и первым входом бло ка формирования адреса, выход шифра тора адреса подключен к вторым входам сумматоров начального и конечного адреса, выходы которых соединены соответственно с информационным входом счетчика основного адреса и первым входом блока сравнения, второй вход блока сравнения подключен к выходу счетчика основного адреса, а выход - к входу элемента ИЛИ-НЕ, выход которого соединен с вторыми входами элементов И первой группы, первый и второй входы распределителя им пульсов подключены соответственно к выходу генератора тактовых импульсов и выходу маркеров входного регистра, второй, третий, четвертый и пятый выходы распределителя импуль сов соединены с тактовыми входами со ответственно счетчиков основного адреса, выходного адреса, буферного адреса и адреса регистра, прямые и инверсные выходы первого, второго и третьего триггеров режима подключены к входам записи и считывания соответ ственно блока основной памяти, блока выходной памяти и блока буферной памяти, вторые входы элементов И второй группы соединены с выходом блока основной памяти, а выходы - с первым входами элементов ИЛИ группы, вторые входы которых подключены к выходу бл ка буферной памяти, выходы элементов ИЛИ группы соединены с информаци онным входом блока выходной памяти, адресный вход которого подкгиочен к выходу счетчика выходного адреса, вы ход счетчика адреса регистра соедине с первым адресным входом блока регис ров, информационный вход которого под ключен к выходу ключа входного регис ра, а выходы - к второму и третьему входам блока формирования адреса, вторые входы элементов И третьей груп пы соединены с выходом блока формирования адреса, а выходы этих элементов подключены к информационному входу счетчика (буферного адреса, выход которого соединен с адресным входом блока буферной памяти, вторым адресным входом блока регистров и первым входом элемента И выход третьего триггера режима подключен к управляющему входу блока регистров и второму входу элемента И, выход которого соединен с входом элемента задержки, вход входного регистра подключен к 1 62 информационному входу процессора, а выход данных - к информационному .входу блока буферной памяти. 2. Процессор по п. 1, о т л и чающийся тем, что блок местного управления содержит триггер ключа, шифратор адреса, регистр адреса, память микрокоманд, регистр микрокоманд, дешифратор, группу элементов И, счетчик, схему сравнения, элемент ИЛИ, элемент И и память признаков, при этом входы установки и сброса триггера ключа соединены с первым входом блока, а прямой и инверсный выходы - с первыми входами соответственно шифратора и элементов И группы, выход шифратора подключен к первому входу регистра адреса, адресный вход памяти микрокоманд соединен с выходом регистра адреса, а выход - с входом регистра микрокоманд, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы которого подключены соответственно к второму входу шифратора адреса, входу дешифратора, трютьему, четвертому и пятому выходам блока, первому входу памяти признаков, второму входу регистра адреса и вторым входам элементов И группы, выходы дешифратора соединены с первым и вторым выходами блока, третьи входы элементов И группы подключены к второму входу блока, третий вход блока соединен с первым входом счетчика, первым входом схемы сравнения, третьим входом регистра адреса, первым входом элемента ИЛИ и вторым выходом блока, выходы элементов И группы подключены к третьему входу шифратора адреса и вторым входам элемента ИЛИ и памяти признаков, четвертый и пятый входы шифратора адреса соединены соответственно с первым выходом схемы сравнения и памяти признаков, четвертый вход блока подключен к второму входу счетчика и третьему входу элемента ИЛИ, пятый вход блока соединен с третьим входом счетчика и четвертым входом элемента ИЛИ, шестой вход блока подключен к четвертому входу счетчика и первому входу элемента И, пятый вход счетчика соединен с прямым выходом триггера ключа, первый и второй вйходы счетчика подключены соответственно к второму входу схемы сравнения и третьему входу памяти признаков, выход схемы сравнения соединен с пятым входом элемента ИЛИ, выход второму входу 1037262 которого, подключен к мента И соединен с упрарляюШим вхоэлемента И, а выход эле- дом памяти микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

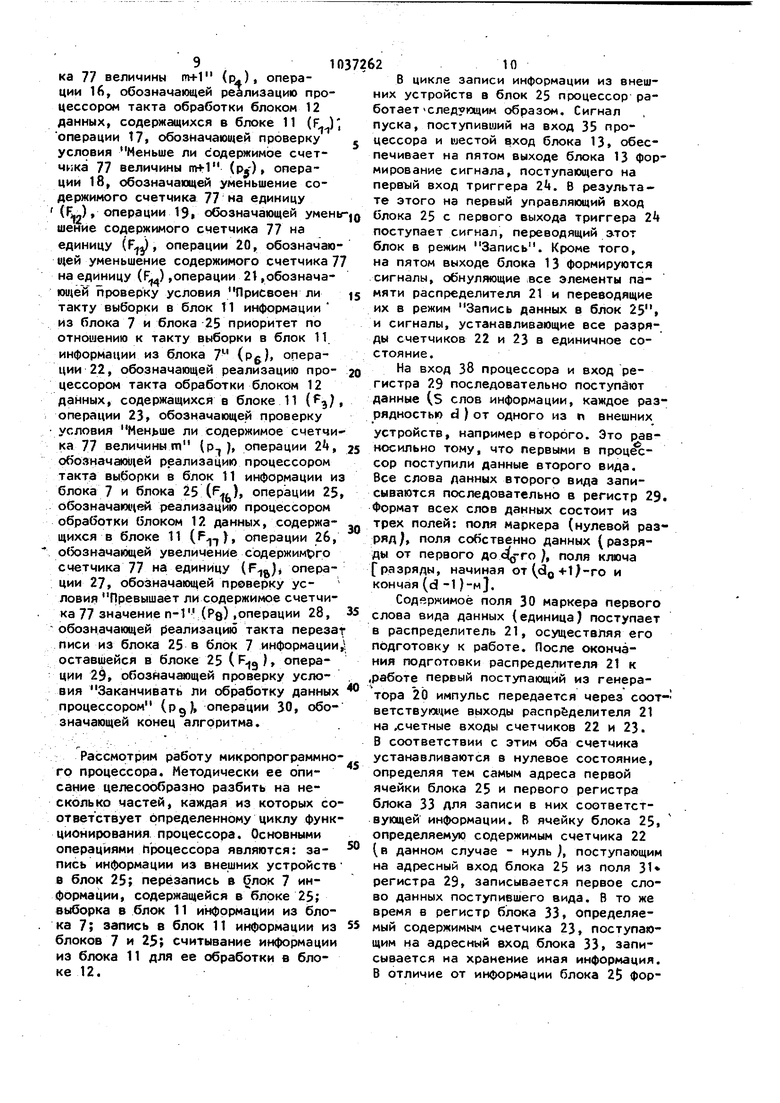

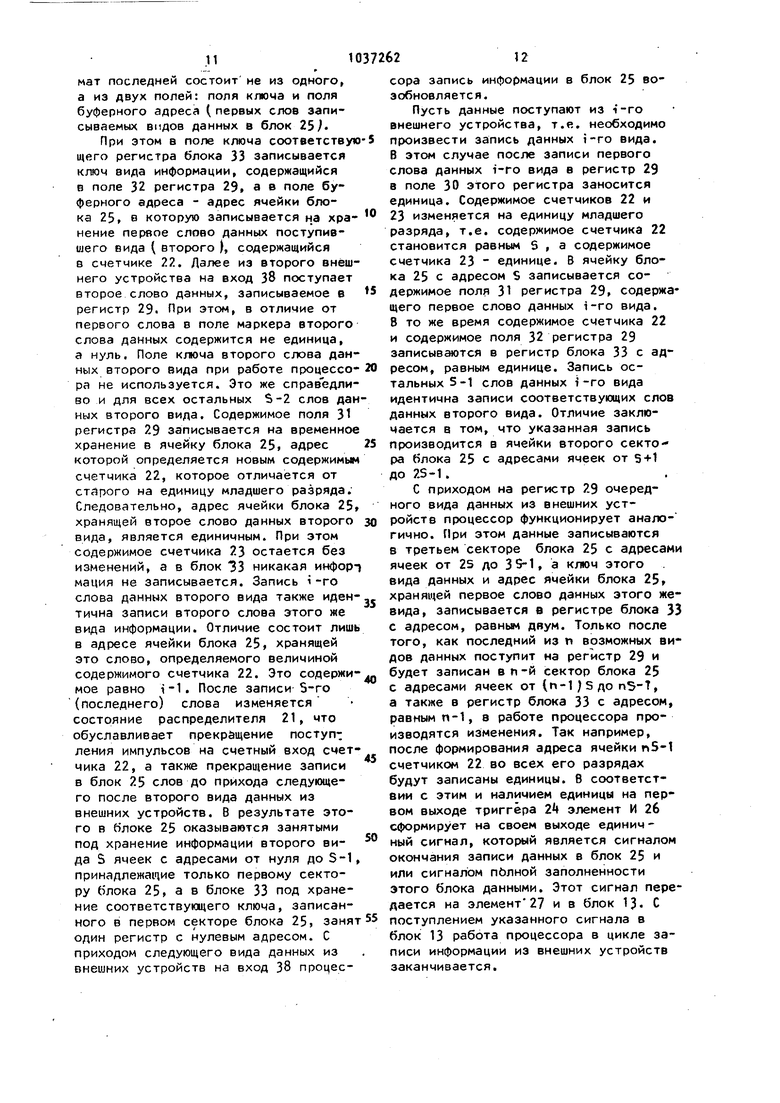

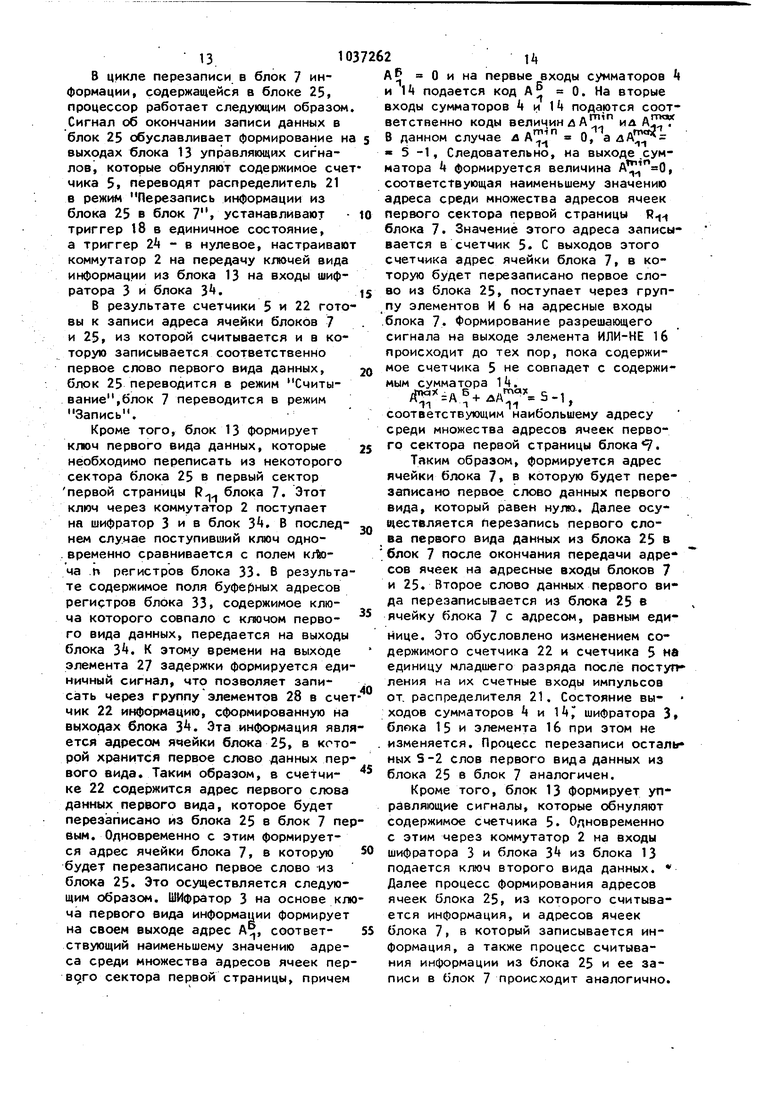

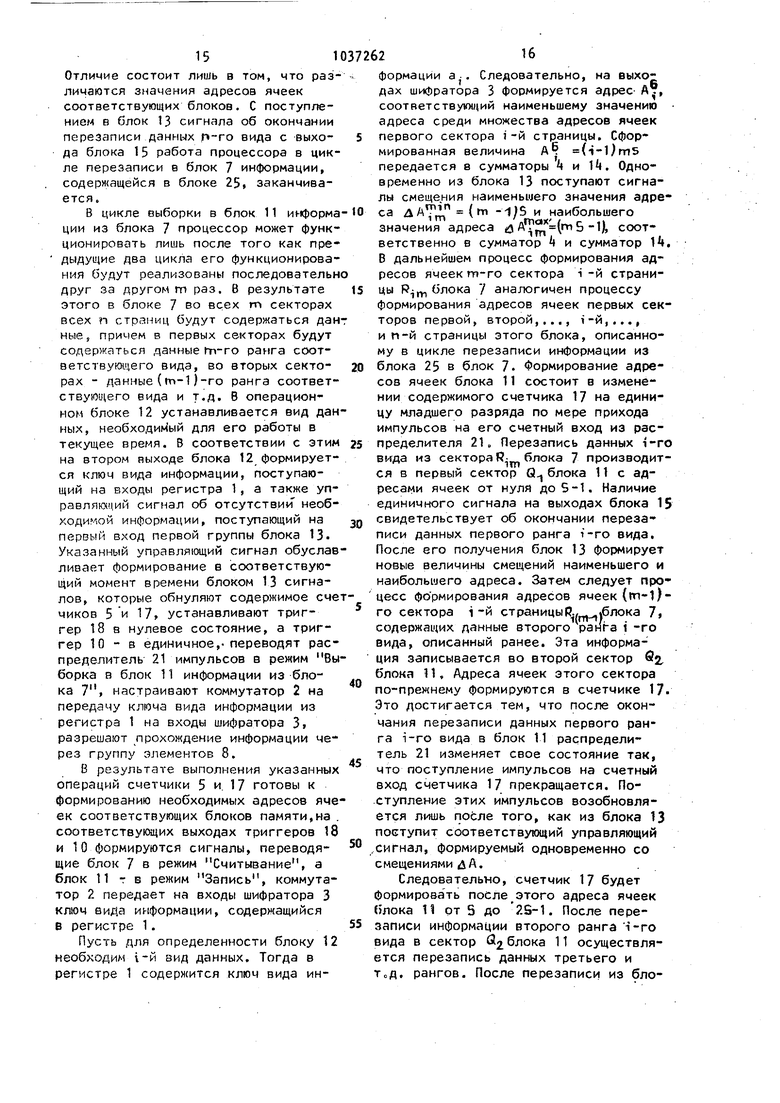

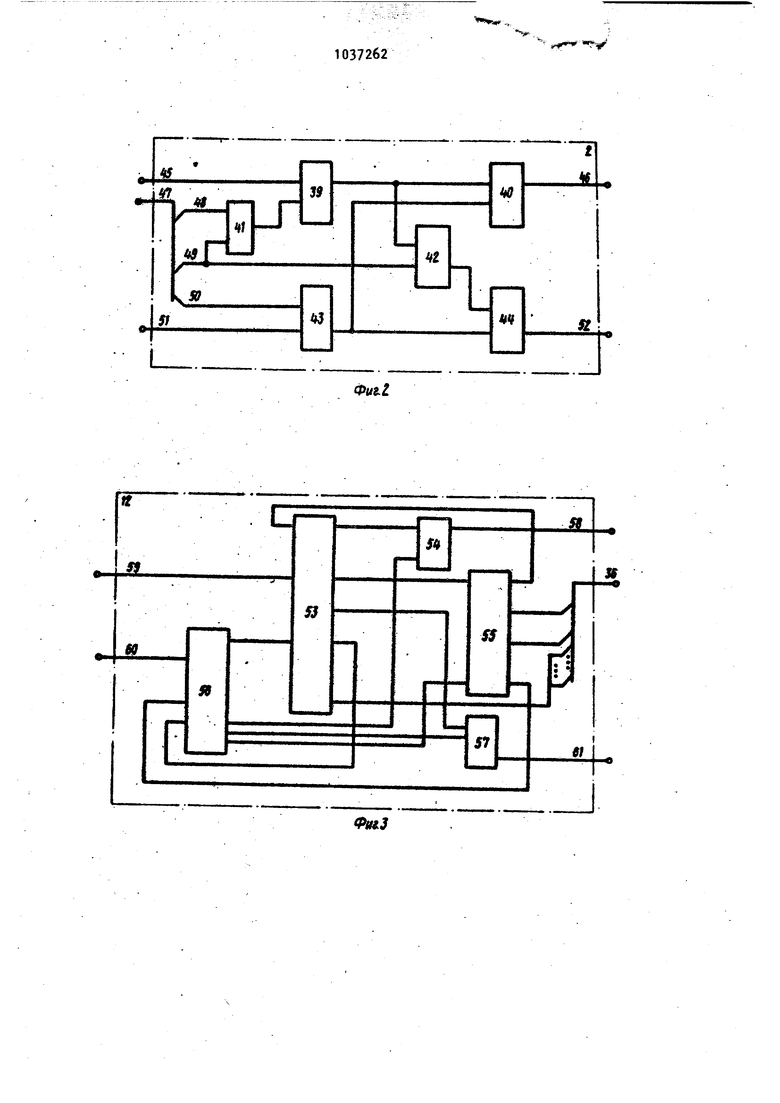

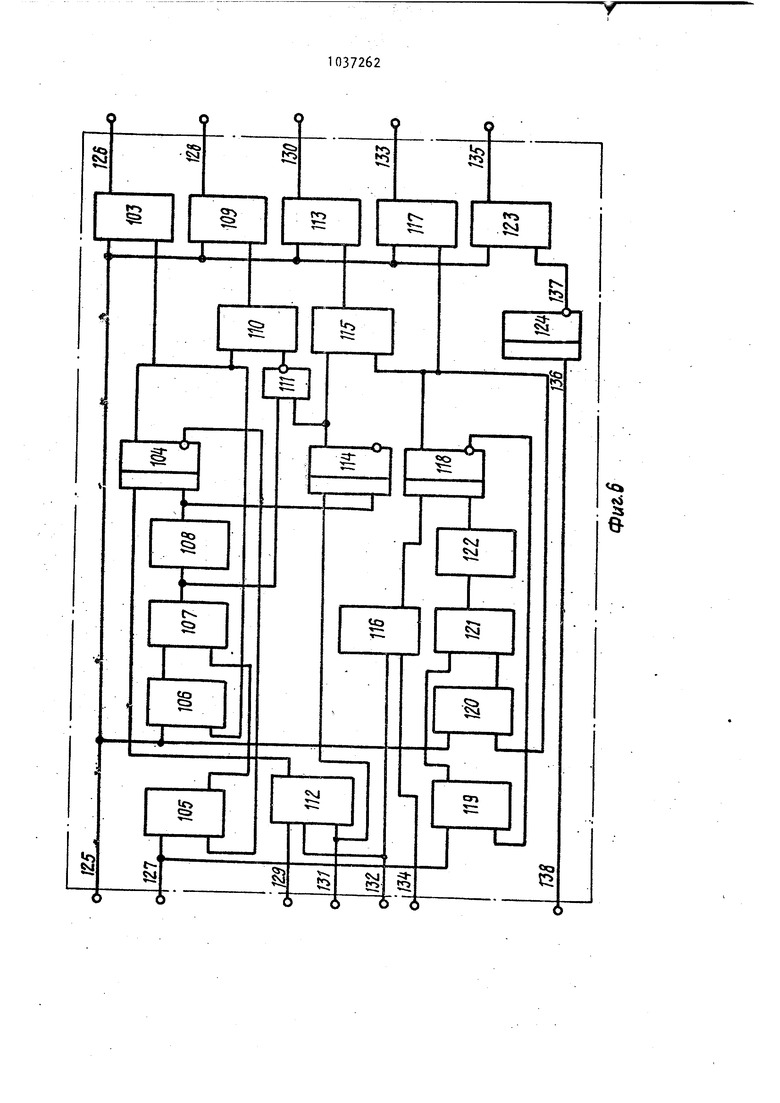

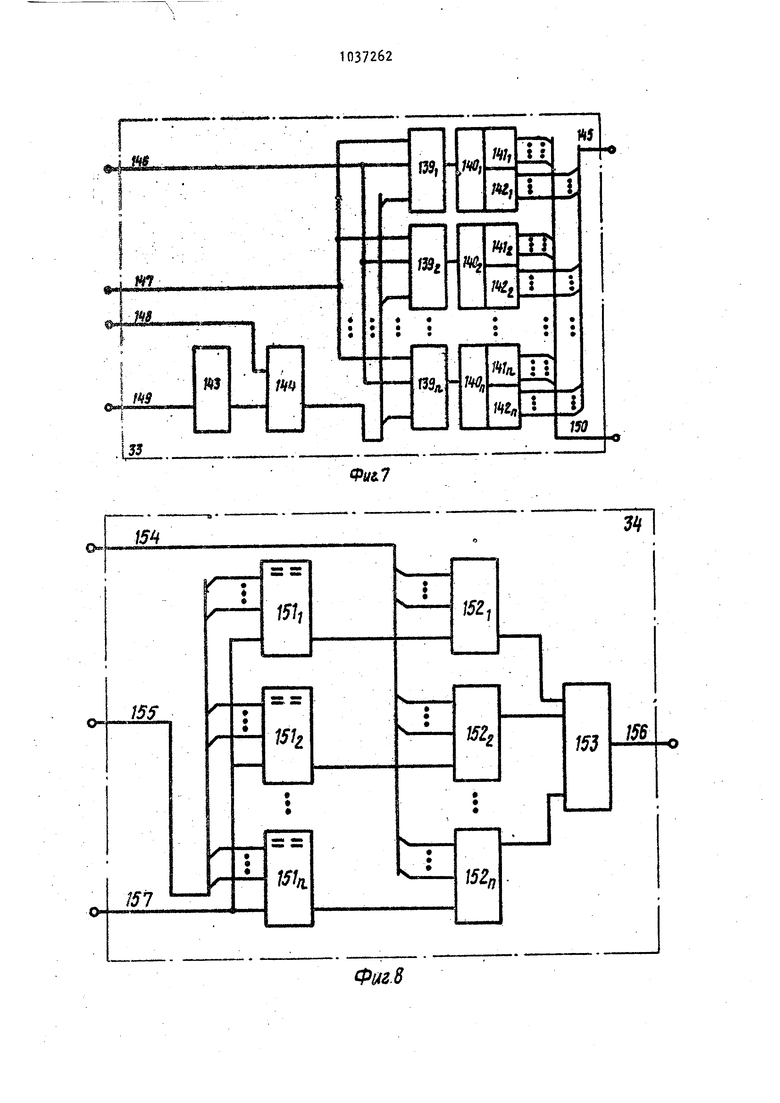

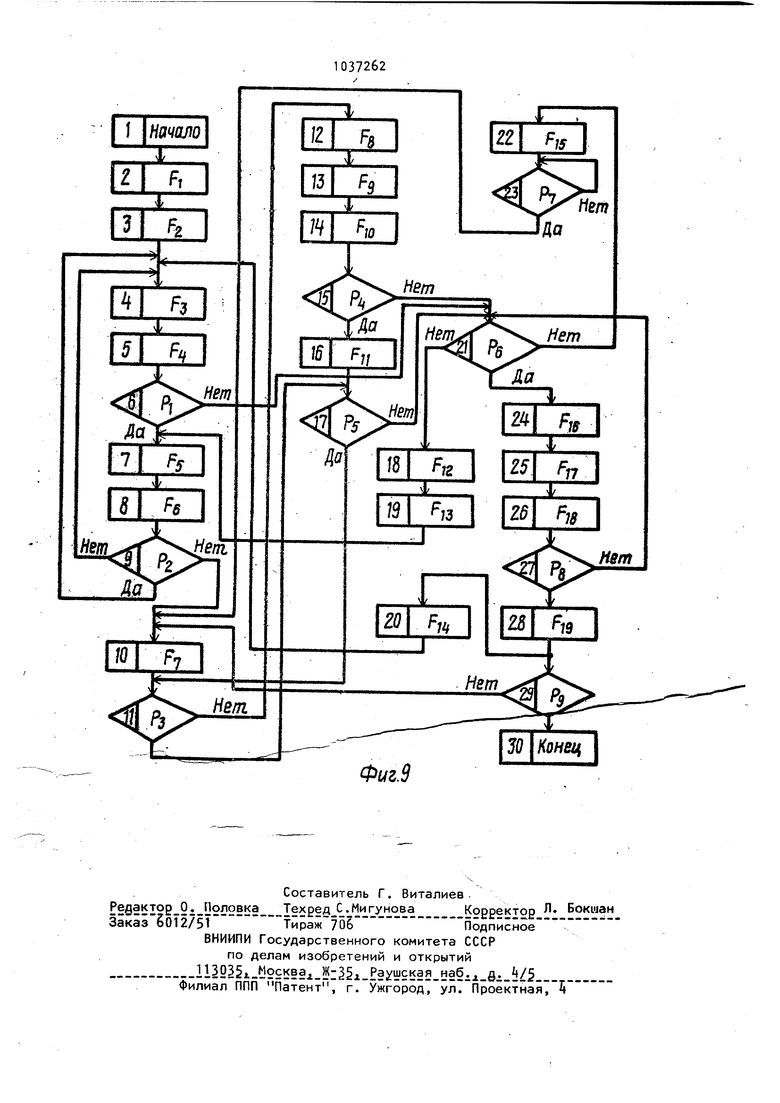

1. МИКРОПРОГРАММНЫЙ ПРОЦЕССОР, содержащий счетчик основного адреса, первую группу элементов И, блок основной памяти, блок выходной памя-. ти, операционный блок, блок управгюния, генератор тактовых импульсов и блок буферной памяти, при этом выход счетчика основного адреса соединен с первыми входами элементов И первой группы, выходы которых подключены к адресному входу блока основной памяти, информационный вход блока основной памяти соединение выходом блока буферной памяти, выход блока выходной памяти подключен к информационному входу операционного блока,управляющий вход которого соединен с выходом блока управления, а первый выход с выходом результата процессора, причем первый вход блока управления подключен к.первому входу операций процессора, отличающийся тем, что, с целью, повышения производительности и расширения функциональных возможностей, он содержит регистр информации, коммутатор, шифратор адреса. сумматоры начального и конечного адреса, блок местного управления, блок сравнения, элемент ИЛИ-НЕ, три триг: гера режима, вторую и третью группы элементов И, группу элементов ИЛИ, счетчик выходного адреса, счетчик буферного адреса, счетчик адреса регистра, распределитель импульсо, входной регистр, блок регистров, блок формирования адреса, элемент И и элемент задержки, выход которого соединен с первыми входами элементов И третьей группы, первый, второй, третий, четвертый, и шестой входы блока местного уп{ авления подк/ночены соответственно к выходу регистра информа-D ции, второму выходу операционного блока, второму входу операций процессора, выходу элемента И, выходу блока сравнения и первому выходу распределителя импульсов, входы регистра информации соединены с вторым выходом операционного блока, первый, второй и третий входы коммутатора подключены соответственно к выходу ре гистра информации, первому и второму выходам блока местного управления, третий и четвертый выходы которого соединены с первыми входами соответственно сумматора начального адреса и сумматора конечного адреса, пятый выход блока местного управления подключен к первой группе входов распределителя импульсов, установочным входам счетчиков основного адреса, выходного Адреса, буферного адреса и адреса регистра, входам сброса и установки триггеров режима, вто-, рому входу блока управления и первым входам элементов И второй группы, первый и второй выходы коммутатора

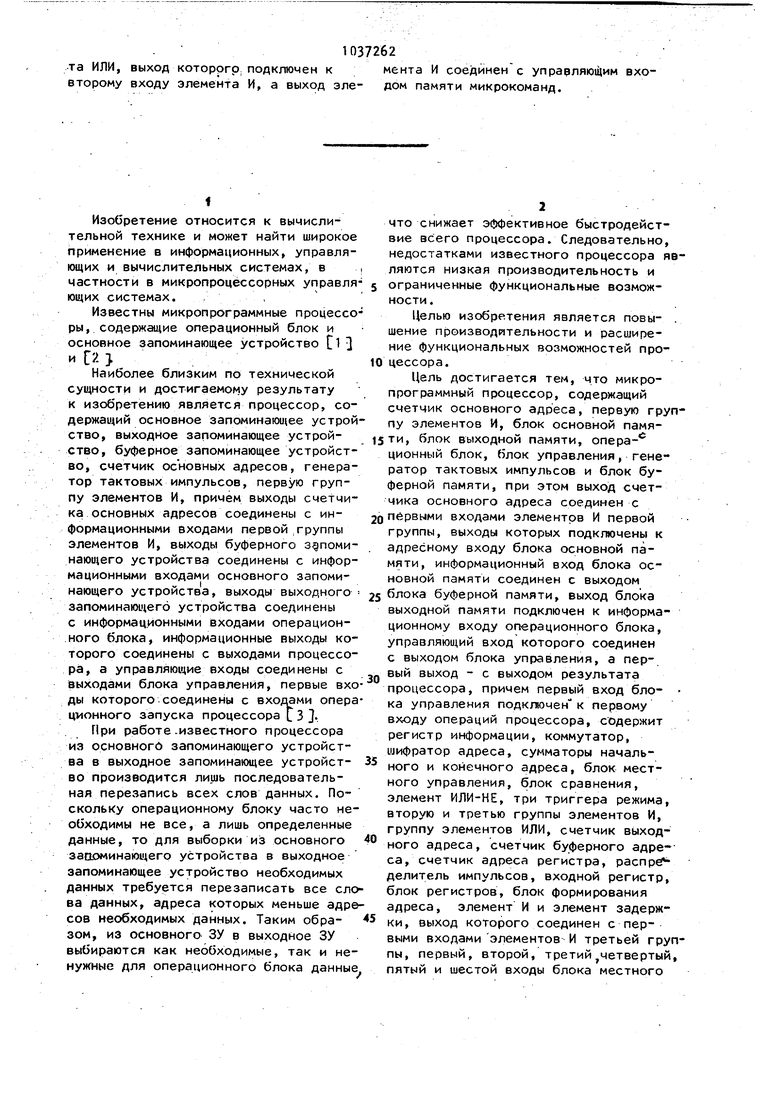

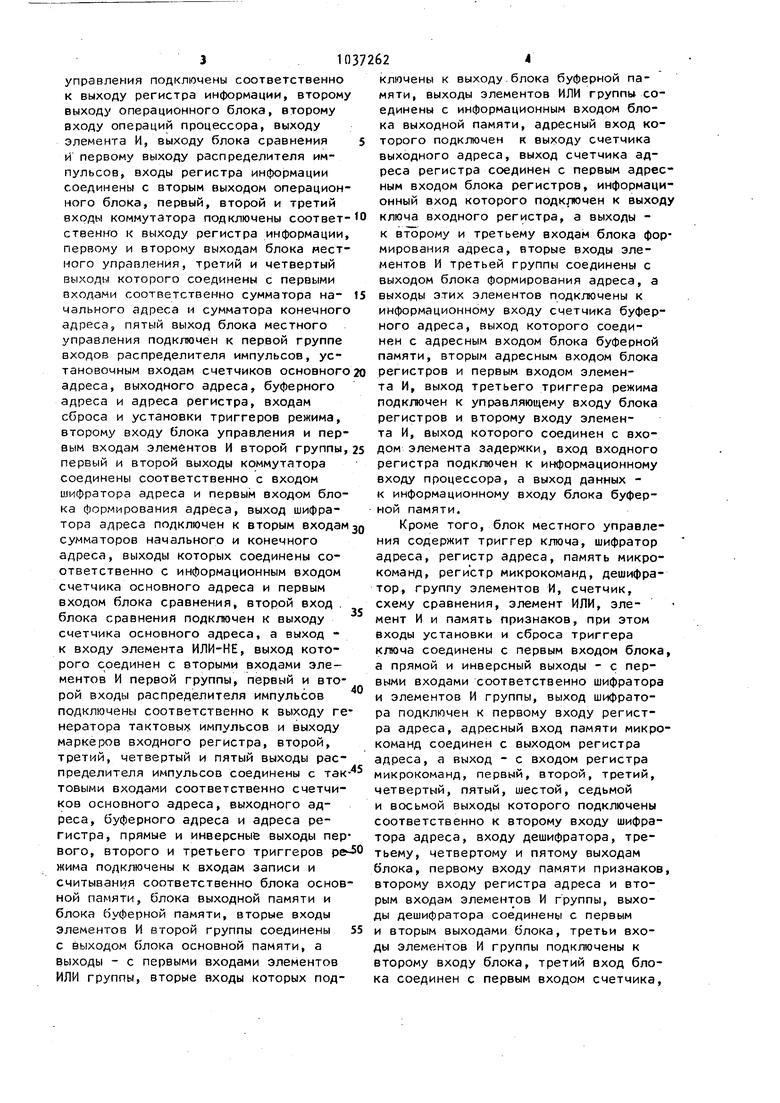

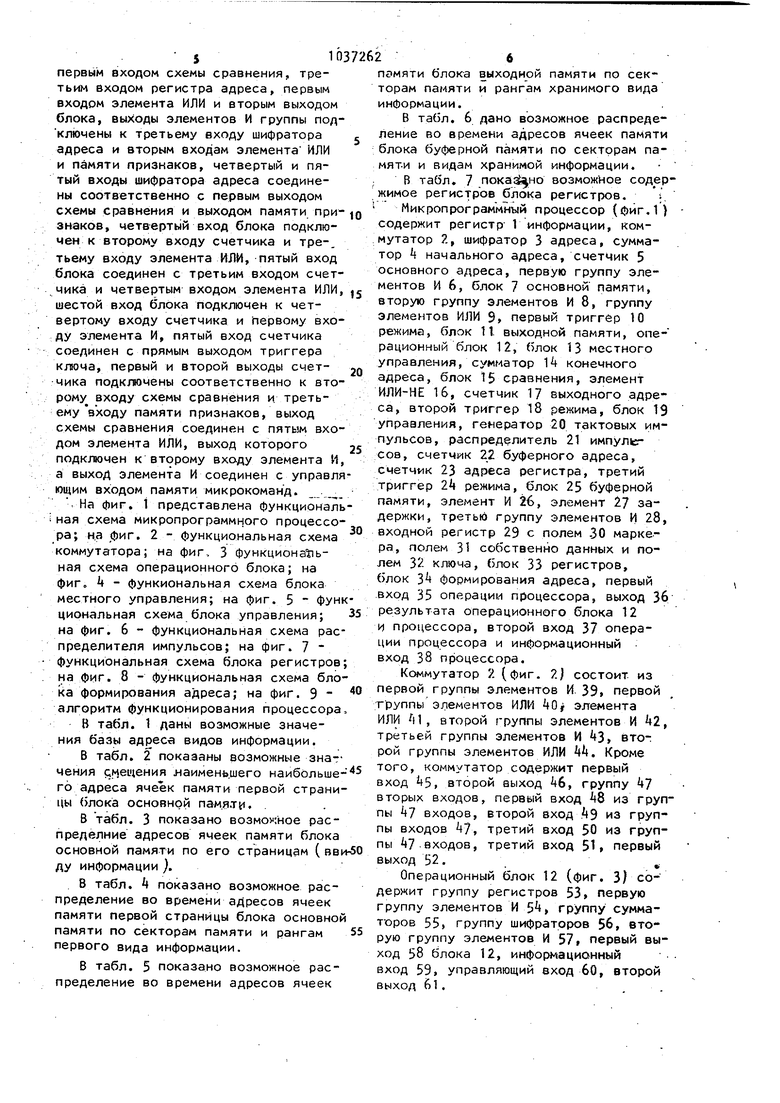

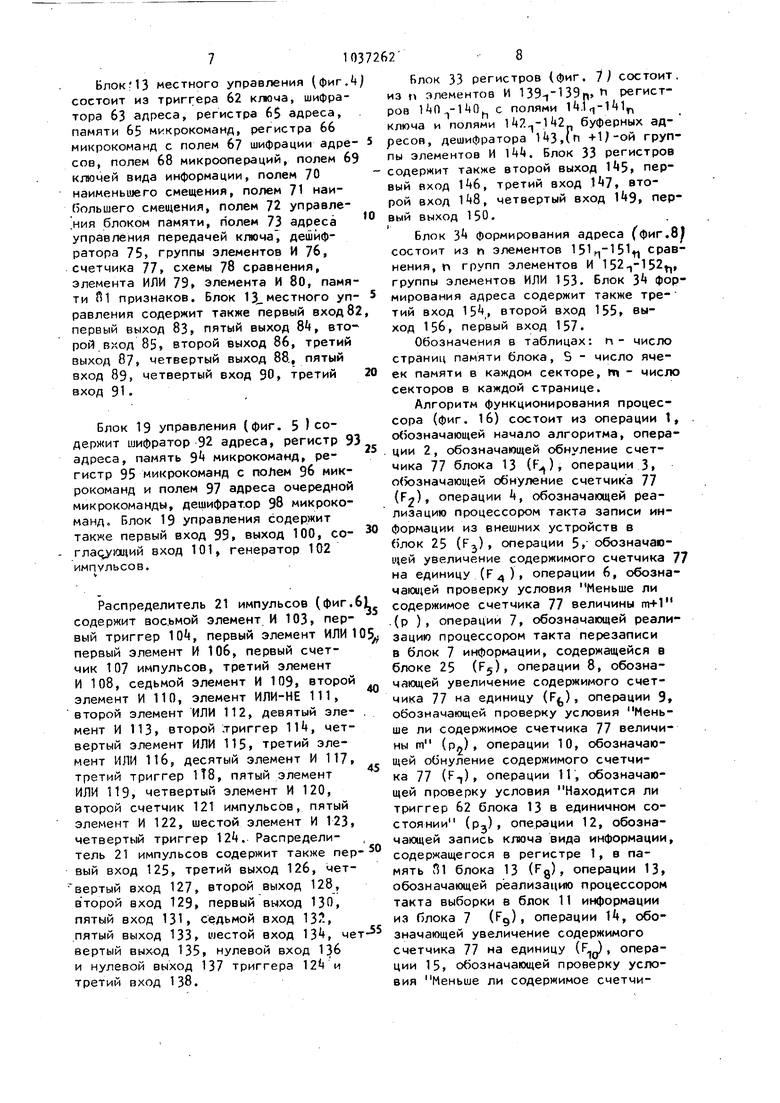

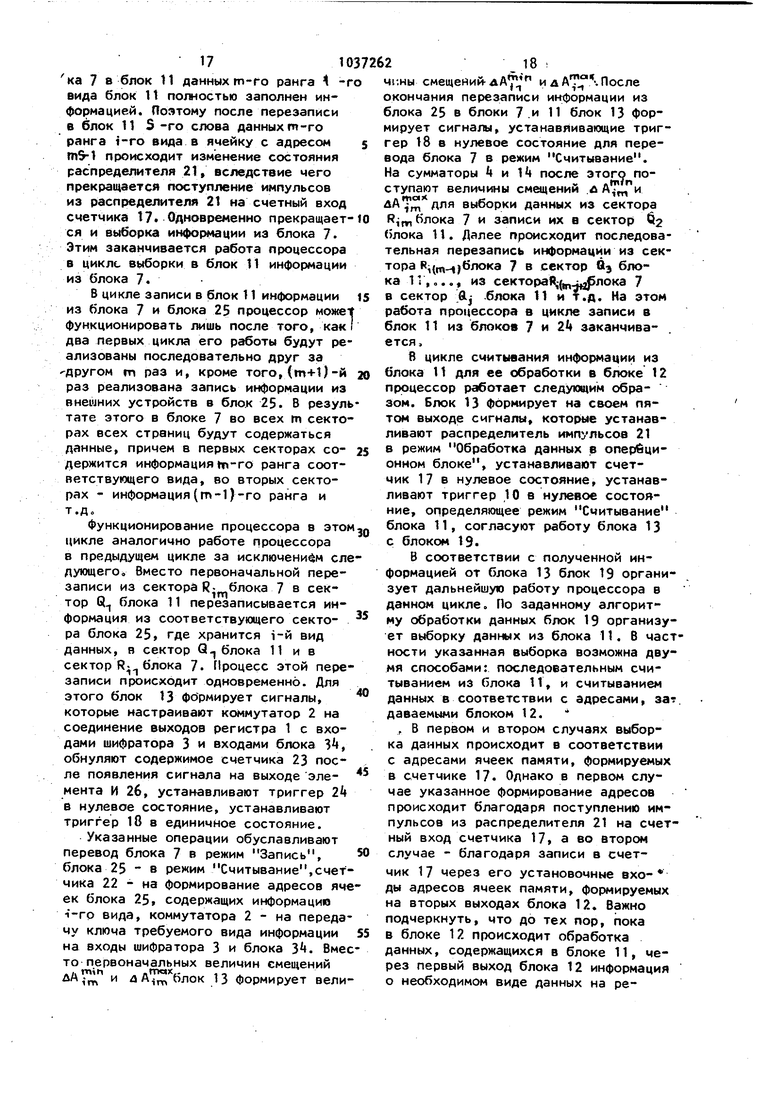

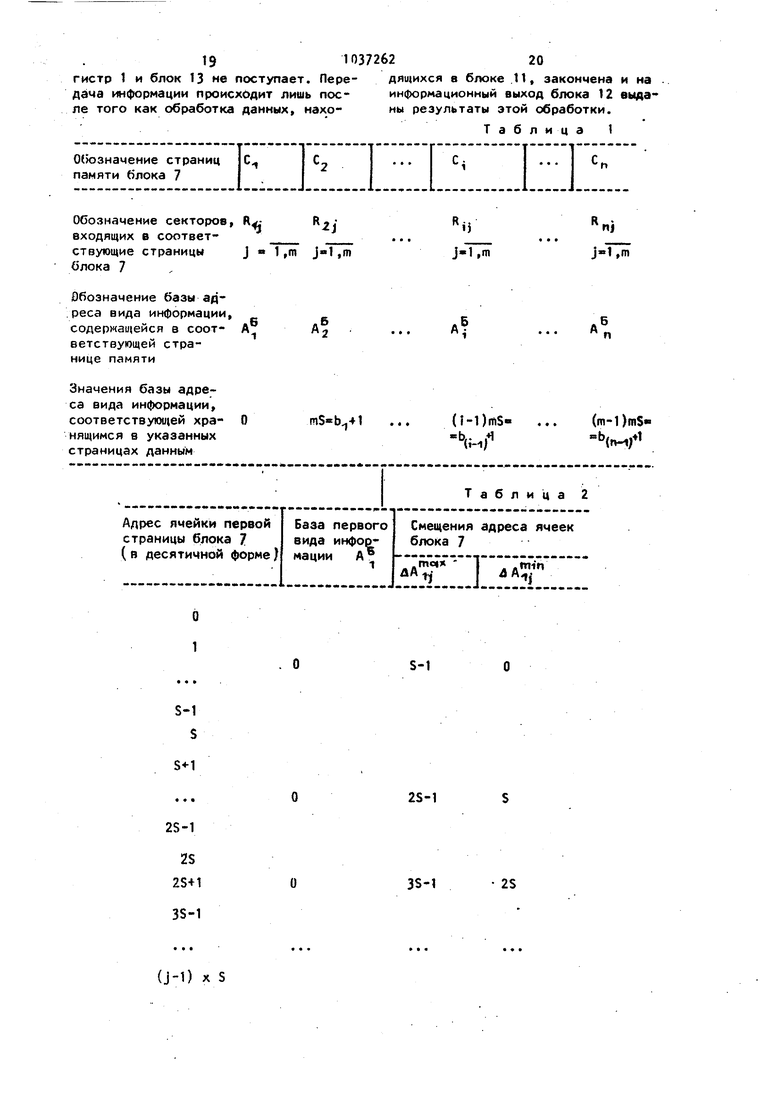

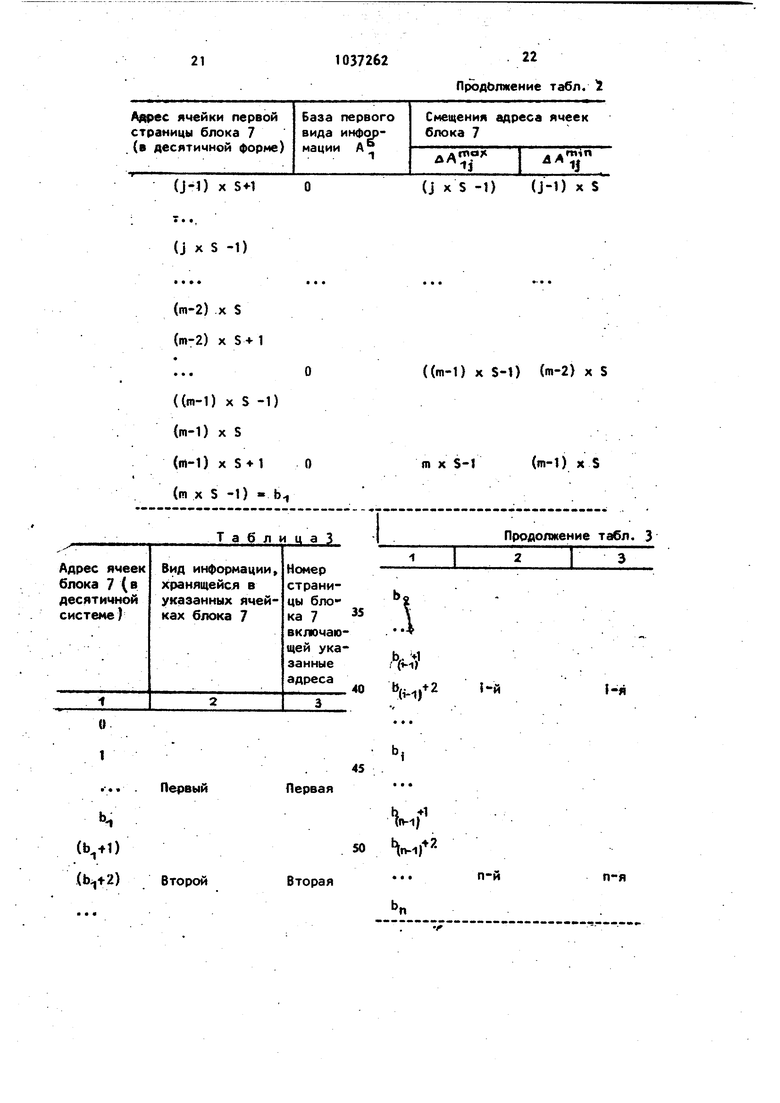

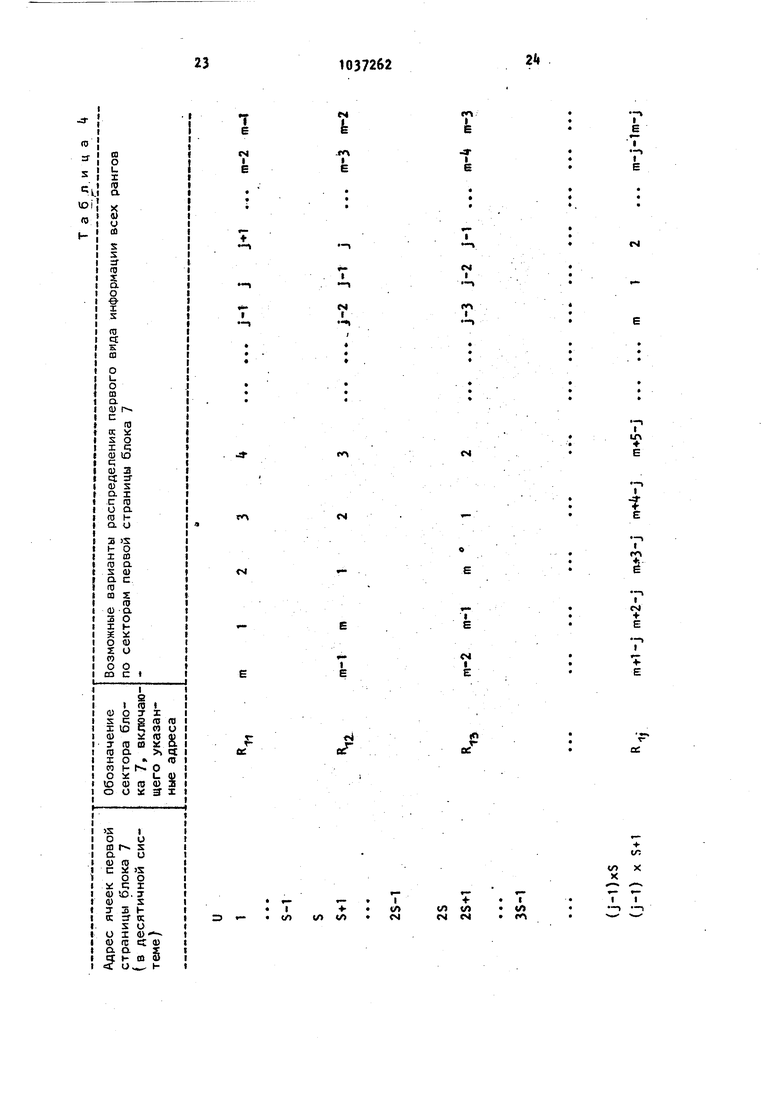

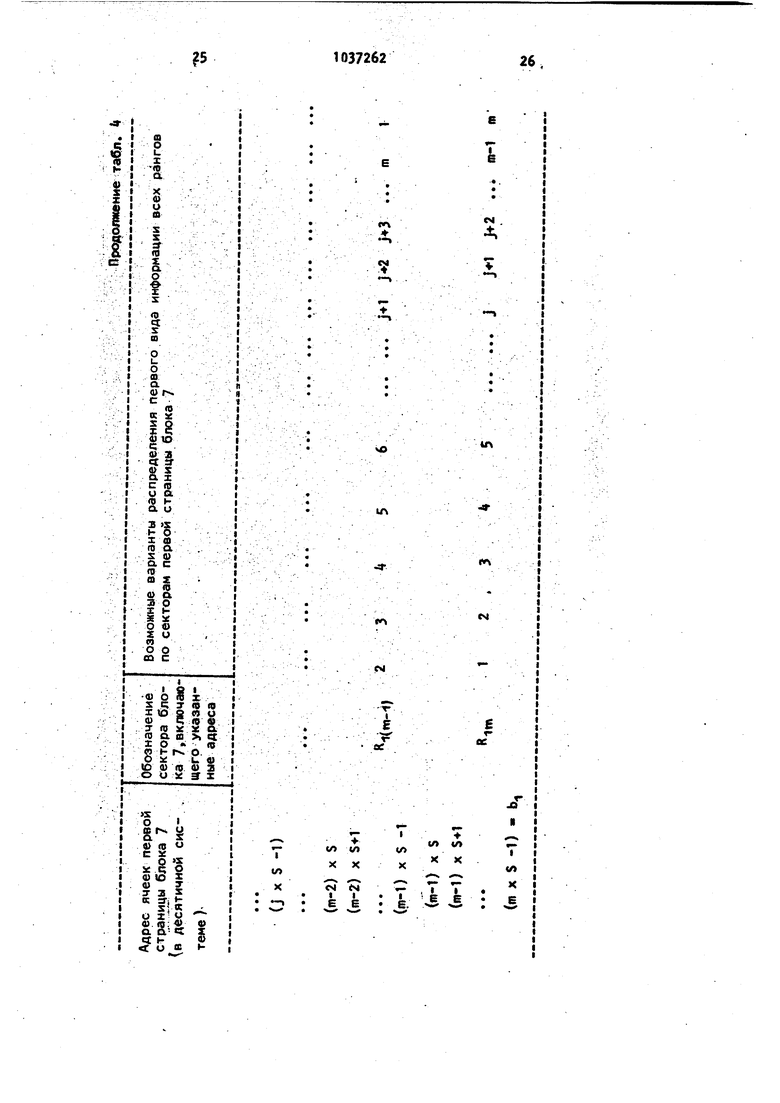

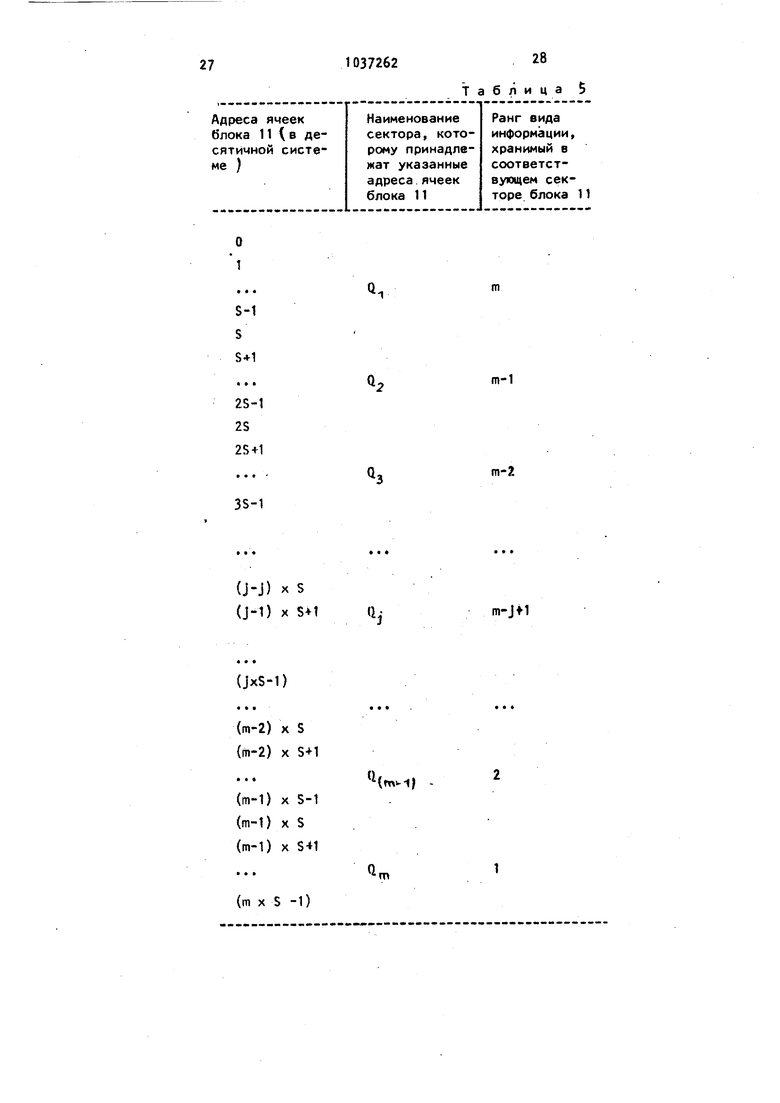

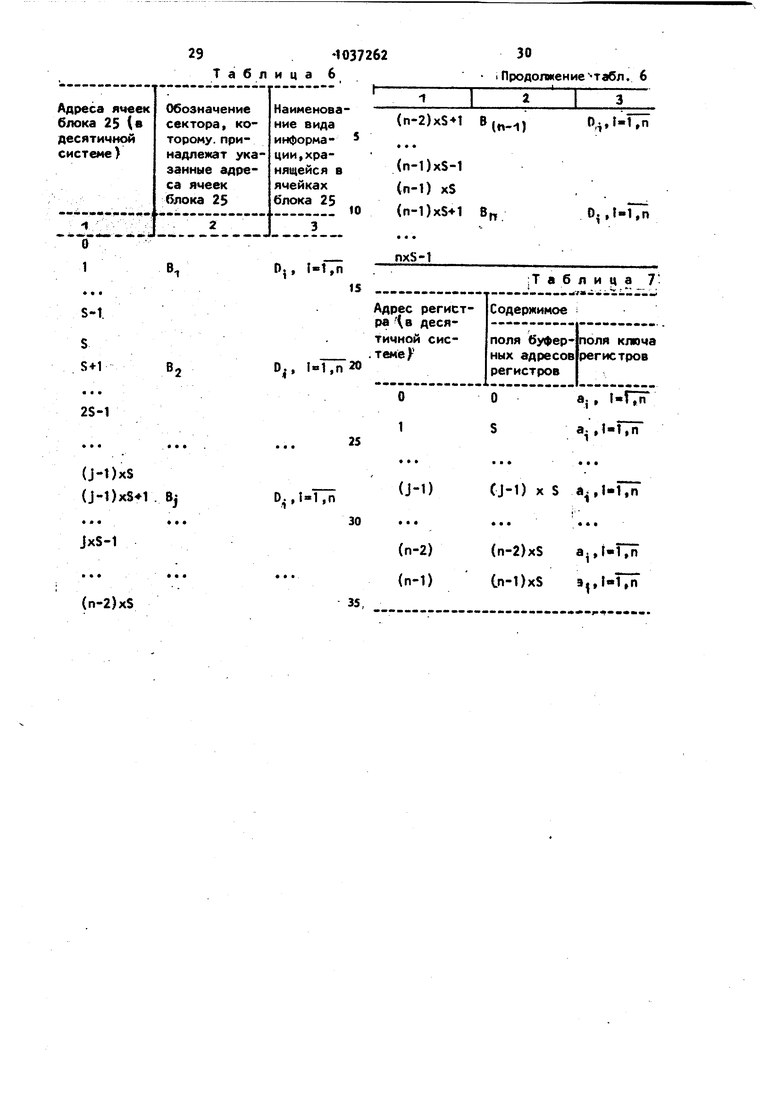

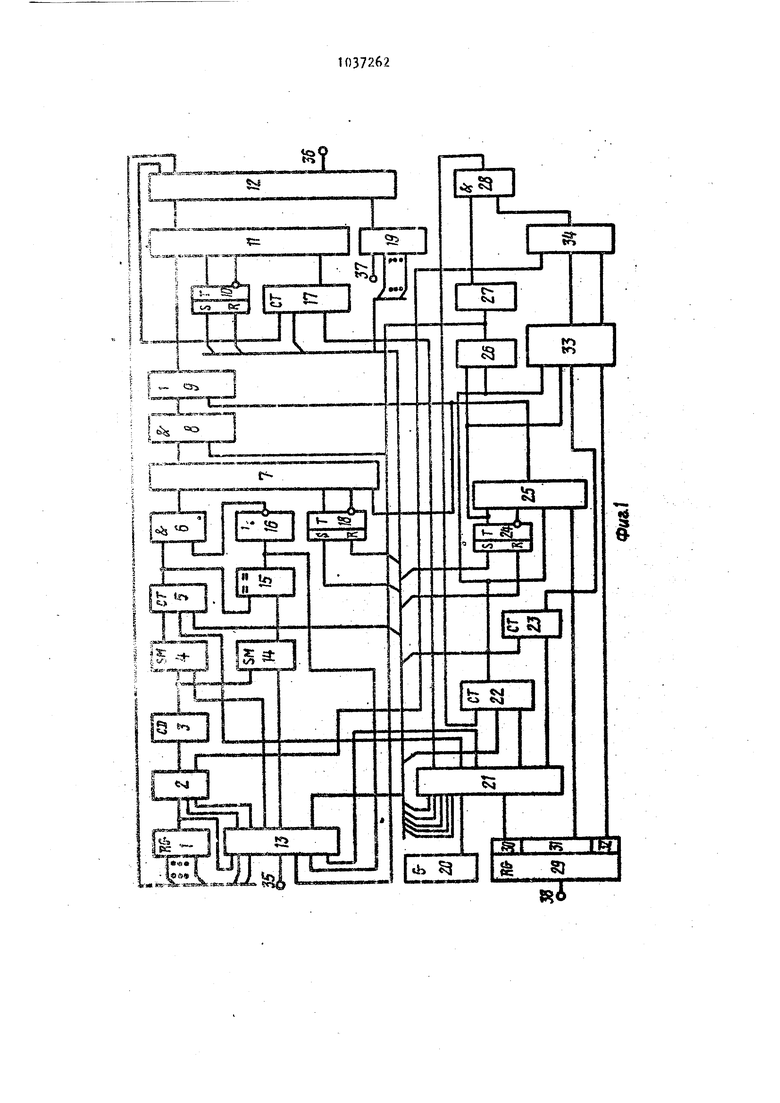

Изобретение относится к вычислительной технике и может найти широкое применение в информационных, управляющих и вычислительных системах, в частности в микропроцессорных управля ющих системах. , Известны микропрограммные процессо ры,, содержащие операционный блок и основное запоминающее устройство tl 2 и 2 } Наиболее близким по технической сущности и достигаемому результату к изобретению является процессор, содержащий основное запоминающее устрой ство, выходное запоминающее устройство, буферное запоминающее устройство, счетчик основных адресов, генератор тактовых импульсов, первую группу элементов И, причем выходы счетчика основных адресов соединены с информационными входами первой труппы элементов И, выходы буферного здпоминающего устройства соединены с информационными входами основного запоминающего устройства, выходы выходного запоминаЮ1цег6 устройства соединены с информационными входами операцион.ного блока, информационные выходы которого соединены с выходами процессора, а управляющие входы соединены с выходами блока управления, первые вхо ды которого соединены с входами опера ционного запуска процессора 13 }. При работе .известного процессора из основного запоминающего устройства в выходное запоминающее устройство производится лишь последовательная перезапись всех слов данных. Поскольку операционному блоку часто необходимы не все, а лишь определенные данные, то для выборки и;з основного запоминающего устройства в выходное запоминающее устройство необходимых данных требуется перезаписать все сло ва данных, адреса которых меньше адре сов необходимых данных. Таким образом, из основного ЗУ в выходное ЗУ выбираются как необходимые, так и ненужные для операционного блока данные что снижает эффективное быстродействие adero процессора. Следовательно, недостатками известного процессора являются низкая производительность и ограниченные функциональные возможности . Целью изобретения является повы- . шение производительности и расширение функциональных возможностей процессора. Цель достигается тем, что микропрограммный процессор, содержащий счетчик основного адреса, первую группу элементов И, блок основной памяти, блок выходной памяти, опера- ционный блок, блок управления, генератор тактовых импульсов и блок буферной памяти, при этом выход счетчика основного адреса соединен с первыми входами элементов И первой группы, выходы которых подкш)чены к адресному входу блока основной памяти, информационный вход блока основной памяти соединен с выходом блока буферной памяти, выход блока выходной памяти подключен к информационному входу операционного блока, управляющий вход которого соединен с выходом блока управления, а первый выход - с выходом результата процессора, причем первый вход бло- ка управления подключен к первому в) операций процессора, содержит регистр информации, коммутатор, лиифратор адреса, сумматоры начального и конечного адреса, блок местного управления, блок сравнения, элемент ИЛИ-НЕ, три триггера режима, вторую и третью группы элементов И, группу элементов ИЛИ, счетчик выходного адреса, счетчик буферного адреса, счетчик адреса регистра, распре делитель импульсов, входной регистр, блок регистров, блок формирования адреса, элемент И и элемент задержки, выход которого соединен с первыми входами элементов-И третьей группы, первый, второй, третий четвертый, пятый и шестой входы блока местного управления подключены соответственно к выходу регистра информации, второму выходу операционного блока, второму входу операций процессора, выходу элемента И, выходу блока сравнения И первому выходу распределителя импульсов, входы регистра информации соединены с вторым выходом операцион ного блока, первый, второй и третий входы коммутатора подключены соответ ственно к выходу регистра информации первому и второму выходам блока местного управления, третий и четвертый выходы которого соединены с первыми входами соответственно сумматора начального адреса и сумматора конечного адреса, пятый выход блока местного управления подключен к первой группе входов распределителя импульсов, установочным входам счетчиков основного адреса, выходного адреса, буферного адреса и адреса регистра, входам сброса и установки триггеров режима, второму входу блока управления и первым входам элементов И второй группы первый и второй выходы коммутатора соединены соответственно с входом шифратора адреса и первым входом блока формирования адреса, выход шифратора адреса подключен к вторым входам сумматоров начального и конечного адреса, выходы которых соединены соответственно с информационным входом счетчика основного адреса и первым входом блока сравнения, второй вход . блока сравнения подключен к выходу счетчика основного адреса, а выход к входу элемента ИЛИ-НЕ, выход которого соединен с вторыми входами элементов И первой группы, первый и второй входы распределителя импульсов подключены соответственно к выходу ге нератора тактовых импульсов и выходу маркеров входного регистра, второй, третий, четвертый и пятый выходы распределителя импульсов соединены с так товыми входами соответственно счетчиков основного адреса, выходного адреса, буферного адреса и адреса регистра, прямые и инверсные выходы пер вого, второго и третьего триггеров р& жима подключены к входам записи и считывания соответственно блока основ ной памяти, блока выходной памяти и блока буферной памяти, вторые входы элементов И второй группы соединены с выходом блока основной памяти, а выходы - с первыми входами элементов ИЛИ группы, вторые входы которых подключены к выходу.блока буферной памяти, выходы элементов ИЛИ группы соединены с информационным входом блока выходной памяти, адресный вход которого подключен к выходу счетчика выходного адреса, выход счетчика адреса регистра соединен с первым адресным входом блока регистров, информационный вход которого подключен к выходу ключа входного регистра, а выходы к второму и третьему входам блока формирования адреса, вторые входы элементов И третьей группы соединены с выходом блока формирования адреса, а выходы этих элементов прдклочены к информационному входу счетчика буферного адреса, выход которого соединен с адресным входом блока буферной памяти, вторым адресным входом блока регистров и первым входом элемента И, выход третьего триггера режима подклочен к управляющему входу блока регистров и второму входу элемента И, выход которого соединен с входом элемента задержки, вход входного регистра подключен к информационному входу процессора, а выход данных к информационному входу блока буферной памяти. Кроме того, блок местного управления содержит триггер ключа, шифратор адреса, регистр адреса, память микрокоманд, регистр микрокоманд, дешифратор, группу элементов И, счетчик, схему сравнения, элемент ИЛИ, элемент И и память признаков, при этом входы установки и сброса триггера ключа соединены с первым входом блока, а прямой и инверсный выходы - с первыми входами соответственно шифратора и элементов И группы, выход шифратора подключен к первому входу регистра адреса, адресный вход памяти микрокоманд соединен с выходом регистра адреса, а выход - с входом регистра микрокоманд, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы которого подключены соответственно к второму входу шифратора адреса, входу дешифратора, третьему, четвертому и пятому выходам блока, первому входу памяти признаков, второму входу регистра адреса и вторым входам элементов И группы, выходы дешифратора соединены с первым и вторым выходами блока, третьи входы элементов И группы подключены к второму входу блока, третий вход блока соединен с первым входом счетчика. первым входом схемы сравнения, третьим входом регистра адреса, первым входом элемента ИЛИ и вторым выходом блока, выходы элементов И группы подключены к третьему входу шифратора адреса и вторым входам элемента ИЛИ и памяти признаков, четвертый и пятый входы шифратора адреса соединены соответственно с первым выходом схемы сравнения и выходом памяти признаков, четвертый вход блока подключен к второму входу счетчика и тре-. тьему входу элемента ИЛИ, пятый вход блока соединен с третьим входом счетчика и четвертым входом элемента ИЛИ, шестой вход блока подключен к четвертому входу счетчика и первому входу элемента И, пятый вход счетчика соединен с прямым выходом триггера ключа, первый и второй выходы счетчика подключены соответственно к второму входу схемы сравнения и третьему входу памяти признаков, выход схемы сравнения соединен с пятым входом элемента ИЛИ, выход которого подключен к второму входу элемента Я, а выход элемента И соединен с управля ющим входом памяти микрокоманд. .На фиг. 1 представлена функциональ ная схема микропрограммного процессора; на фиг. 2 - функциональная схема коммутатора; на фиг. 3 функциона ьная схема операционного блока; на фиг. k - функиональная схема блока местного управления; на фиг. 5 - фун циональная схема блока управления; на фиг. 6 - функциональная схема рас пределителя импульсов; на фиг. 7 функциональная схема блока регистров на Фиг. 8 - функциональная схема бло ка формирования адреса; на фиг. Э алгоритм функционирования процессора В табл. 1 даны возможные значения базы адресе видов информации. В табл. 2 показаны возможные знаг чения умещения лаименьшего наибольше го адреса ячеек памяти первой страни 1(ы ()лока основной па«я.. . В табл. 3 показано возмоадое распределние адресов ячеек памяти блока „- / основной памяти по его страницам (вв ду информации ). В табл. 4 показано возможное распределение во времени адресов ячеек памяти первой страницы блока основно памяти по секторам памяти и рангам первого вида информации. В табл. 5 показано возможное распределение во времени адресов ячеек памяти блока выходной памяти по секторам памяти и рангам хранимого вида информации. В табл. 6 дано возможное распределение во времени адресов ячеек памяти блока буферной памяти по секторам памяти и видам хранимой информации. В табл. 7 noKaai Ho возможное содержимое регистров блока регистров. Микропрограммный процессор (фиг.1) содержит регистр 1 информации, коммутатор ., шифратор 3 адреса, сумматор h начального адреса, счетчик 5 основного адреса, первую группу элементов И 6, блок 7 основной памяти, вгорую группу элементов И 8, группу элементов ИЛИ 9, первый триггер 10 режима, блок 11. выходной памяти, oneрационный блок 12, блок 13 местного управления, сумматор 14 конечного адреса, блок 15 сравнения, элемент ИЛИ-НЕ 16, счетчик 17 выходного адреса, второй триггер 18 режима, блок 19 управления, генератор 20 тактовых импульсов, распределитель 21 импулкг сов, счетчик 22 буферного адреса, счетчик 23 адреса регистра, третий триггер 2k режима, блок 25 буферной памяти, элемент И 26, элемент 27 задержки, третью группу элементов И 28, входной регистр 29 с полем -30 маркера, полем 31 собственно данных и полем 32 ключа, блок 33 регистров, блок 34 формирования адреса, первый .вход 35 операции процессора, выход 36 результата операционного блока 12 и процессора, второй вход 37 операции процессора и информационный вход 38 процессора. Коммутатор У. (фиг. .) состоит из первой группы элементов И. 39 первой группы элементов ИЛИ 40 элемента ИЛИ , второй группы элементов И k2, третьей группы элементов И 3 втог рой группы элементов ИЛИ k, Кроме того, коммутатор содержит первый вход ifS, второй выход 46, группу 47 вторых входов, первый вход 48 из группы 47 входов, второй вход 49 из группы входов 47, третий вход 50 из груп,„ .., пы ч7 входов, третий вход 51. первый « . к н v выход 52. .,. Операционный блок 12 (фиг. 3) содержит группу регистров 53, первую группу элементов И 54, группу сумматоров 55 группу шифраторов 56, вторую группу элементов И 57t первый выход 58 блока 12, информационный вход 59, управляющий вход 60, второй выход (i1.. . ЬлокМЗ местного управления фиг. состоит из триггера 62 ключа, шифратора 63 адреса, регистра 6$ адреса, памяти б5 микрокоманд, регистра 66 микрокоманд с полем б7 шифрации адре сов, полем 68 микроопераций, полем 6 кгвочей вида информации, полем 70 наименьшего смещения, полем 71 наи()ольшего смещения, полем 72 управления блоком памяти, полем 73 адреса управления передачей ключа, дешифратора 75, группы элементов И 76, счетчика 77 схемы 78 сравнения, элемента ИЛИ 79 элемента И 80, памя ти признаков. Блок 13 местного уп равления содержит также первый вход 8 первый выход 83, пятый выход В, вто рой вход 85, второй выход 86, третий выход 87, четвертый выход 88., пятый вход 89, четвертый вход 90, третий вход 91. Блок 19 управления (фиг. 5 ) содержит шифратор 92 адреса, регистр 9 адреса, память 9 микрокоманд, регистр 95 микрокоманд с полем 9б микрокоманд и полем 97 адреса очередной микрокоманды, дешифратор 98 микрокоманд. Блок 19 управления содержит также первый вход 99, выход 100, соглас уадий вход 101, генератор 102 импvльcoв. Распределитель 21 импульсов (фиг. содержит восьмой элемент. И 103, первый триггер , первый элемент ИЛИ 1 первый элемент И 106, первый счетчик 107 импульсов, третий элемент И 108, седьмой элемент И 109, второй элемент И 110, элемент ИЛИ-НЕ 111, второй элемент ИЛИ 112, девятый элемент И 113, второй триггер ll, четвертый элемент ИЛИ 115, третий элемент ИЛИ 116, десятый элемент И 117, третий триггер 1Т8, пятый элемент ИЛИ ПЭ, четвертый элемент И 120, второй счетчик 121 импульсов, пятый элемент И 122, шестой элемент И 123, четвертый триггер . Распределитель 21 импульсов содержит также пер вый вход 125, третий выход 126, чет вертый вход 127, второй выход 128, второй вход 129, первый выход 130, пятый вход 131, седьмой вход 13., Лятый выход 133, шестой вход , че вертый выход 135, нулевой вход 136 и нулевой выход 137 триггера 12 и третий вход 138. 1 2 8 Блок 33 регистров (фиг. 7 состоит. из п элементов И ТЗЭ- -ТЗЭр регист ров с полями l. ключа и полями 42- буферных ад. ,- . ресоя, дешифратора ,(fi +U-ой группы элементов И Т44. Блок 33 регистров содержит также второй выход , первый вход , третий вход I, второй вход , четвертый вход Й9 первый выход 150Блок 3 формирования адреса (фиг.81 состоит из и элементов сравнения, п групп элементов И , группы элементов ИЛИ 153. Блок 3 формирования адреса содержит также третий вход 15,, второй вход 155, выход 156, первый вход 157. Обозначения в таблицах: п- число страниц памяти блока, S число ячеек памяти в каждом секторе, п число секторов в каждой странице. Алгоритм функционирования процессора (фиг. 1б) состоит из операции 1, обозначающей начало алгоритма, операции 2, обозначающей обнуление счетчика 77 блока 13 (F), операции 3, о(означающей обнуление счетчика 77 (F), операции k, обозначающей реализацию процессором такта записи информации из внешних устройств в блок 25 (РЗ операции 5, обозначающей увеличение содержимого счетчика 77 на единицу (F), операции 6, обозначающей проверку условия Меньше ли содержимое счетчика 77 величины m+l .(р ), операции 7, обозначающей реализацию процессором такта перезаписи В блок 7 информации, содержащейся в блоке 25 (Fj), операции 8, обозначающей увеличение содержимого счетчика 77 на единицу (F), операции 9t обозначающей проверку условия Меньше ли содержимое счетчика 77 величины т (р), операции 10, обозначающей обнуление содержимого счетчика 77 (F-,), операции П, обозначающей проверку условия Находится ли триггер б2 блока 13 в единичном состоянии (р), операции 12, обозначающей запись ключа вида информации, содержащегося в регистре 1, в память 81 блока 13 (Fg), операции 13, обозначающей реализацию процессором такта выборки в блок 11 информации из Плока 7 (Fg), операции Н, обозначающей увеличение содержимого счетчика 77 на единицу (, операции 15, обозначающей проверку условия Меньше ли содержимое счетчи910372ка 77 величины m+1 (р)« операции 16, обозначающей реализацию процессором такта обработки блоком 12 данных, содержащихся в блоке 11 (F), операции 17, обозначающей проверку условия Меньше ли содержимое счетчика 77 величины пН-1 (Pj) операции 18, обозначающей уменьшение содержимого счетчика 77 на единицу (Fjj), операции 15, обозначающей умен1г,о шение содержимого счетчика 77 на единицу (Rj, операции 20, обозначающей уменьшение содержимого счетчика 77 на единицу (F),операции 21,обозначающей проверку условия Присвоен ли такту выборки в блок 11 информации из блока 7 и блока 25 приоритет по отношению к такту выборки в блок 11 информации из блока 7 (pg), операции 22, обозначающей реализацию про- 20 цессором такта обработки блоком 12 данных, содержащихся в блоке 11 операции 23 обозначающей проверку условия Меньше ли содержимое счетчика 77 величины т (Р- ) операции 2k, 75 обозначаюи1ей реализацию процессором такта выборки в блок 11 информации из блока 7 и блока 25 (), операции обозначаю1цей реализацию процессором обработки блоком 12 данных, содержа- ,. щихся в блоке 11 (, операции 26, о(5означающей увеличение содержимого счетчика 77 на единицу (Р-,) операции 27 обозначающей проверку успиы J n r UAUAiruii kbi nrtAa ni/ / v/ ловия Превышает ли содержикюе счетчика 77 значение п-1(Р8) .операции 28, 35 обозначающей реализацию такта перезат писи из блока 25 в блок 7 информации оставшейся в блоке 25 () операции 2, обозначающей проверку уело- . вия Заканчивать ли обработку данных процессором (рд операции 30, обозначающей конец алгоритма. Рассмотрим работу микропрограммного процессора. Методически ее описание целесообразно разбить на несколько частей, каждая из которых соответствует определенному циклу функционирования процессора. Основными операциями Процессора являются: запись информации из внешних устройств в блок 25; перезапись в блок 7 информации, содержащейся в блоке 25; выборка в блок 11 информации из елока 7; запись в блок 11 информации из 55 блоков 7 и 25; считывание информации из блока 11 для ее обработки в блоке 12. 210 В цикле записи информации из внешних устройств в блок 25 процессор работает«следующим образом. Сигнал пуска, поступивший на вход 35 процессора и шестой вход блока 13 обеспечивает на пятом выходе блока 13 формирование сигнала, поступающего на первый вход триггера 2k. В результате этого на первый управляющий вход блока 25 с первого выхода триггера 2k поступает сигнал, переводящий атот блок в режим Запись. Кроме того, на пятом выходе блока 13 формируются сигналы, обнуляющие все элементы памяти распределителя 21 и переводящие их в режим Запись данных в блок 25 и сигналы, устанавливающие все разряды счетчиков 22 и 23 в единичное состояние. вход 38 процессора и вход регистра 29 последовательно поступают данные (S слов информации, каждое разрядностью d ) от одного из п внешних устройств, например второго. Это равнесильно тому, что первыми в процессор поступили данные второго вида, Все слова данных второго вида записываются последовательно в регистр 29. Формат всех слов данных состоит из трех полей: поля маркера (нулевой разряд), поля собственно данных (разряды от первого до го ), поля ключа разряды, начиная от (dg-i-l -ro и кончая (d - 1 }-M |. Содержимое поля 30 маркера первого слова вида данных (единица) поступает в распределитель 21, осуществляя его подготовку к работе. После окончания подготовки распределителя 21 к .работе первый поступающий из генераЧора 20 импульс передается через соответствушчие выходы распределителя 21 на х:четные входы счетчиков 22 и 23. В соответствии с этим оба счетчика устанавливаются в нулевое состояние, определяя тем самым адреса первой ячейки блока 25 и первого регистра блока 33 для записи в них соответствующей информации. В ячейку блока 25, определяемую содержимым счетчика 22 (в данном случае - нуль, поступающим на адресный вход блока 25 из поля 31 регистра 29, записывается первое слово данных поступившего вида. В то же время в регистр блока 33, определяемый содержимым счетчика 23, поступаощим на адресный вход блока 33, записывается на хранение иная информация, В отличие от информации блока 25 формат последней ссх:тоит не из одного, а из двух полей: поля ключа и поля буферного адреса (первых слое записываемых видов данных в блок 25) При этом в поле ключа соответству щего регистра блока 33 записывается ключ вида информации, содержащийся в поле 32 регистра 29, а в поле буферного адреса - адрес ячейки блока 25, в которую записывается н,а хра иение первое слово данных поступившего вида ( второго ), содержащийся в счетчике 22. Далее из второго внеш него устройства на вход 38 поступает второе слово данных, записываемое в регистр 29. При этом, в отличие от первого слова в поле маркера второго слова данных содержится не единица, а нуль. Поле ключа второго слова дан ных второго вида при работе процессо ра не используется. Это же справедли во и для всех остальных S-2 слов да ных второго вида. Содержимое поля 31 регистра 29 записывается на временное хранение в ячейку блока 25, адрес которой определяется новым содержимым счетчика 22, которое отличается от старого на единицу младшего разряда. Следовательно, адрес ячейки блока 25 хранящей второе слово данных второго вида, является единичным. При этом содержимое счетчика 23 остается без изменений, а в блок 33 никакая инфор нация не записывается. Запись i-го слова данных второго вида также иден тична записи второго слова SfToro же вида информации. Отличие состоит лиш в адресе ячейки блока 25, хранящей это слово, определяемого величиной содержимого счетчика 22. Это содержи мое равно i-1. После записи S-ro (последнего) слова изменяется состояние распределителя 21, что обуславливает прекращение поступления импульсов на счетный вход счет чика 22, а также прекращение записи в блок 25 слов до прихода следующего после второго вида данных из внешних устройств. В результате этого в блоке 25 оказываются занятыми под хранение информации второго вида S ячеек с адресами от нуля до S-1 принадлежащие только первому сектору блока 25, а в блоке 33 под хранение соответствующего ключа, записанного в первом секторе блока 25, занят один регистр с нулевым адресом. С приходом следующего вида данных из внешних устройств на вход 38 процессора запись информации в блок 25 возобновляется. Пусть данные поступают из 1-го внешнего устройства, т.е. необходимо произвести запись данных i-ro вида. В этом случае после записи первого слова данных i-ro вида в регистр 29 в поле 30 3toro регистра заносится единица. Содержимое счетчиков 22 и 23 изменяется на единицу младшего разряда, т.е. содержимое счетчика 22 становится равным S , а содержимое счетчика 23 - единице. В ячейку блока 25 с адресом S записывается содержимое поля 31 регистра 29, содержащего первое слово данных i-го вида. 8 то же время содержимое счетчика 22 и содержимое поля 32 регистра 29 записываются в регистр блока 33 с адресом, равным единице. Запись остальных 5-1 слов данных i-ro вида идентична записи соответствующих слов данных второго вида. Отличие заключается в том, что указанная запись производится в ячейки второго сектора блока 25 с адресами ячеек от 5+1 до 2S-1. С приходом на регистр 29 очередного вида данных из внешних устройств процессор функционирует аналогично. При этом данные записываются в третьем секторе блока 25 с адресами ячеек от 25 до 3 S-1, а ключ этого вида данных и адрес ячейки блока 25, хранящей первое слово данных этого же8ида, записывается в регистре блока 33 с адресом, равньм двум. Только после того, как последний из т возможных видов данных поступит на регистр 29 и будет записан в п-и сектор блока 25 с адресами ячеек от (п-1 ) Sдо nS-T, а также в регистр блока 33 с адресом, равным п-1, 8 работе процессора производятся изменения. Так например, после формирования адреса ячейки nS-1 счетчиком 22 во всех его разрядах будут записаны единицы. В соответствии с этим и наличием единицы на первом выходе триггера 2 элемент И 2б сформирует на своем выходе единич ный сигнал, который является сигналом окончания записи данных в блок 25 и или сигналом пЬлной заполненности этого блока данными. Этот сигнал передается на элемент 27 и в блок 13. С поступлением указанного сигнала в блок 13 работа процессора в цикле записи информации из внешних устройств заканчивается. В цикле перезаписи в блок 7 информации, содержащейся в блоке 25, процессор работает следующим образом Сигнал об окончании записи данных в блок 25 обуславливает формирование на выходах блока 13 управляющих сигналов, которые обнуляют содержимое счет чика 5 переводят распределитель 21 в режим Перезапись информации из блока 25 в блок 7, устанавливают триггер 18 в единичное состояние, а триггер 2А - в нулевое, настраиваю коммутатор 2 на передачу ключей вида информации из блока 13 на входы шифратора 3 и блока 3. В результате счетчики 5 и 22 гото вы к записи адреса ячейки блоков 7 и 25, из которой считывается и в которую записывается соответственно первое слово первого вида данных, блок 25 переводится в режим Считывание,блок 7 переводится в режим Запись. Кроме того, блок 13 формирует ключ первого вида данных, которые необходимо переписать из некоторого сектора блока 25 в первый сектор первой страницы R блока 7. Этот ключ через коммутатор 2 поступает на шифратор 3 и в блок 3. В последнем случае поступивший ключ одно. временно сравнивается с полем кЛоча .г регистров блока 33. В результа те содержимое поля буферных адресов реги ;тров блока 33, содержимое ключа которого совпало с ключом первого вида данных, передается на выходы блока 3. К этому времени на выходе элемента 27 задержки формируется еди ничный сигнал, что позволяет записать через группуэлементов 28 в сче чик 22 информацию, сформированную на выходах блока Эта информация явл ется адресом ячейки блока 25, в кото рой хранится первое слово данных пер вого вида. Таким образом, в счетчике 22 содержится адрес первого слова данных первого вида, которое будет перезаписано из блока 25 в блок 7 пе вым. Одновременно с этим формируется адрес ячейки блока 7, в которую будет перезаписано первое слово из блока 25. Это осуществляется следующим образом, шифратор 3 на основе кл ча первого вида информации формирует на своем выходе адрес А, соответствующий наименьшему значению адреса среди множества адресов ячеек пер вого сектора первой страницы, причем Р о и на первые входы сумматоров 1 и l подается код А 0. На вторые входы сумматоров k и Ц подаются соответственно коды велич.ин д ид В данном случае л ft, О, а лР « 5-1, Следовательно, на выходе .сумматора k формируется величина , соответствующая наименьшему значению адреса среди множества адресов ячеек первого сектора первой страницы R блока 7. Значение этого адреса записывается в счетчик 5. С выходов этого счетчика адрес ячейки блока 7, в которую будет перезаписано первое слово из блока 25, поступает через группу элементов И 6 на адресные входы блока 7. Формирование разрешающего сигнала на выходе элемента ИЛИ-НЕ 16 происходит до тех пор, пока содержимое счетчика 5 не совпадет с содержимым сумматора Т. ..лА;; 5.1, соответствующим наибольшему адресу среди множества адресов ячеек первого сектора первой страницы блока . Таким образом, формируется адрес ячейки блока 7, в которую будет перезаписано первое слово данных первого вида, который равен нулю. Далее осуществляется Перезапись первого слова первого вида данных из блока 25 в блок 7 после окончания передачи адресов ячеек на адресные входы блоков 7 и 25. Второе слово данных первого вида перезаписывается из блока 25 в ячейку блока 7 с адресом, равным единице. Это обусловлено изменением содержимого счетчика 22 и счетчика 5 на единицу младшего разряда после поступления на их счетные входы импульсов от. распределителя 21. Состояние выходов сумматоров i и шифратора 3f блока 15 и элемента 16 при этом не изменяется. Процесс перезаписи осталь ных S-2 слов первого вида данных из блока 25 в блок 7 аналогичен. Кроме того, блок 13 формирует управляющие сигналы, которые обнуляют содержимое счетчика 5. Одновременно с этим через коммутатор 2 на входы шифратора 3 и блока из блока 13 подается ключ второго вида данных. Далее процесс формирования адресов ячеек блока 25, из которого считывается информация, и адресов ячеек блока 7, в который записывается информация, а также процесс считывания информации из блока 25 и ее записи в блок 7 происходит аналогично. 151 Отличие состоит лишь в том, что различаются значения адресов ячеек соответствующих блоков. С поступлением в блок 13 сигнала об окончании перезаписи данных п-го вида с выхода блока 15 работа процессора в цикле перезаписи в блок 7 информации, содерм ащейся в блоке 25, заканчивается. В цикле выборки в блок 11 информа ции из блока 7 процессор может функционировать лишь после того как предыдущие два цикла его функционирования будут реализованы последовательн друг за другом m раз. В результате этого в блоке 7 во всех m секторах всех п страниц будут содержаться дан ныв, причем в первых секторах будут содержаться данные Гп-го ранга соответствуккчего вида, во вторых сектоpax - данные (m-1)-го ранга соответствующего вида и т.д. В операционном блоке 12 устанавливается вид дан ных, необходиь ый для его работы в текущее время. В соответствии с этим на втором выходе блока 12 формируется ключ вида информации, поступающий на входы регистра 1, а также управляюций сигнал об отсутствии необходимой информации, поступающий на первый вход первой группы блока 13. Указанный управляющий сигнал обуслав ливает формирование в соответствующий момент времени блоком 13 сигналов, которые обнуляют содержимое сме чиков 5 и 17, устанавливают триггер 18 в нулевое состояние, а триггер 10 - в единичное,-переводят распределитель 21 импульсов в режим Вы борка в блок 11 информации из блока 7, настраивают коммутатор 2 на передачу ключа вида информации из регистра 1 на входы шифратора 3 разрешают прохождение информации через группу элементов 8. В результате выполнения указанных операций счетчики 5 и. 17 готовы к формированию необходимых адресов яче ек соответствующих блоков памяти,на соответствующих выходах триггеров 18 и 10 формируются сигналы, переводящие блок 7 в режим Считывание, а блок 11 т в режим Запись, коммутатор 2 передает на входы шифратора 3 ключ вида информации, содержащийся В регистре 1. Пусть для определенности блоку 12 необходим i-й вид данных. Тогда в регистре 1 содержится ключ вида ин2формации а-. Следовательно, на выходах шифратора 3 формируется адрес- А, соответству1ои(ий наименьшему значению адреса среди множества адресов ячеек первого сектора i-и страницы. Сформированная величина АР (i-Um5 передается в сумматоры и 1, Одновременно из блока 13 поступают сигналы смещения наименьшего значения адреса Д ( и наибольшего значения адреса а (т5-1), соответственно в сумматор 4 и сумматор , В дальнейшем процесс формирования адресов ячеект-го сектора i -и страницы R блока 7 аналогичен процессу формирования адресов ячеек первых секторов первой, второй,..., i-й,..., и п-й страницы этого блока, описанному в цикле перезаписи информации из блока 25 в блок 7. Формирование адресов ячеек блока 11 состоит в изменении содержимого счетчика 17 на единицу младшего разряда по мере прихода импульсов на его счетный вход из распределителя 21, Перезапись данных 1-го вида из сектора R- блока 7 производится в первый сектор Q блока 11 с адресами ячеек от нуля до5-1. Наличие единичного сигнала на выходах блока 15 свидетельствует об окончании перезаписи данных первого ранга 1-го вида. После его получения блок 13 формирует новые величины смещений наименьшего и наибольшего адреса. Затем следует процесс формирования адресов ячеек (m-l)го сектора i -и страницыр.,бяока 7, содержащих данные второго ранга i -го вида, описанный ранее. Эта информация записывается во второй сектор 62, блока 11, Адреса ячеек этого сектора по-прежнему формируются в счетчике 17. Это достигается тем, что после окончания перезаписи данных первого ранга i-ro вида в блок 11 распределитель 21 изменяет свое состояние так, что поступление импульсов на счетный вход счетчика 17 прекращается. Поступление этих импульсов возобновляется лишь Г1Осле того, как из блока 13 поступит соответствующий управляющий сигнал, формируемый одновременно со смещениямидА. Следовательно, счетчик 17 будет формировать после этого адреса ячеек (шока 11 от 5 до 2S-1. После перезаписи информации второго ранга i-ro вида в сектор 2 блока 11 осуществляется перезапись данных третьего и т„д. рангов. После перезаписи из блока 7 8 блок 11 данныхm-ro ранга 1 -го вида блок 11 полностью заполнен инормацией. Поэтому после перезаписи в блок 11 S -го слова данныхm-го ранга i-ro вида в ячейку с адресом 5 ШЯ происходит изменение состояния распределителя 21, вс юдстаие чего прекращается поступление импульсов из распределителя 21 на счетный вход счетчика 17. Одновременно прекращает-fо ся и выборка инфо(м«1а14ии из блока 7. Этим заканчивается работа процессора в цикле выборки в блок 11 информации из блока 7.

В цикле записи в блок 11 информации is из блока 7 и блока 25 процессор може функционировать лишь после того, как два первых цикла его работы будут реализованы последовательно друг за

другом m раз и, кроме того, (m+l)-и jo раз реализована запись информации из внешних устройств в блок 25. В результате этого в блоке 7 во всех m секторах всех страниц будут содержаться данные, причем в первых секторах со- 25 держится информация т(-го ранга соответствующего вида, во вторых секторах - информация(т-1)-го ранга и т.д.

функционирование процессора в 1|икле аналогично работе процессора в предыдущем цикле за исключением следующего. Вместо первоначальной перезаписи из сектора R- блока 7 в сектор Q блока 11 перезаписывается информация из соответствующего сектора блока 25, где хранится i-й вид данных, в сектор Q блока 11 и в сектор R. блока 7. Процесс этой перезаписи происходит одновременно. Для этого блок 13 формирует сигналы, которые настраивают ксммутатор 2 на соединение выходов регистра 1 с входами шифратора 3 и входами блока З, обнуляют содержимое счетчика 23 после появления сигнала на выходе эле- мента И 26, устанавливают триггер 2 в нулевое состояние, устанавливают триггер 18 в единичное состояние.

Указанные операции обуславливают перевод блока 7 в режим Запись, 50 блока 25 - в режим Считывание,счетчика 22 - на формирование адресов ячеек блока 25 содержащих информацию 1-го вида, коммутатора 2 - на передачу ключа требуемого вида информации 55 на входы шифратора 3 и блока 3. Вместо первоначальных величин смещений

- |. и ГЛсцс,- - -

ДА,. и 13 формирует велиЧ1-.НЫ смещений-лА р и дАТ1 .После окончания перезаписи информации из блока 25 в блоки 7 .и 11 блок 13 формирует сигналы, устанавливающие триггер 18 в нулевое состояние для перевода блока 7 в режим Считывание. На сумматоры и 1А после этого поступают величины смещений . выборки данных из сектора R блока 7 и записи их в сектор §2 (лока 11. Далее происходит последовательная перезапись информации из сектора ,блока 7 в сектор вэ блока IV, „.., из свктора$;(,„.лока 7 в сектор -блока 11 и тТд. На этом работа процессора в цикле записи в блок 11 из блоков 7 и 2 заканчивается,

В цикле считывания информации из блока 11 для ее обработки в блоке 12 процессор р€1ботает следующим образом. Блок 13 формирует на своем пятом выходе сигналы, которые устанавливают распределитель импульсов 21 в режим Обработка данных в опербционном блоке, устанавливают счетчик 17 в нулевое состояние, устанавливают триггер 10 в нулевое состояние, определяющее режим Считывание блока 11, согласуют работу блока 13 с блоком 19.

В соответствии с полученной информацией от блока 13 блок 19 организует дальнейшую работу процессора в данном цикле. По заданному алгоритму обработки данных блок 19 организует выборку данных из блока 11. В часности указанная выборка возможна двумя способами: последовательным считыванием из блока 11, и считыванием данных в соответствии с адресами, за даваемыми блоком 12.

, В первом и втором случаях выборка данных происходит в соответствии с адресами ячеек памяти, формируемых в счетчике 17. Однако в первом случае указанное формирование адресов происходит благодаря поступлению импульсов из распределителя 21 на счетный вход счетчика 17 а во втором случае - благодаря записи в счетчик 17 через его установочные вхо- ды адресов ячеек памяти, формируемых на вторых выходах блока 12. Важно подчеркнуть, что до тех пор, пока в блоке 12 происходит обработка данных, содержащихся в блоке 11, через первый выход блока 12 информация о необходимом виде данных на регистр 1 и блок 13 не поступает. Передача информации происходит лишь после того как обработка данных, нахоОбозначение секторов, входящих в соответствующие страницы блока 7

0бозначение базы адреса вида информации, содержащейся в соответствующей странице памяти

Значения базы адреса вида информации, соответст8уюи1ей хранящимся в указанных страницах данным

S-1 S

2S 2S+1

(j-1) X S

дящихся 8 блоке .11, закончена и на информационный выход блока 12 выданы результаты этой обработки.

Таблица 1

«ij

nj

J«TT;

j.1,m

А

(f-DitiS- ... (m-l)mSb{n-i;

Ь,- . (-i/

Таблица 2

3S-1

2S

1037262

21

(j-1) X

(j X S -1)

(m-2) X S (m-2) X S +1

...

((fn-1) X S -1) (m-l) X S

(m-1) X S + l

(m X S -1) - b

Т a 6 л и ц a 3

Первый

Первая

Вторая

Второй

. 22 ПродЬлжение табл. 12

(j X S -1) (J-1) X S

((m-1) X S-1) (m-2) x S

(m-1) X S

ffl X S-l

Продолжение табл. 3

.1

h Vir

1-й

1-я

Vn

n-й

n-я

f4

7

.tf I

сч E

rf

N

r

I

u t/

ГЭ . СЛ

I

I

.

s

I

in

E

fS

- I

CNj

+ E

i

M

E

f

I л

V)

ff

еч t/ vt

)/

X

с М Е Е

4П

X)

и

+

(/ «л

i

I

«л X

i

Е

27

S-1

S

t

2S-1

2S 2S+1

3S-1

(J-j) X S (J-1) X

(jxS-1)

(m-2) X S (m-2) X S-H

(m-1) X S-t (m-1) X S (m-1) X

(m X S -1)

28

1037262 Таблица 5

m-1

m-2

m-Jfl

(mvi)

1037262

29

Таблица 6 D|, 1 1,n 20 (J-t)xS D,.,.TTK (j-1) (n-2)xS

30 I Продолжениетабл. 6

(n-2)xS .)0,i.-t,n

(n-l)xS-l Cn-1) xS (n-1) Brt

0.,l-l,n

;Таблица 7 (J-1) X Sa,l-1,n « « (n-2)xSa., tn-l)xSapI T n

4e(:S--- ic-a

RA

39

w

Я

43

я

S9

53

itO

42

4«

«:

57

«;

62

63

6

-щ

f t

15

6&

SL

,1

35

.i

JL

3

J7|

Cm

;;

J7

tf

xvt

$5

Фаг.б H34ajJO А ing 3| РЭ ой т fml 01д 5 РЛ f7 «ГР п W %п 8| g I |гу| Fn I/ gj 50|Хо//аГ1 фуг.5

Авторы

Даты

1983-08-23—Публикация

1981-04-28—Подача