1

Изобретение относится к области вычислительной техники.

Известны устройства для моделирования случайного выбора элементов множества, содержащие блок управления, входы которого подключены ко входам пуска и опроса устройства, первый выход соединен с первым входом счетчика, второй, третий и четвертый выходы соединены с управляющими входами первого, второго и третьего блоков передачи кода соответственно, а пятый выход соединен с управляющим входом сумматора и вторым входом счетчика, выходы которого через первый блок передачи кода соединены с информационными входами сумматора, выходы которого через дешифратор соединены с информационными входами второго и третьего блоков передачи кода, а выходы третьего блока передачи кода соединены с выходами устройства.

Все известные устройства не обеспечивают случайного выбора элементов множества без повторений.

iB предложенном устройстве указанный недостаток исключен.

Устройство отличается от известных тем, что оно содержит блок памяти, управляющий вход которого подключен к пятому выходу блока управления, а информационные входы подключены к соответствующим выходам третьего блока передачи кода, и блок сигналов приращения, входы которого подключены к соответствующим выходам блока памяти и второго блока передачи кода, а выход соединен с третьим входом счетчика.

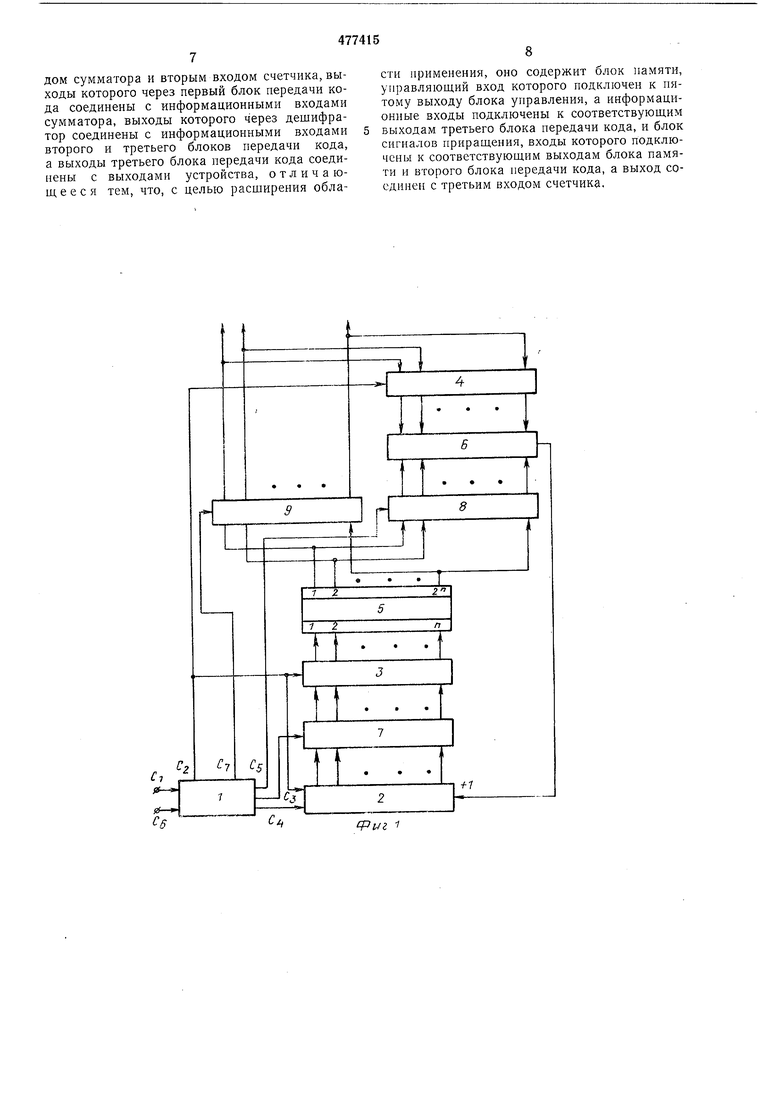

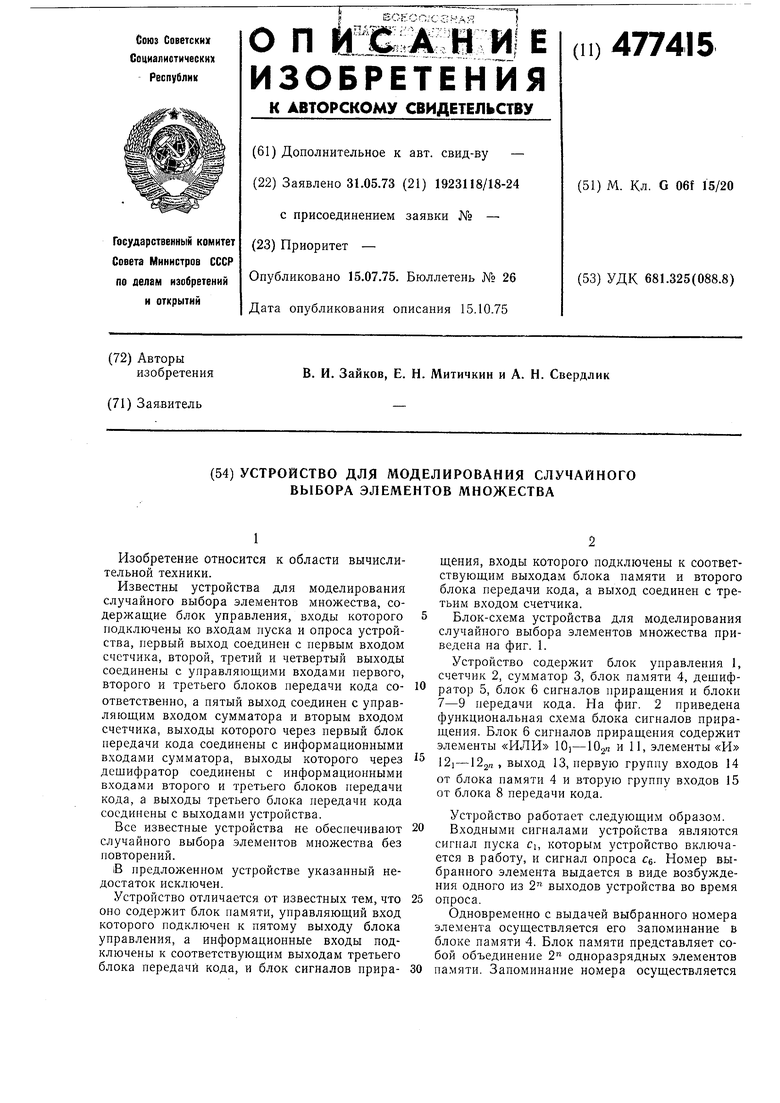

Блок-схема устройства для моделирования случайного выбора элементов множества приведена на фиг. 1.

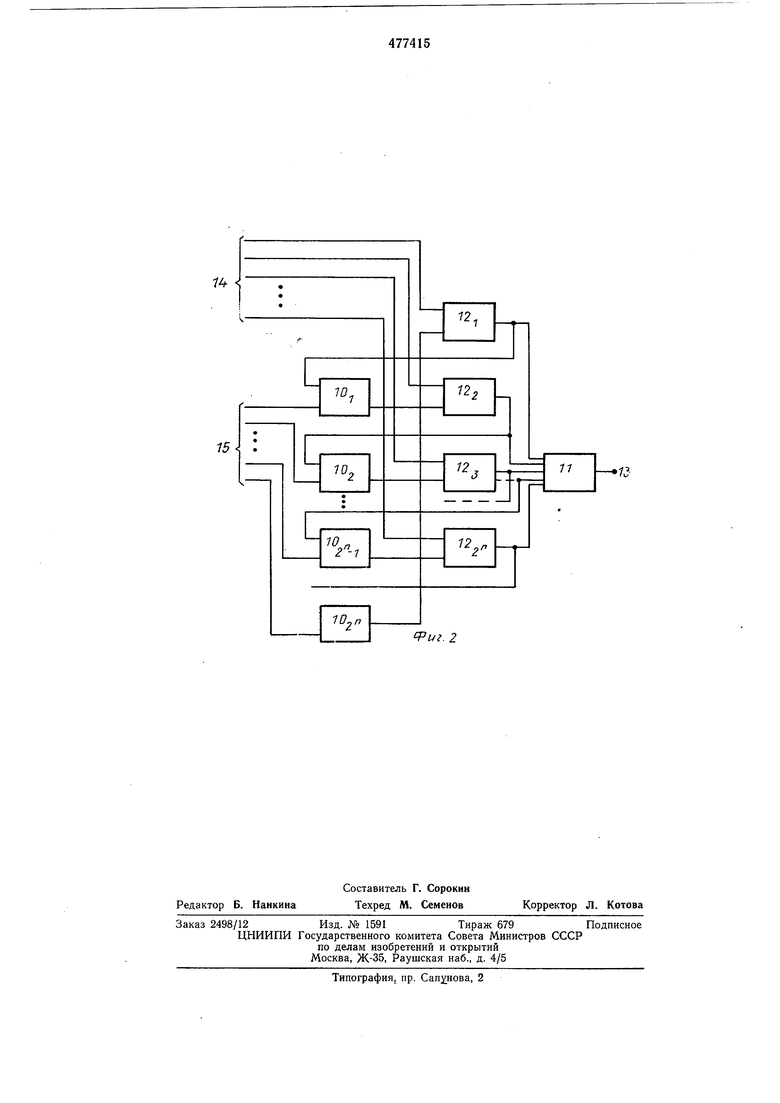

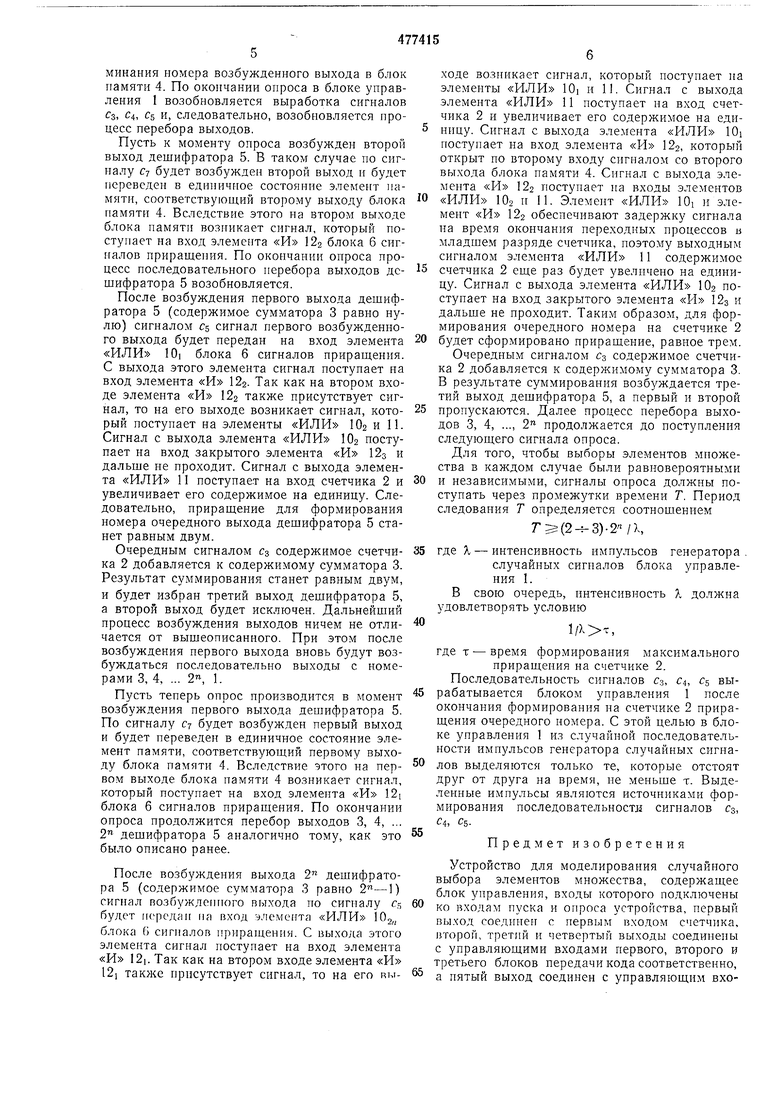

Устройство содержит блок управления 1, счетчик 2, сумматор 3, блок памяти 4, дешифратор 5, блок 6 сигналов приращения и блоки 7-9 передачи кода. На фиг. 2 приведена функциональная схема блока сигналов приращения. Блок 6 сигналов приращения содержит элементы «ИЛИ lOj-IQ n и 11, элементы «И ,г , выход 13, первую группу входов 14 от блока памяти 4 и вторую группу входов 15 от блока 8 передачи кода.

Устройство работает следующим образом.

Входными сигналами устройства являются сигнал пуска Сь которым устройство включается в работу, и сигнал опроса с. Номер выбранного элемента выдается в виде возбуждения одного из 2 выходов устройства во время опроса.

Одновременно с выдачей выбранного номера элемента осуществляется его запоминание в блоке памяти 4. Блок памяти представляет собой объединение 2 одноразрядных элементов памяти. Запоминание номера осуществляется переходом в единичное состояние соответствующего возбужденной шине элемента памяти блока памяти 4. Для этой цели входы блока памяти соединены с выходами устройства. Формирование номера элемента множества происходит на сумматоре 3 путем суммирования по модулю 2 номера предыдущего элемента множества с приращением очередного номера, формируемого на счетчике 2. Для передачи содержимого счетчика 2 в сумматор 3 выходы счетчика 2 через блок 7 передачи кода подключены ко входам сумматора 3. Дешифрирование номера элемента осуществляется дешифратором 5, для чего его входы подключены к выходам сумматора 3. Выходы дешифратора 5 подключены через блок 9 передачи кода к выходам устройства и через блок 8 передачи кода - ко входам блока 6 сигналов приращения. Другая группа входных щин блока сигналов приращения подключена к выходам блока памяти 4. Блок 6 сигналов приращения под воздействием входных сигналов вырабатывает последовательность импульсов, число которых рав но числу ранее выбранных номеров, непосредственно следующих за номером возбужденного выхода дешифратора 5. Например, если возбужден выход с номером i и среди старших номеров ближайший невыбранный номер , то блок 6 сигналов приращения вырабатывает последовательность, состоящую из (k-1) импульсов. Эта последовательность поступает на вход счетчика 2 и подсчитывается. Согласованная работа блока устройства обеспечивается сигналами Cz, Cz, с, Cs и CT, вырабатываемыми блоком управления 1. Сигнал С2 переводит в нулевое состояние счетчик 2, сумматор 3 и блок памяти 4. Сигнал сз осуществляет передачу содержимого счетчика 2 через блок 7 передачи кода на вход сумматора 3. Сигнал С4 поступает на счетчик 2 и переводит все,его разряды, кроме младшего, в нулевое состояние, а младший разряд устанавливает в единичное состояние. Сигнал Cs осушествляет передачу сигнала возбужденного выхода дешифратора 5 через блок 8 передачи кода на вход блока 6 сигналов приращения. Сигнал С7 обеспечивает передачу сигнала возбужденного выхода дешифратора 5 через блок 9 передачи кода на выход устройства. На вход устройства поступает сигнал пуска Сь которым включается в работу блок управления 1. Блок управления вырабатывает сигнал С2, которым переводятся в нулевое состояние счетчик 2, сумматор 3 и блок памяти 4. Возбулсдается первый выход дешифратора 5, соответствующий нулевому содержимому сумматора 3. Так как все элементы памяти 4 находятся в нулевом состоянии, то сигналы на всех его выходах отсутствуют, вследствие чего все элементы «И 12i-122П блока 6 сигналов приращения закрыты. После приведения устройства в исходное состояние блоком управления 1 вырабатывается сигнал Сз. Источником сигнала Сз является генератор случайных сигналов (на чертеже не показан), который входит в состав блока управления 1. Сигналом Сз содержимое счетчика 2 прибавляется к содержимому сумматора 3. Так как их содержимое равно нулю, то состояние сумматора 3 не изменяется, и не изменяется номер возбужденного выхода дешифратора 5. Пересылка содержимого счетчика 2 на вход сумматора 3 осуществляется через блок 7 передачи кода. После сигнала Сз вырабатывается сигнал С4, которым на счетчике 2 устанавливается единичное приращение. После сигнала С4 вырабатывается сигнал Cs, которым сигнал с первого возбужденного выхода дешифратора 5 через блок 8 передачи кода передается на вход элемента «ИЛИ lOi блока 6 сигналов приращения. Сигнал с выхода элемента «ИЛИ lOi поступает на закрытый элемент «И 122 и дальше не проходит. В результате, на выходе блока 6 сигналов приращения импульсы отсутствуют и, следовательно, содержимое счетчика 2 не меняется. Таким образом, после выработки первой последовательности сигналов Сз, С4 и с содержимое сумматора 3 будет равно нулю, на выходе дещифратора 5 будет возбужден первый выход, содержимое счетчика 2 будет равно единице. После выработки блоком управления 1 второй последовательности этих сигналов содержимое сумматора 3 станет равным единице, будет возбужден второй выход дещифратора 5, а содержимое счетчика 2 останется равным единице. После выдачи третьей последовательности сигналов Сз, С4 и Cs содержимое сумматора 3 станет равным двум, будет возбужден третий выход дешифратора 5, а содержимое счетчика 2 по-прежнему останется рав пым единице и т. д. Итак, сигналами Сз, С4, Сэ, вырабатываемыми блоком управления 1, осуществляется последовательный перебор выходов дешифрато-. ра 5. На сумматоре 3 выполняется суммирование по модулю 2, поэтому после выбора выхода с номером 2 следующим будет выбран первый выход, после чего процесс перебора выходов повторится. В таком режиме устройство работает до поступления в него сигнала опроса Cg. После прихода сигнала опроса блок управления 1 прекращает вырабатывать сигналы Сз, С4 и Сд и по истечении времени окончания переходных процессов в дешифраторе 5, вызванных формированием текущего номера элемента, вырабатывает сигнал с. Этот сигнал поступает в блок 9 передачи кода и осуществляет выдачу сигнала возбужденного выхода дешифратора 5 на выход устройства в виде возбуждения одного из 2 выходов. За счет связи входов блока памяти 4 с выходами устройства осуществляется одновременно с выдачей запоминания номера возбужденного выхода в блок намяти 4. По окончании опроса в блоке управления 1 возобновляется выработка сигналов Сз, С4, С5 и, следовательно, возобновляется процесс перебора выходов.

Пусть к моменту опроса возбужден второй выход дешифратора 5. В таком случае по сигналу Су будет возбужден второй выход и будет 1ереведен в единичное состояние элемент паохмятн, соответствующий второму выходу блока памяти 4. Вследствие этого на втором выходе блока памяти возникает сигнал, который поступает на вход элемента «И 122 блока 6 сигналов приращения. По окончании опроса процесс последовательного перебора выходов дощифратора 5 возобновляется.

После возбуждения первого выхода дешифратора 5 (содержимое сумматора 3 равно нулю) сигналом Сб сигнал первого возбужденного выхода будет передай на вход элемента «ИЛИ lOi блока 6 сигналов приращения. С выхода этого элемента сигнал поступает на вход элемента «И 122. Так как на втором входе элемента «И 122 также присутствует сигнал, то на его выходе возникает сигнал, который поступает на элементы «ИЛИ Юг и П. Сигнал с выхода элемента «ИЛИ Юг поступает на вход закрытого элемента «И 12з и дальше не проходит. Сигнал с выхода элемента «ИЛИ 11 поступает на вход счетчика 2 и увеличивает его содержимое на единицу. Следовательно, приращение для формирования номера очередного выхода дешифратора 5 станет равным двум.

Очередным сигналом Сз содержимое счетчика 2 добавляется к содержимому сумматора 3. Результат суммирования станет равным двум, и будет избран третий выход дешифратора 5, а второй выход будет исключен. Дальнейший процесс возбуждения выходов ничем не отличается от вышеописанного. При этом после возбуждения первого выхода вновь будут возбуждаться последовательно выходы с номерами 3, 4, ... 2, 1.

Пусть теперь опрос производится в момент возбуждения первого выхода дешифратора 5. По сигналу С7 будет возбужден первый выход и будет переведен в единичное состояние элемент памяти, соответствующий первому выходу блока памяти 4. Вследствие этого на первом выходе блока памяти 4 возникает сигнал, который поступает на вход элемента «И 12i блока б сигналов приращения. По окончании онроса продолжится перебор выходов 3, 4, ... 2 дешифратора 5 аналогично тому, как это было описано ранее.

После возбуждения выхода 2 дешифратора 5 (содержимое сумматора 3 равно ) сигнал позбуждеппого выхода по сигналу Cs будет гк-редаи па вход элемента «ИЛИ 102,, блока 6 сигналов прирагцення. С выхода этого элемента сигнал поступает на вход элемента «И 12. Так как на втором входе элемента «И 12) также присутствует сигнал, то на его RWходе возникает сигнал, который поступает на элементы «ИЛИ 10 и 11. Сигнал с выхода элемента «ИЛИ И поступает на вход счетчика 2 и увеличивает его содержимое на единицу. Сигнал с вы.хода элемента «ИЛРГ lOj поступает на вход элемента «И 122, который открыт по второму входу снгналом со второго выхода блока памяти 4. Сигнал с выхода элемента «И 122 поступает на входы элементов «ИЛИ Юг н П. Элемент «ИЛИ lOj и элемент «И 122 обеспечивают задержку сигнала на время окончания переходных процессов и младшем разряде счетчика, поэтому выходным сигиалом элемента «ИЛИ 11 содержимое счетчика 2 еще раз будет увеличено на единицу. Сигнал с выхода элемента «ИЛИ Юг постуиает на вход закрытого элемента «И 12з и дальше не нроходит. Таким образом, для формирования очередного номера на счетчике 2 будет сформировано приращение, равное трем.

Очередным сигналом Сз содержимое счетчика 2 добавляется к содерн-симому сумматора 3. В результате суммирования возбуждается третий выход дешифратора 5, а первый и второй пропускаются. Далее процесс перебора выходов 3, 4, ..., 2 продолжается до поступления следующего сигнала опроса.

Для того, чтобы выборы элементов множества в каждом случае были равновероятными и независимыми, сигналы опроса должны поступать через промежутки времени Т. Период следования Т определяется соотношением

Г2г()-2/Х,

где К-интенсивность импульсов генератора случайных сигналов блока управления 1. В свою очередь, интенсивность .

удовлетворять условию

1А,

где т - время формирования максимального

приращения на счетчике 2. Последовательность сигналов Сз, С4, Cs вырабатывается блоком управления 1 после окончания формирования на счетчике 2 приращения очередного номера. С этой целью в блоке управлення 1 из случайной последовательности импульсов генератора случайных сигналов выделяются только те, которые отстоят друг от друга на время, не меньше т. Выделенные импульсы являются источииками формирования последовательност.н сигналов Сз,

С4, С5.

Предмет изобретения

Устройство для моделирования случайного выбора элементов множества, содержащее блок управления, входы которого подключены ко входам пуска и опроса устройства, первый БЫ.ход соелпнен с первым входом счетчика, второй, третпй и четвертый выходы соединены с управляющими входами первого, второго и третьего блоков передачи кода соответственно, а пятый выход соединен с управляющим входом сумматора и вторым входом счетчика, выходы которого через первый блок передачи кода соединены с информационными входами сумматора, выходы которого через дешифратор соединены с информационными входами второго и третьего блоков передачи кода, а выходы третьего блока передачи кода соединены с выходами устройства, отличающееся тем, что, с целью расширения обла8

сти применения, оно содержит блок памяти, управля1ош,ий вход которого подключен к пятому выходу блока управления, а информационные входы подключены к соответствующим выходам третьего блока передачи кода, и блок сигналов приращения, входы которого подключены к соответствующим выходам блока памяти и второго блока передачи кода, а выход соединен с третьим входом счетчика,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования случайного выбора элементов множества | 1977 |

|

SU703824A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Устройство для ввода информации | 1988 |

|

SU1513438A1 |

| Устройство для уплотнения многоканальных сообщений с кодоимпульсной модуляцией | 1986 |

|

SU1365106A1 |

| Устройство для поиска информации в памяти | 1986 |

|

SU1392579A1 |

| Система коммутации | 1985 |

|

SU1317449A1 |

| Адаптивный классификатор | 1984 |

|

SU1220004A1 |

Cs

Сз

C

8

Г

+ 1

иг 1

15

иг. 2

Авторы

Даты

1975-07-15—Публикация

1973-05-31—Подача