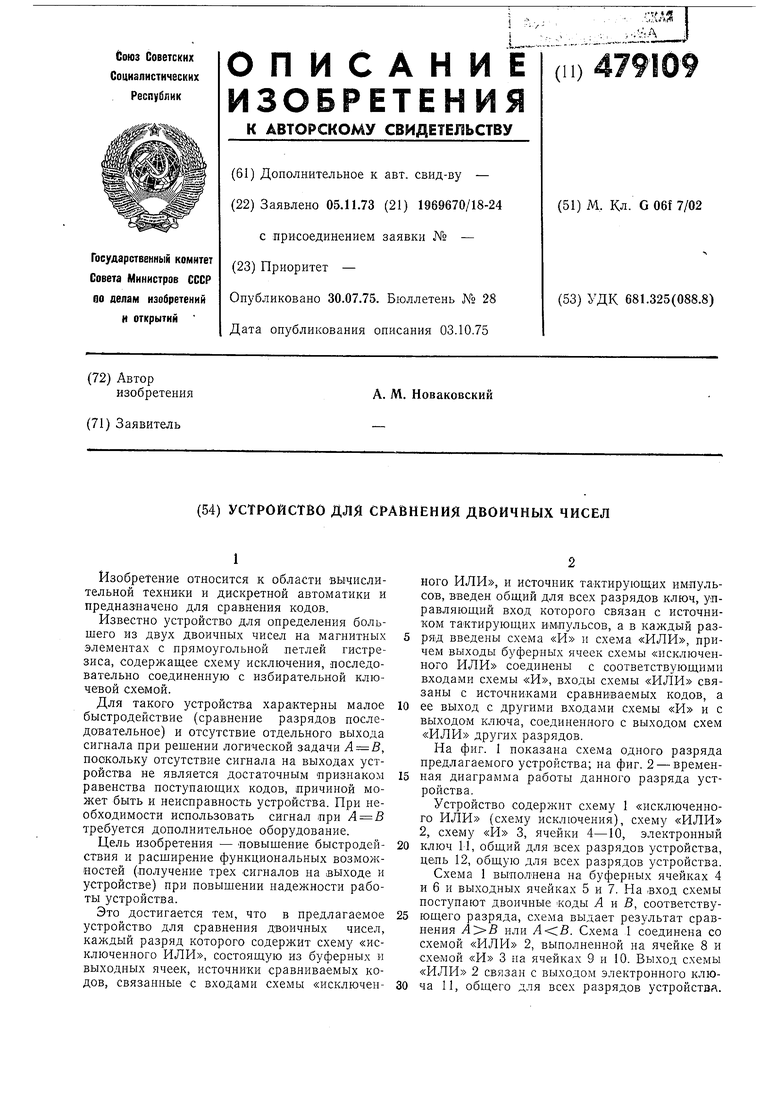

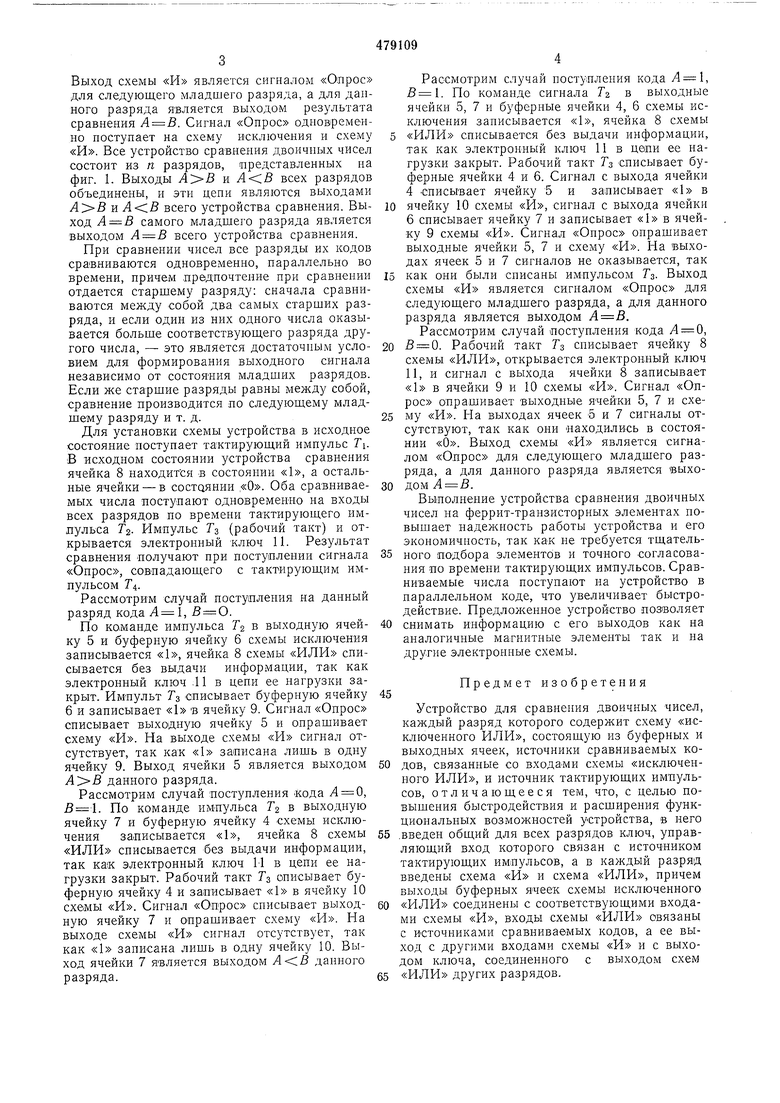

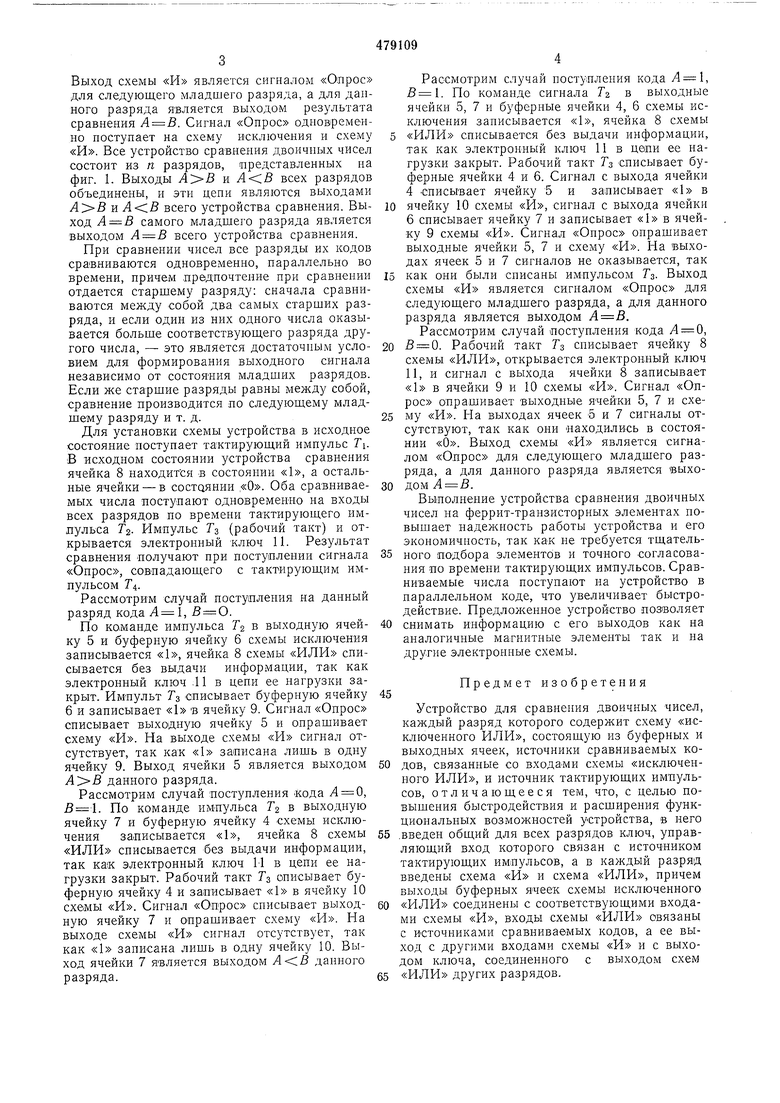

Выход схемы «И является сигналом «Опрос для следующего младшего разряда, а для данного разряда является выходом результата сравнения . Сигнал «Опрос одновременно поступает на схему исключения и схему «И. Все устройство сравнения двоичных чисел состоит из п разрядов, представленных на фиг. 1. Выходы и А-.В всех разрядов объединены, и эти цепи являются выходами и всего устройства сравнения. Выход А В самого младшего разряда является выходом всего устройства сравнения. При сравнении чисел все разряды их кодов сравниваются одновременно, параллельно во времени, причем предпочтение при сравнении отдается старшему разряду: сначала сравниваются между собой два самых старших разряда, и если один из них одного числа оказывается больше соответствуюшего разряда другого числа, - это является достаточным условием для формирования выходного сигнала независимо от состояния младших разрядов. Если же старшие разряды равны между собой, сравнение производится по следуюш,ему младшему разряду и т. д. Для установки схемы устройства в исходное состояние поступает тактируюш,ий импульс Гь В исходном состоянии устройства сравнения ячейка 8 находится в состоянии «1, а остальные ячейки - в состаянии «О. Оба сравниваемых числа поступают одновременно на входы всех разрядов по времени тактируюш,его имлульса 2. Импульс Гз (рабочий такт) и открывается электронный ключ И. Результат сравнения получают при поступлении сигнала «Опрос, сов1падаюш,его с тактируюш,им импульсом Г4. Рассмотрим случай поступления на данный разряд кода , В О. По команде импульса TZ в выходную ячейку 5 и буферную ячейку 6 схемы исключения записывается «1, ячейка 8 схемы «ИЛИ списывается без выдачи информации, так как электронный ключ Л 1 в цепи ее нагрузки закрыт. Импульт Гз списывает буферную ячейку б и записывает «1 в ячейку 9. Сигнал «Оцрос списывает выходную ячейку 5 и опрашивает схему «И. На выходе схемы «И сигнал отсутствует, так как «1 записана лишь в одну ячейку 9. Выход ячейки 5 является выходом данного разряда. Рассмотрим случай поступления «ода А 0, . По команде импульса TZ в выходную ячейку 7 и буферную ячейку 4 схемы исключения записывается «Ь, ячейка 8 схемы «ИЛИ списывается без выдачи информации, так как электронный ключ М в цепи ее нагрузки закрыт. Рабочий такт Гз списывает буферную ячейку 4 и занисывает «1 в ячейку 10 схемы «И. Сигнал «Опрос списывает выходную ячейку 7 и опрашивает схему «И. На выходе схемы «И сигнал отсутствует, так как «1 записана лишь в одну ячейку 10. Выход ячейки 7 является выходом данного разряда. Рассмотрим случай поступления кода , . По команде сигнала TZ в выходные ячейки 5, 7 и буферные ячейки 4, 6 схемы исключения записывается «1, ячейка 8 схемы «ИЛИ списывается без выдачи информации, так как электронный ключ 11 в цапи ее нагрузки закрыт. Рабочий такт Гз списывает буферные ячейки 4 и 6. Сигнал с выхода ячейки 4Списывает ячейку 5 н записывает «1 в ячейку 10 схемы «И, сигнал с выхода ячейки 6 списывает ячейку 7 и записывает «1 в ячейку 9 схемы «И. Сигнал «Опрос опрашивает выходные ячейки 5, 7 и схему «И. На выходах ячеек 5 и 7 сигиалов не оказывается, так как они были списаны импульсом Гз. Выход схемы «И является сигпалом «Опрос для следующего младшего разряда, а для данного разряда является выходом . Рассмотрим случай поступления кода Л 0, 5 0. Рабочий такт Гз списывает ячейку 8 схемы «ИЛИ, открывается электронный ключ 11, и сигнал с выхода ячейки 8 записывает «1 в ячейки 9 и 10 схемы «И. Сигнал «Опрос опрашивает выходные ячейки 5, 7 и схему «И. На выходах ячеек б и 7 сигналы отсутствуют, так как они находились в состоянии «О. Выход схемы «И является сигналом «Опрос для следующего младшего разряда, а для данного разряда является выходом А В. Выполнение устройства сравнения двоичных чисел на феррит-транзисторных элементах повышает надежность работы устройства и его экономичность, так как не требуется тщательного подбора элементов и точного согласования по времени тактирующих нмпульсов. Сравниваемые числа поступают на устройство в параллельном коде, что увеличивает быстродействие. Предложенное устройство позволяет снимать информацию с его выходов как на аналогичные магнитные элементы так и на другие электронные схемы. Предмет изобретения Устройство для сравнения двоичных чисел, каждый разряд которого содержит схему «исключенного ИЛИ, состоящую из буферных и выходных ячеек, источники сравниваемых кодов, связанные со входами схемы «исключенного ИЛИ, и источник тактирующих импульсов, отличающееся тем, что, с целью ноышения быстродействия и расширения функиональных возможностей устройства, в него веден обший для всех разрядов ключ, управяющий вход которого связан с источником актирующих импульсов, а в каждый разряд ведены схема «И и схема «ИЛИ, причем ыходы буферных ячеек схемы исключенного ИЛИ соединены с соответствующими входаи схемы «И, входы схемы «ИЛИ связаны источниками сравниваемых кодов, а ее выод с другими входами схемы «И и с выхоом ключа, соединенного с выходом схем ИЛИ других разрядов.

УЗ

Опрос

А-гВ А В

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1974 |

|

SU572922A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1319305A1 |

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| Устройство для управления приемом и упорядочением данных | 1981 |

|

SU1019448A2 |

| Устройство ранжирования экстремальных значений | 1984 |

|

SU1168924A2 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙУГОЛ — КОД | 1970 |

|

SU277416A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ в АССОЦИАТИВНОЙ НАМЯТИ | 1968 |

|

SU209538A1 |

| Устройство для считывания графической информации | 1976 |

|

SU640334A1 |

| Линейный аппроксиматор | 1983 |

|

SU1157548A1 |

Авторы

Даты

1975-07-30—Публикация

1973-11-05—Подача