Изобретение относится к радиотехнике и может использоваться в асинхронных адресных системах связи.

Цель изобретения - повышение скорости передачи.

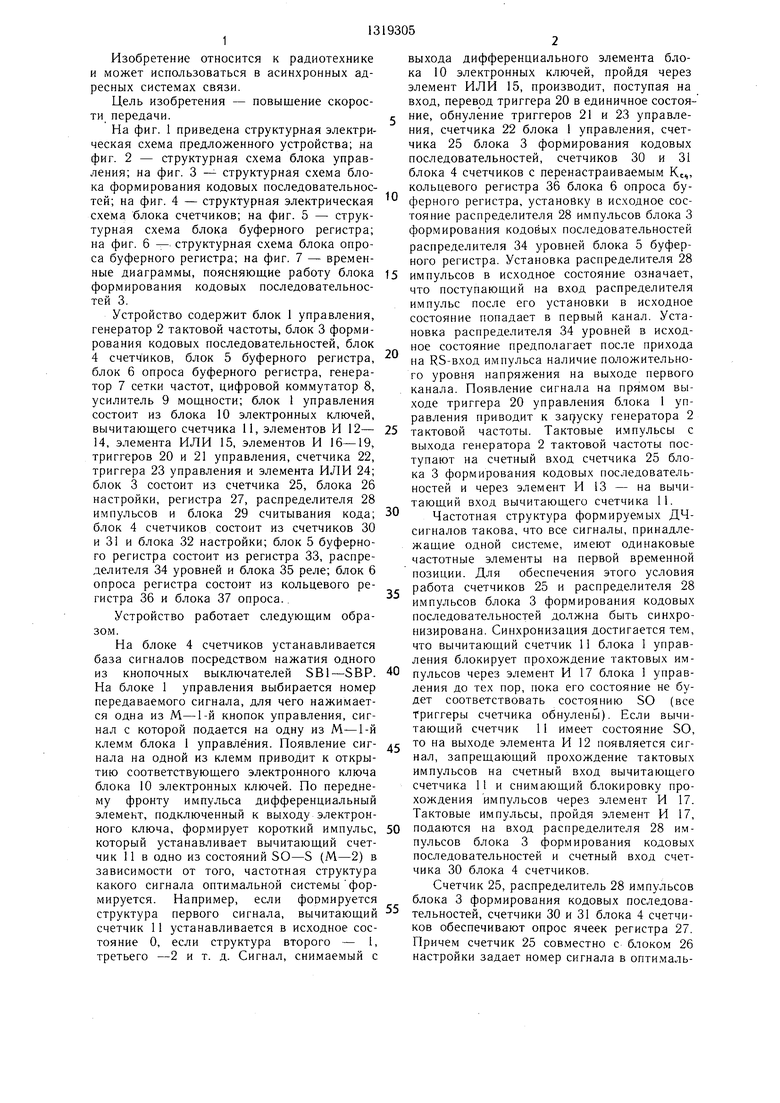

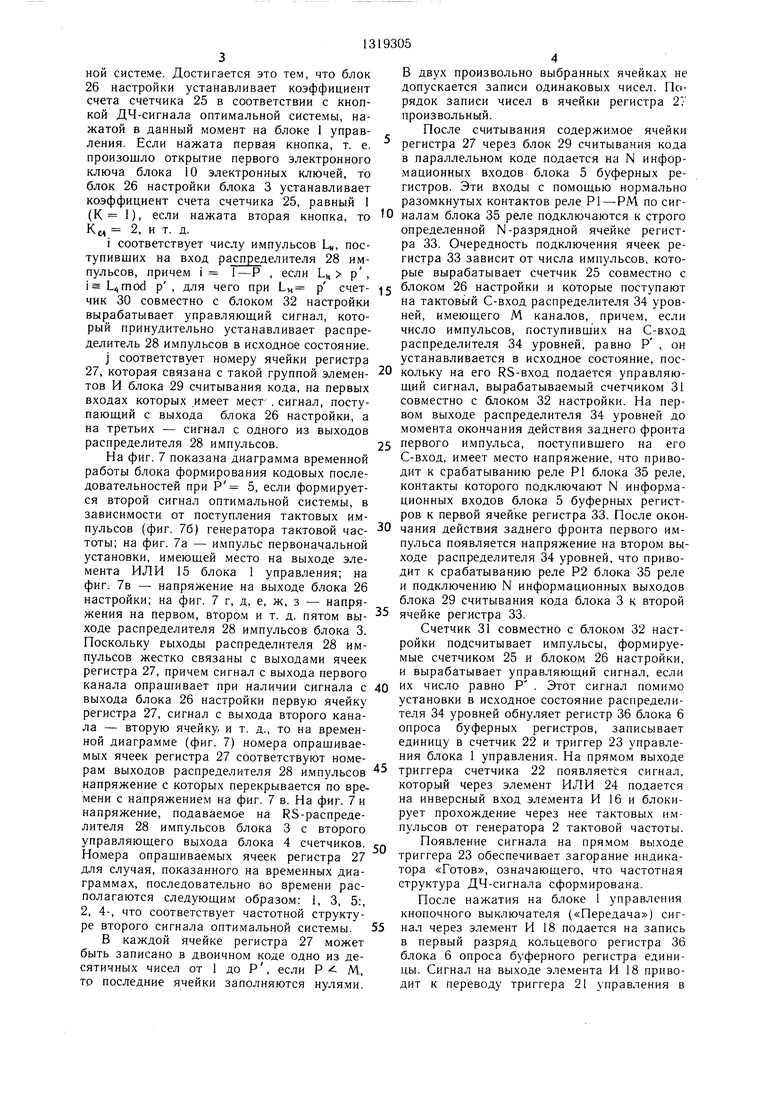

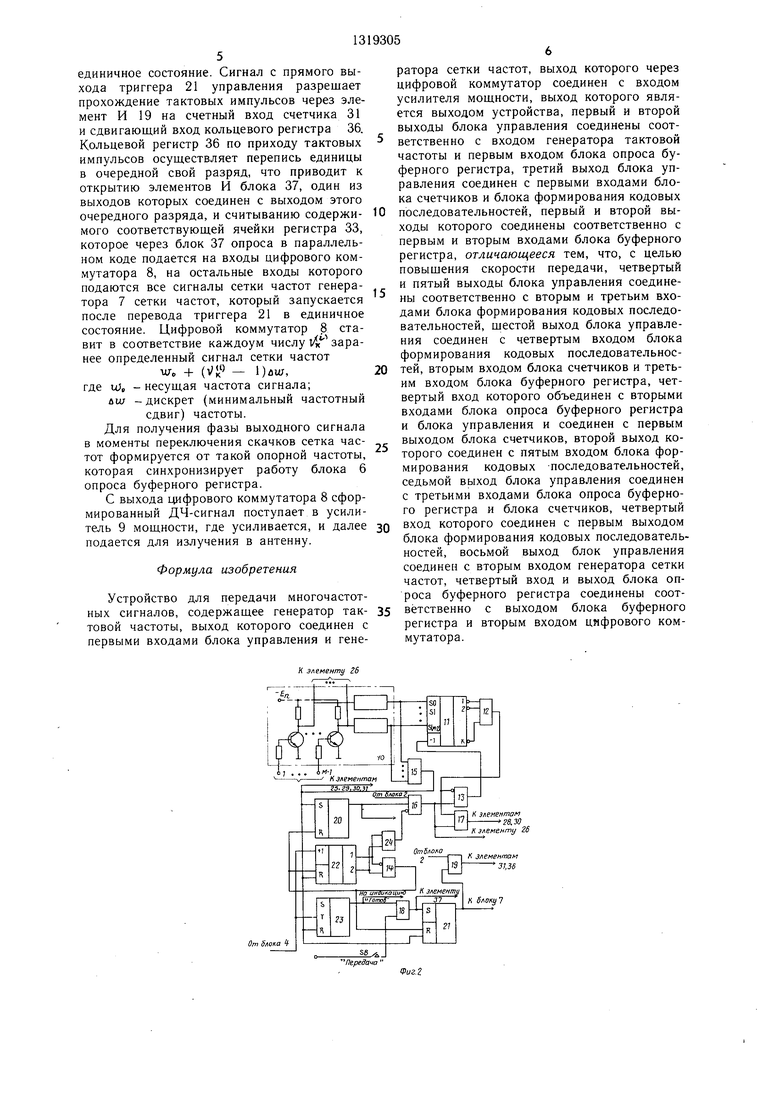

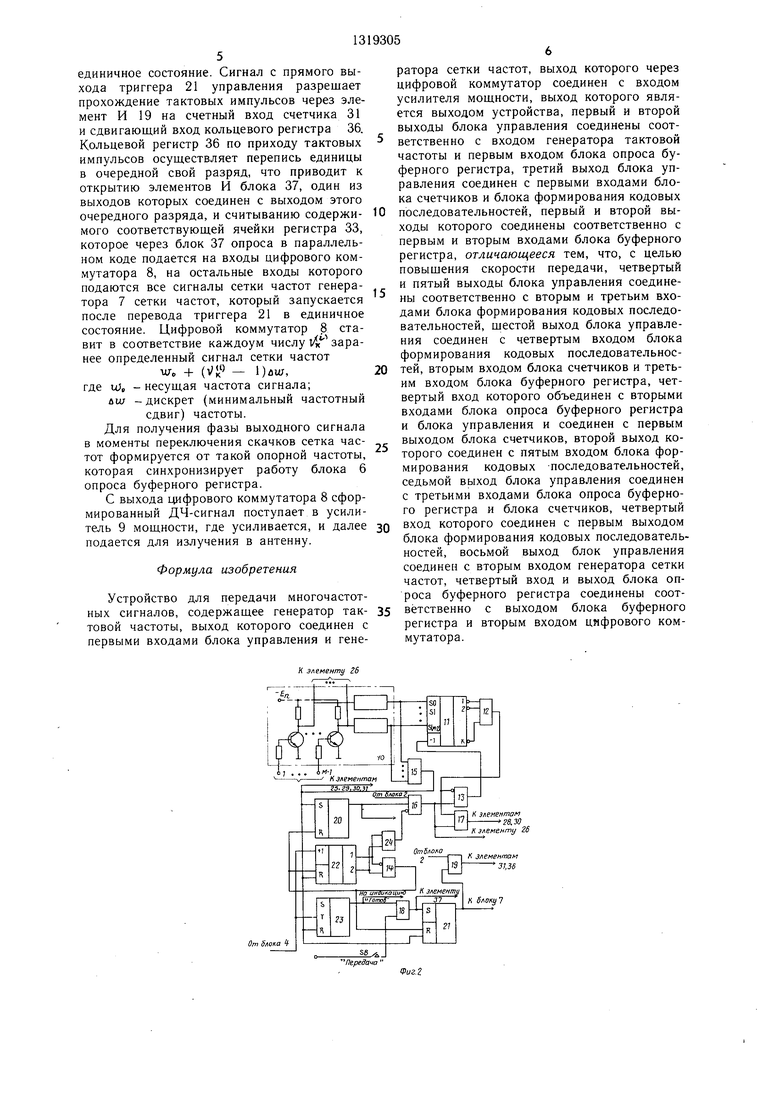

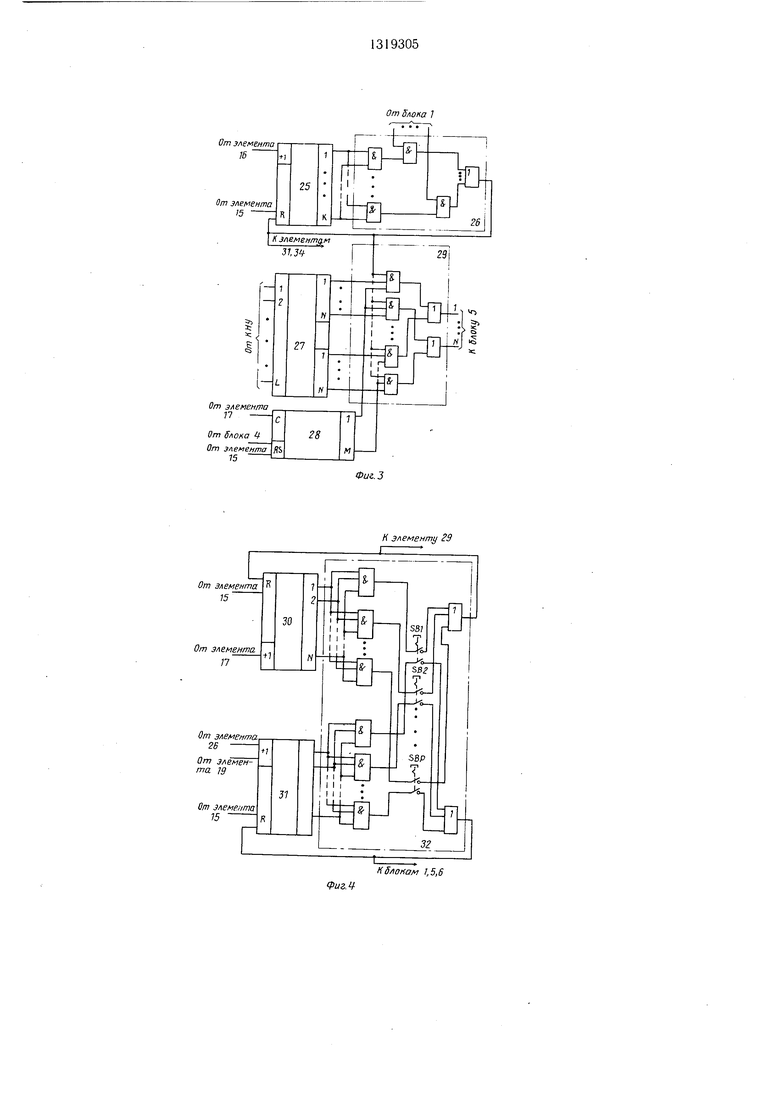

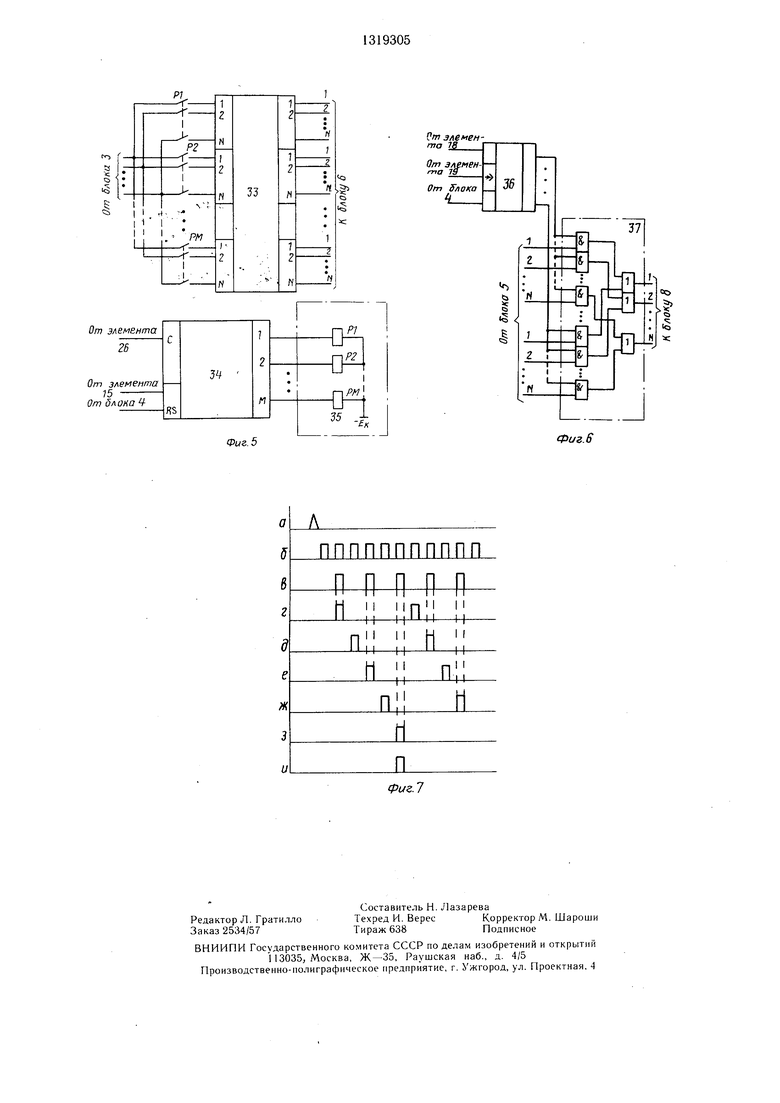

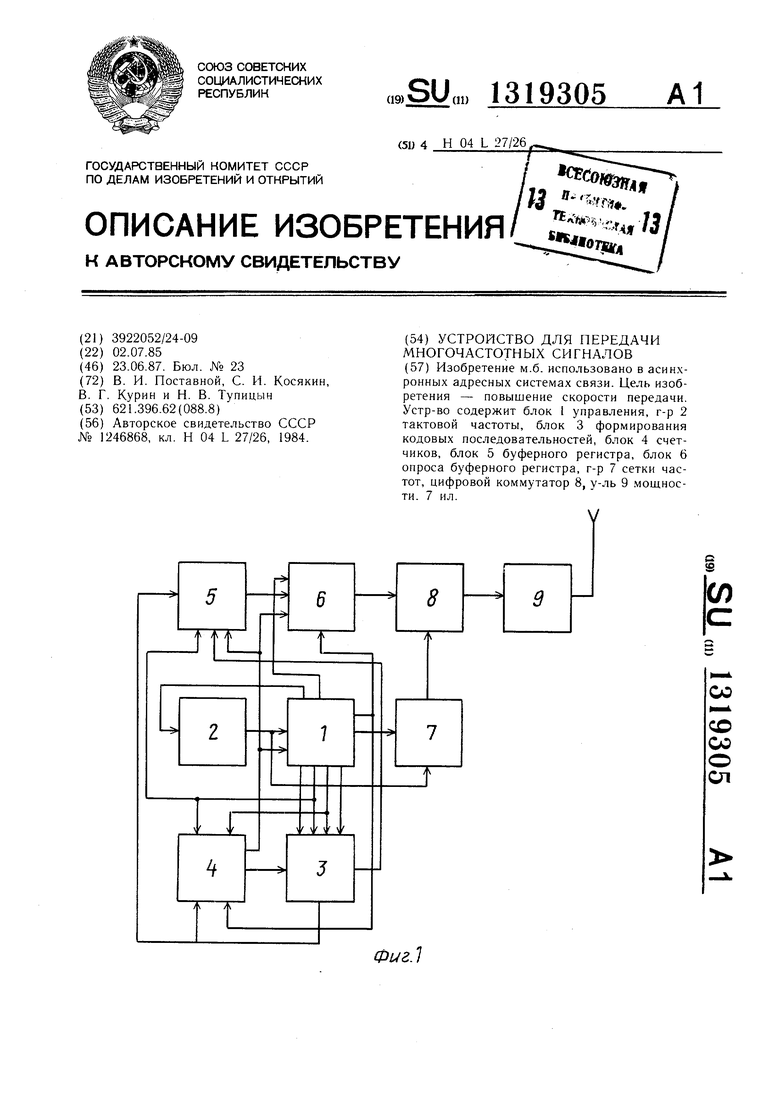

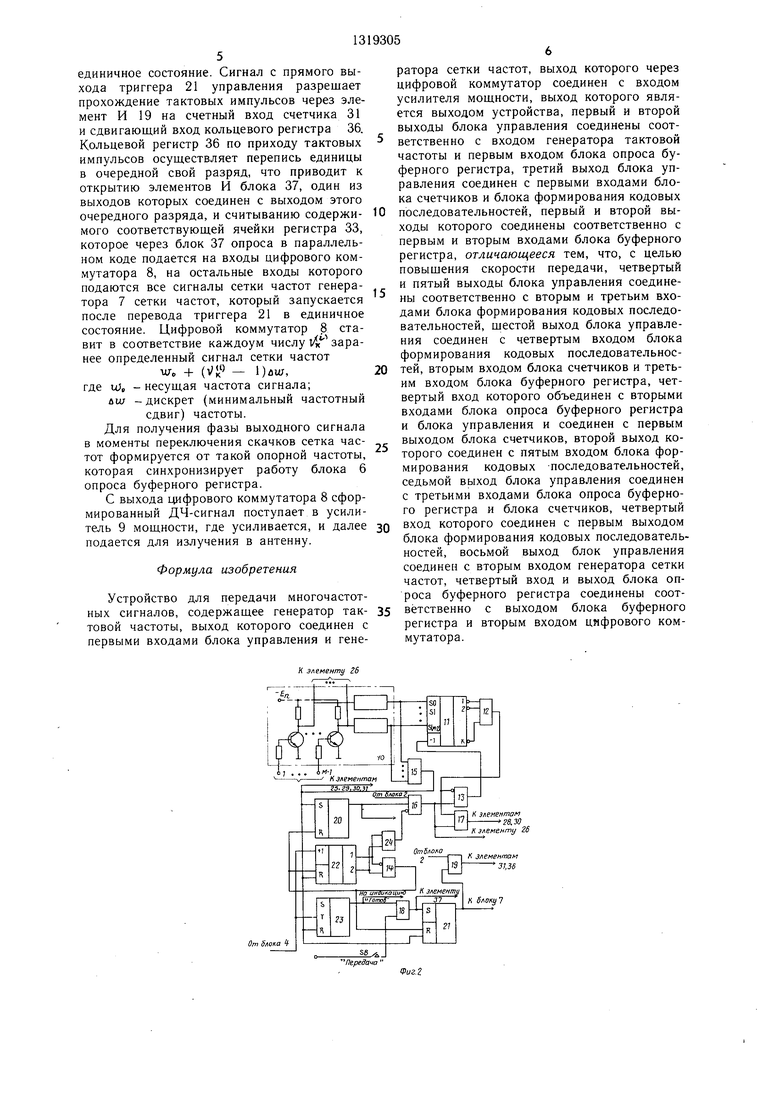

На фиг. 1 приведена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная схема блока управления; на фиг. 3 - структурная схема блока формирования кодовых последовательностей; на фиг. 4 - структурная электрическая схема блока счетчиков; на фиг. 5 - структурная схема блока буферного регистра; на фиг. 6 структурная схема блока опроса буферного регистра; на фиг. 7 - времен10

выхода дифференциального элемента блока 10 электронных ключей, пройдя через элемент ИЛИ 15, производит, поступая на вход, перевод триггера 20 в единичное состояние, обнуление триггеров 21 и 23 управления, счетчика 22 блока 1 управления, счетчика 25 блока 3 формирования кодовых последовательностей, счетчиков 30 и 31 блока 4 счетчиков с перенастраиваемым Кс,, кольцевого регистра 36 блока 6 опроса буферного регистра, установку в исходное состояние распределителя 28 импульсов блока 3 формирования кодовых последовательностей распределителя 34 уровней блока 5 буферного регистра. Установка распределителя 28

ные диаграммы, поясняющие работу блока 15 импульсов в исходное состояние означает, формирования кодовых последовательное-q-ro поступающий на вход распределителя

импульс после его установки в исходное состояние попадает в первый канал. Установка распределителя 34 уровней в исходтей 3.

Устройство содержит блок 1 управления, генератор 2 тактовой частоты, блок 3 формирования кодовых последовательностей, блокцое состояние предполагает после прихода 4 счетчиков, блок 5 буферного регистра, д i s-вход импульса наличие положительно- блок 6 опроса буферного регистра, генератор 7 сетки частот, цифровой коммутатор 8, усилитель 9 мощности; блок 1 управления состоит из блока 10 электронных ключей.

вычитающего счетчика 11, элементов И 12- 25 14, элемента ИЛИ 15, элементов И 16-19, триггеров 20 и 21 управления, счетчика 22, триггера 23 управления и элемента ИЛИ 24; блок 3 состоит из счетчика 25, блока 26 настройки, регистра 27, распределителя 28 импульсов и блока 29 считывания кода; 30 блок 4 счетчиков состоит из счетчиков 30 и 31 и блока 32 настройки; блок 5 буферного регистра состоит из регистра 33, распределителя 34 уровней и блока 35 реле; блок 6 опроса регистра состоит из кольцевого регистра 36 и блока 37 опроса..

Устройство работает следующим образом.

На блоке 4 счетчиков устанавливается база сигналов посредством нажатия одного из кнопочных выключателей SB1-SBP. 40 На блоке 1 управления выбирается номер передаваемого сигнала, для чего нажимается одна из М-1-й кнопок управления, сигнал с которой подается на одну из М-1-й

35

го уровня напряжения на выходе первого канала. Появление сигнала на прямом выходе триггера 20 управления блока 1 управления приводит к генератора 2 тактовой частоты. Тактовые импульсы с выхода генератора 2 тактовой частоты поступают на счетный вход счетчика 25 блока 3 формирования кодовых последовательностей и через элемент И 13 - на вычитающий вход вычитающего счетчика 11.

Частотная структура формируемых ДЧ- сигналов такова, что все сигналы, принадлежащие одной системе, имеют одинаковые частотные элементы на первой временной позиции. Для обеспечения этого условия работа счетчиков 25 и распределителя 28 импульсов блока 3 формирования кодовых последовательностей должна быть синхронизирована. Синхронизация достигается тем, что вычитающий счетчик 11 блока 1 управления блокирует прохождение тактовых импульсов через элемент И 17 блока 1 управления до тех пор, пока его состояние не будет соответствовать состоянию SO (все Триггеры счетчика обнулень). Если вычитающий счетчик 11 имеет состояние SO,

клемм блока 1 управления. Появление сиг- д то на выходе элемента И 12 появляется сигнала на одной из клемм приводит к открытию соответствующего электронного ключа блока 10 электронных ключей. По переднему фронту импульса дифференциальный элемент, подключенный к выходу электроннал, запрещающий прохождение тактовых импульсов на счетный вход вычитающего счетчика И и снимающий блокировку прохождения импульсов через элемент И 17. Тактовые импульсы, пройдя элемент И 17,

ного ключа, формирует короткий импульс, 50 подаются на вход распределителя 28 и.мкоторыи устанавливает вычитающий счетчик 11 в одно из состояний SO-S (М-2) в зависимости от того, частотная структура какого сигнала оптимальной системы формируется. Например, если формируется структура первого сигнала, вычитающий счетчик 11 устанавливается в исходное состояние О, если структура второго - 1, третьего -2 и т. д. Сигнал, снимаемый с

выхода дифференциального элемента блока 10 электронных ключей, пройдя через элемент ИЛИ 15, производит, поступая на вход, перевод триггера 20 в единичное состояние, обнуление триггеров 21 и 23 управления, счетчика 22 блока 1 управления, счетчика 25 блока 3 формирования кодовых последовательностей, счетчиков 30 и 31 блока 4 счетчиков с перенастраиваемым Кс,, кольцевого регистра 36 блока 6 опроса буферного регистра, установку в исходное состояние распределителя 28 импульсов блока 3 формирования кодовых последовательностей распределителя 34 уровней блока 5 буферного регистра. Установка распределителя 28

импульсов в исходное состояние означает, q-ro поступающий на вход распределителя

новка распределителя 34 уровней в исходцое состояние предполагает после прихода д i s-вход импульса наличие положительно-

цое состояние предполагает после прихода д i s-вход импульса наличие положительно-

0

0

5

го уровня напряжения на выходе первого канала. Появление сигнала на прямом выходе триггера 20 управления блока 1 управления приводит к генератора 2 тактовой частоты. Тактовые импульсы с выхода генератора 2 тактовой частоты поступают на счетный вход счетчика 25 блока 3 формирования кодовых последовательностей и через элемент И 13 - на вычитающий вход вычитающего счетчика 11.

Частотная структура формируемых ДЧ- сигналов такова, что все сигналы, принадлежащие одной системе, имеют одинаковые частотные элементы на первой временной позиции. Для обеспечения этого условия работа счетчиков 25 и распределителя 28 импульсов блока 3 формирования кодовых последовательностей должна быть синхронизирована. Синхронизация достигается тем, что вычитающий счетчик 11 блока 1 управления блокирует прохождение тактовых импульсов через элемент И 17 блока 1 управления до тех пор, пока его состояние не будет соответствовать состоянию SO (все Триггеры счетчика обнулень). Если вычитающий счетчик 11 имеет состояние SO,

то на выходе элемента И 12 появляется сигнал, запрещающий прохождение тактовых импульсов на счетный вход вычитающего счетчика И и снимающий блокировку прохождения импульсов через элемент И 17. Тактовые импульсы, пройдя элемент И 17,

5

пульсов блока 3 формирования кодовых последовательностей и счетный вход счетчика 30 блока 4 счетчиков.

Счетчик 25, распределитель 28 импульсов блока 3 формирования кодовых последовательностей, счетчики 30 и 31 блока 4 счетчиков обеспечивают опрос ячеек регистра 27. Причем счетчик 25 совместно с блоко.м 26 настройки задает номер сигнала в оптимальной системе. Достигается это тем, что блок 26 настройки устанавливает коэффициент счета счетчика 25 в соответствии с кнопкой ДЧ-сигнала оптимальной системы, нажатой в данный момент на блоке 1 управления. Если нажата первая кнопка, т. е. произошло открытие первого электронного ключа блока 10 электронных ключей, то блок 26 настройки блока 3 устанавливает коэффициент счета счетчика 25, равный 1

В двух произвольно выбранных ячейках не допускается записи одинаковых чисел. Порядок записи чисел в ячейки регистра 27 произвольный.

После считывания содержимое ячейки регистра 27 через блок 29 считывания кода в параллельном коде подается на N информационных входов блока 5 буферных регистров. Эти входы с помощью нор.мально разомкнутых контактов реле Р1-РМ по сиг(К 1), если нажата вторая кнопка, то О налам блока 35 реле подключаются к строго KM 2, и т. д.определенной N-разрядной ячейке регистра 33. Очередность подключения ячеек регистра 33 зависит от числа импульсов, которые вырабатывает счетчик 25 совместно с

ней, имеющего М каналов, причем, если число импульсов, поступивших на С-вход распределителя 34 уровней, равно Р , он устанавливается в исходное состояние, посi соответствует числу импульсов U, поступивших на вход распределителя 28 импульсов, причем i 1-Р , если LH р , р , для чего при Ь„ р счет- is блоком 26 настройки и которые поступают чик 30 совместно с блоком 32 настройки на тактовый С-вход распределителя 34 уров- вырабатывает управляющий сигнал, который принудительно устанавливает распределитель 28 импульсов в исходное состояние, j соответствует номеру ячейки регистра

27, которая связана с такой группой элемен- -20 кольку на его RS-вход подается управляю- тов И блока 29 считывания кода, на первых щий сигнал, вырабатываемый счетчиком 31

совместно с блоком 32 настройки. На первом выходе распределителя 34 уровней до момента окончания действия заднего фронта 25 первого импульса, поступившего на его С-вход, имеет место напряжение, что приводит к срабатыванию реле Р1 блока 35 реле, контакты которого подключают N информационных входов блока 5 буферных регистров к первой ячейке регистра 33. После окон- пульсов (фиг. 76) генератора тактовой час- чания действия заднего фронта первого им- тоты; на фиг. 7а - импульс первоначальной пульса появляется напряжение на втором выходе распределителя 34 уровней, что приводит к срабатыванию реле Р2 блока 35 реле и подключению N информационных выходов блока 29 считывания кода блока 3 к второй

жения на первом, втором и т. д. пятом вы- ячейке регистра 33. ходе распределителя 28 импульсов блока 3.Счетчик 31 совместно с блоком 32 наствходах которых имеет мест . сигнал, поступающий с выхода блока 26 настройки, а на третьих - сигнал с одного из выходов распределителя 28 импульсов.

На фиг. 7 показана диаграмма временной работы блока формирования кодовых последовательностей при Р 5, если формируется второй сигнал оптимальной системы, в зависимости от поступления тактовых имустановки, имеющей место на выходе элемента ИЛИ 15 блока 1 управления; на фиг; 7в - напряжение на выходе блока 26 настройки; на фиг. 7 г, д, е, ж, з - напряПоскольку рыходы распределителя 28 импульсов жестко связаны с выходами ячеек регистра 27, причем сигнал с выхода первого канала опрашивает при наличии сигнала с выхода блока 26 настройки первую ячейку регистра 27, сигнал с выхода второго канала - вторую ячейку, и т. д., то на временной диаграмме (фиг. 7) номера опрашиваемых ячеек регистра 27 соответствуют номеройки подсчитывает импульсы, формируемые счетчиком 25 и блоком 26 настройки, и вырабатывает управляющий сигнал, если 40 их число равно Р . Этот сигнал помимо установки в исходное состояние распределителя 34 уровней обнуляет регистр 36 блока 6 опроса буферных регистров, записывает единицу в счетчик 22 и триггер 23 управления блока 1 управления. На прямом выходе

рам выходов распределителя 28 импульсов триггера счетчика 22 появляется сигнал.

напряжение с которых перекрывается по времени с напряжением на фиг. 7 в. На фиг. 7 и напряжение, подаваемое на RS-распреде- лителя 28 импульсов блока 3 с второго управляющего выхода блока 4 счетчиков, сп Номера опрашиваемых ячеек регистра 27 для случая, показанного на временных диаграммах, последовательно во времени располагаются следующим образом: 1, 3, 5;, 2, 4-, что соответствует частотной структуре второго сигнала оптимальной системы. 55

В каждой ячейке регистра 27 может быть записано в двоичном коде одно из десятичных чисел от 1 до р , если Р- М, то последние ячейки заполняются нулями.

который через элемент ИЛИ 24 подается на инверсный в.ход элемента И 16 и блокирует прохождение через нее тактовых импульсов от генератора 2 тактовой частоты.

Появление сигнала на прямом выходе триггера 23 обеспечивает загорание индикатора «Готов, означающего, что частотная структура ДЧ-сигнала сформирована.

После нажатия на блоке 1 управления кнопочного выключателя («Передача) сигнал через элемент И 18 подается на запись в первый разряд кольцевого регистра 36 блока 6 опроса буферного регистра единицы. Сигнал на выходе эле.мента И 18 приводит к переводу триггера 21 управления в

В двух произвольно выбранных ячейках не допускается записи одинаковых чисел. Порядок записи чисел в ячейки регистра 27 произвольный.

После считывания содержимое ячейки регистра 27 через блок 29 считывания кода в параллельном коде подается на N информационных входов блока 5 буферных регистров. Эти входы с помощью нор.мально разомкнутых контактов реле Р1-РМ по сигналам блока 35 реле подключаются к строго определенной N-разрядной ячейке регистрые вырабатывает счетчик 25 совместно с

блоком 26 настройки и которые поступают на тактовый С-вход распределителя 34 уров-

ней, имеющего М каналов, причем, если число импульсов, поступивших на С-вход распределителя 34 уровней, равно Р , он устанавливается в исходное состояние, пос блоком 26 настройки и которые поступают на тактовый С-вход распределителя 34 уров-

кольку на его RS-вход подается управляю- щий сигнал, вырабатываемый счетчиком 31

ячейке регистра 33. Счетчик 31 совместно с блоком 32 настройки подсчитывает импульсы, формируемые счетчиком 25 и блоком 26 настройки, и вырабатывает управляющий сигнал, если их число равно Р . Этот сигнал помимо установки в исходное состояние распределителя 34 уровней обнуляет регистр 36 блока 6 опроса буферных регистров, записывает единицу в счетчик 22 и триггер 23 управления блока 1 управления. На прямом выходе

триггера счетчика 22 появляется сигнал.

триггера счетчика 22 появляется сигнал.

который через элемент ИЛИ 24 подается на инверсный в.ход элемента И 16 и блокирует прохождение через нее тактовых импульсов от генератора 2 тактовой частоты.

Появление сигнала на прямом выходе триггера 23 обеспечивает загорание индикатора «Готов, означающего, что частотная структура ДЧ-сигнала сформирована.

После нажатия на блоке 1 управления кнопочного выключателя («Передача) сигнал через элемент И 18 подается на запись в первый разряд кольцевого регистра 36 блока 6 опроса буферного регистра единицы. Сигнал на выходе эле.мента И 18 приводит к переводу триггера 21 управления в

единичное состояние. Сигнал с прямого выхода триггера 21 управления разрешает прохождение тактовых импульсов через элемент И 19 на счетный вход счетчика 31 и сдвигающий вход кольцевого регистра 36. Кольцевой регистр 36 по приходу тактовых импульсов осуществляет перепись единицы в очередной свой разряд, что приводит к открытию элементов И блока 37, один из выходов которых соединен с выходом этого очередного разряда, и считыванию содержи- мого соответствующей ячейки регистра 33, которое через блок 37 опроса в параллельном коде подается на входы цифрового коммутатора 8, на остальные входы которого подаются все сигналы сетки частот генератора 7 сетки частот, который запускается после перевода триггера 21 в единичное состояние. Цифровой коммутатор 8 ставит в соответствие каждоум числу t заранее определенный сигнал сетки частот

иг. + ( - 1)йи;, где ц;„ - несущая частота сигнала;

йш -дискрет (минимальный частотный сдвиг) частоты.

Для получения фазы выходного сигнала в моменты переключения скачков сетка час- тот формируется от такой опорной частоты, которая синхронизирует работу блока 6 опроса буферного регистра.

С выхода цифрового коммутатора 8 сформированный ДЧ-сигнал поступает в усилитель 9 мощности, где усиливается, и далее подается для излучения в антенну.

Формула изобретения

Устройство для передачи многочастотных сигналов, содержащее генератор так- товой частоты, выход которого соединен с первыми входами блока управления и гене

к элементу 26

5

.

о

5

0

ратора сетки частот, выход которого через цифровой коммутатор соединен с входом усилителя мощности, выход которого является выходом устройства, первый и второй выходы блока управления соединены соответственно с входом генератора тактовой частоты и первым входом блока опроса буферного регистра, третий выход блока управления соединен с первыми входами блока счетчиков и блока формирования кодовых последовательностей, первый и второй выходы которого соединены соответственно с первым и вторым входами блока буферного регистра, отличающееся тем, что, с целью повыщения скорости передачи, четвертый и пятый выходы блока управления соединены соответственно с вторым и третьим входами блока формирования кодовых последовательностей, щестой выход блока управления соединен с четвертым входом блока формирования кодовых последовательностей, вторым входом блока счетчиков и третьим входом блока буферного регистра, четвертый вход которого объединен с вторыми входами блока опроса буферного регистра и блока управления и соединен с первым выходом блока счетчиков, второй выход которого соединен с пятым входом блока формирования кодовых последовательностей, седьмой выход блока управления соединен с третьими входами блока опроса буферного регистра и блока счетчиков, четвертый вход которого соединен с первым выходом блока формирования кодовых последовательностей, восьмой выход блок управления соединен с вторым входом генератора сетки частот, четвертый вход и выход блока опроса буферного регистра соединены соответственно с выходом блока буферного регистра и вторым входом цифрового коммутатора.

От 5лока

Передача

Фиг.2

От 5лока 7

От элемента №

5

От элемента 77

От блока Ч

От элемента 75

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1354437A1 |

| Устройство для передачи многочастотных сигналов | 1987 |

|

SU1406817A1 |

| Устройство для передачи многочастотных сигналов | 1983 |

|

SU1107328A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1992 |

|

RU2031546C1 |

| Устройство для формирования сигналов частотно-фазовой манипуляции | 1984 |

|

SU1252968A1 |

| Устройство для отображения информации | 1986 |

|

SU1446642A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

Изобретение м.б. использовано в асинхронных адресных системах связи. Цель изобретения - повышение скорости передачи. Устр-во содержит блок 1 управления, г-р 2 тактовой частоты, блок 3 формирования кодовых последовательностей, блок 4 счетчиков, блок 5 буферного регистра, блок 6 опроса буферного регистра, г-р 7 сетки частот, цифровой коммутатор 8, у-ль 9 мощности. 7 ил. W СО со СО О ел Фиг.1

К элементу 29

К 5лакам 15,6

Cm зле менто 7.

От злрменто

гТ

0т f/ioKO

36

§

о

5 i

I

Фиг. 5

Редактор л. Гратилло Заказ 2534/57

ВНИИПИ Государственного комитета СССР поделай изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-иолиграфическое предприятие, г. Ужгород, ул. Проектная. 4

Фиг.б

Составитель Н. Лазарева

Техред И. ВересКорректор М. Шароши

Тираж 638Подписное

| Авторское свидетельство СССР № 1246868, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-23—Публикация

1985-07-02—Подача