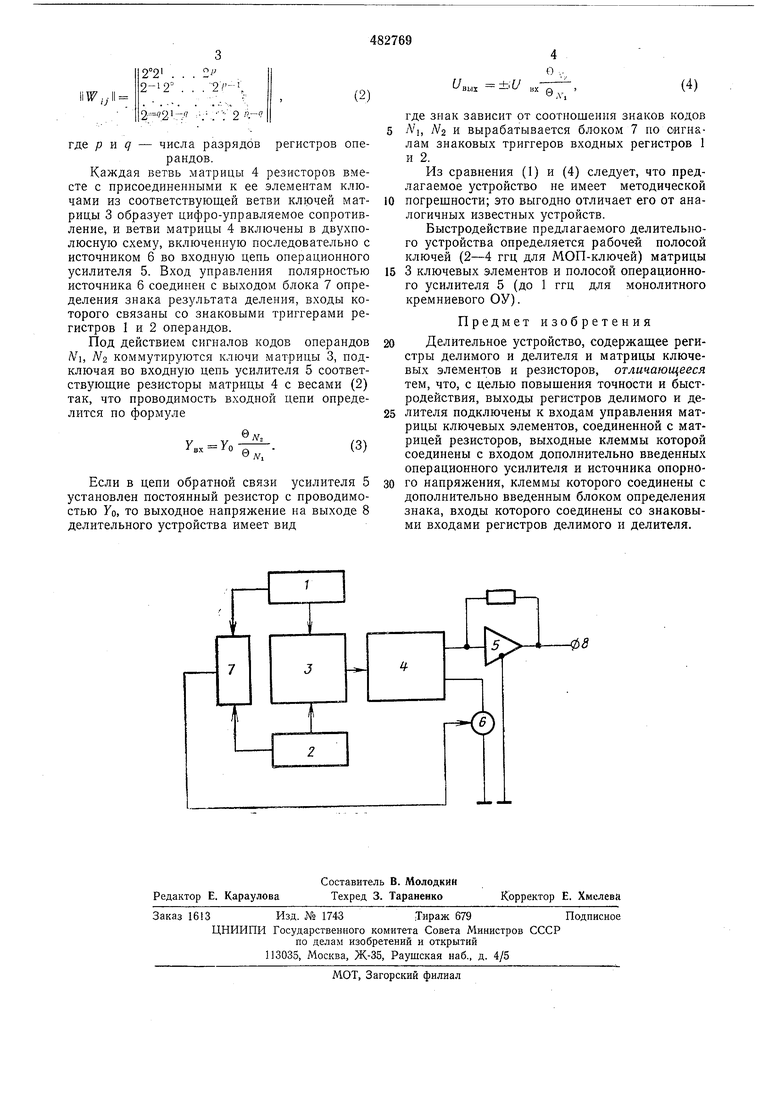

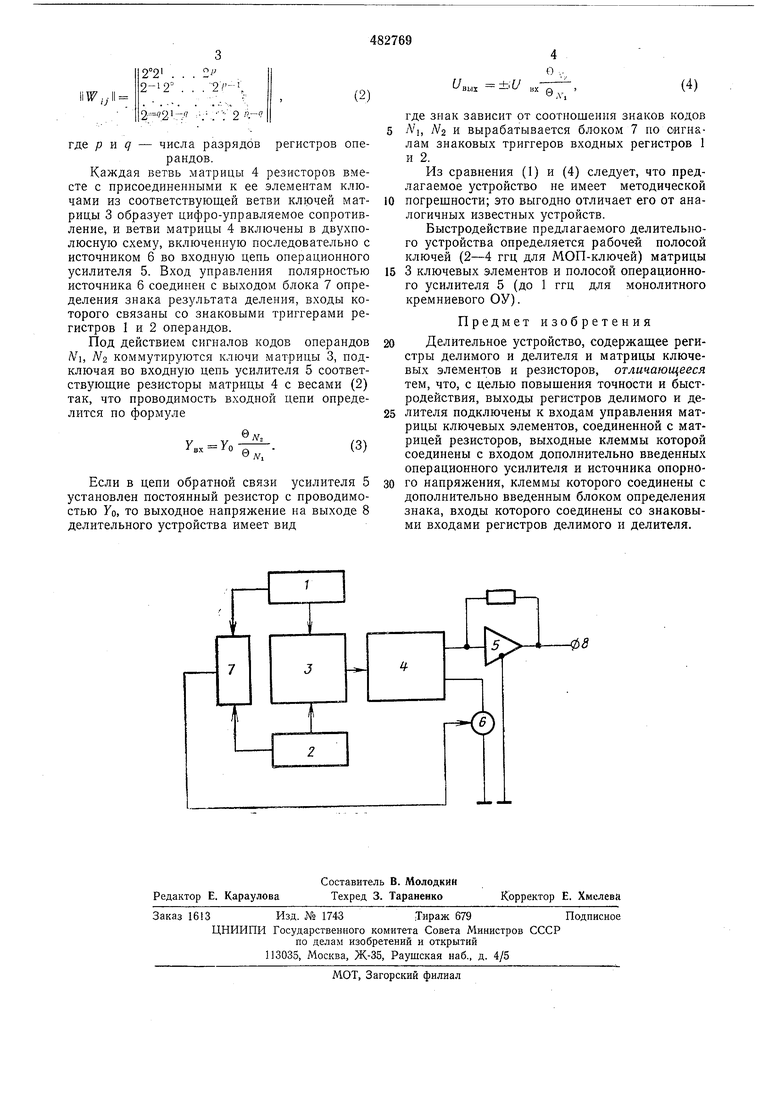

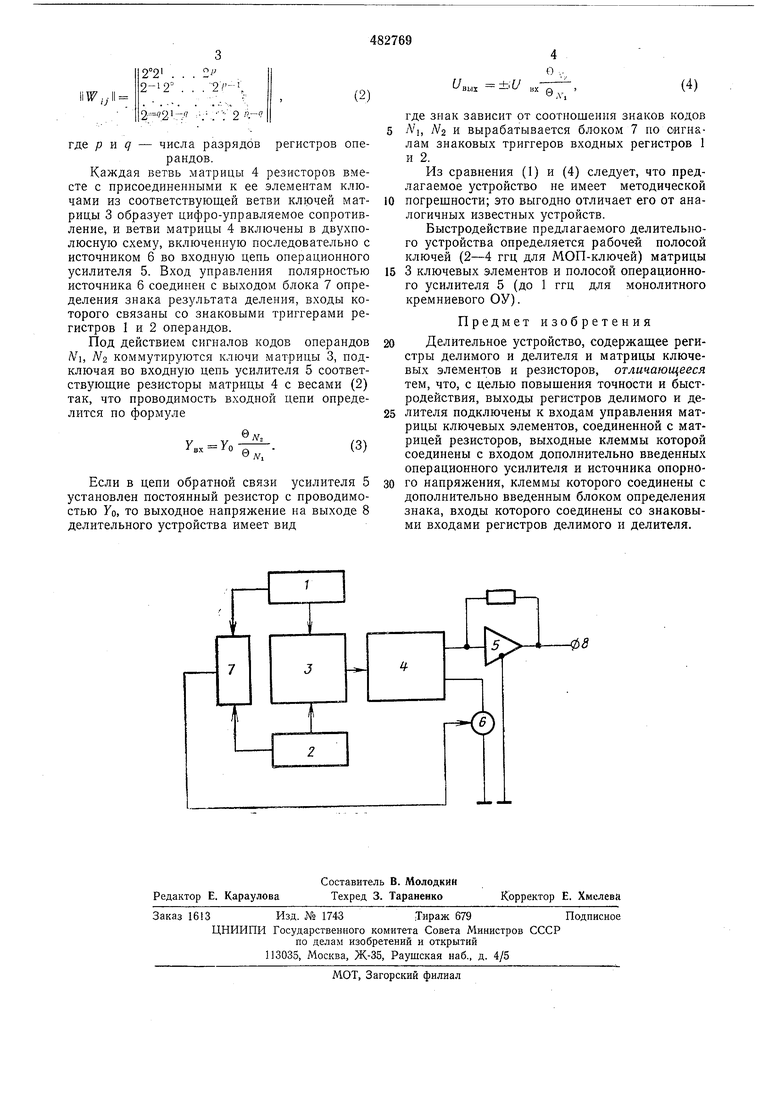

Изобретение относится к вычислительной технике и может использоваться для построения аналого-цифровых специализированных вычислителей для управляющих устройств широкого, применения. Известны делительные устройства, содержащие регистры делимого и делителя и матрицы ключевых элементов и резисторов. Такие устройства имеют методическую погрещность, так как напряжение на их выходе определяется зависимостью Для устранения этой погрешности обычно используют компенсационно-мостовые схемы включения цифро-аналоговых делителей напряжения. Однако компенсационно-мостовые схемы содержат устройства уравновешивания, резко снижающие быстродействие делительного цифрового управляемого сопротивления. С целью повышения точности и быстродействия в предлагаемом устройстве выходы регистров делимого и делителя подключены к входам управления матрицы ключевых элементов, соединенной с матрицей резисторов, выходные клеммы которой соединены с входом дополнительно введенных операционного 5 10 15 20 25 30 усилителя и источника опорного напряжения, клеммы которого соединены с дополнительно введенным блоком определения знака, входы последнего соединены со знаковыми входами регистров делимового и делителя. На чертел е приведена блок-схема предлагаемого устройства. Устройство содержит регистр 1 делимого, регистр 2 делителя, матрицу 3 ключевых элементов, матрицу 4 резисторов, операционный усилитель 5, источник 6 опорного напрял ения, блок 7 определения знака. Кодовые выходы регистров 1 и 2 делимого и делителя соединены с входами управления матрицы 3 ключевых элементов, сопряженной с матрицей 4 двоично-взвешенных по двум координатам постоянных резисторов. Выходные клеммы матрицы резисторов соединены с входом введенного дополнительно операционного усилителя 5 и управляемого источника 6 опорного напряжения. Клеммы управления полярностью выходного напряжения источника 6 соединены с дополнительно введенным блоком 7 определения знака, вход которого соединен со знаковыми триггерами регистров 2 и 1 делителя и делимого. Таблица весов резисторов матрицы 3 имеет вид 2°2 i 2-12° . . . 2/-, ..- 2 где p и q - числа разрядов регистров операндов. Каждая ветвь матрицы 4 резисторов вместе с присоединенными к ее элементам ключами из соответствующей ветви ключей матрицы 3 образует цифро-управляемое сопротивление, и ветви матрицы 4 включены в двухполюсную схему, включенную последовательно с источником 6 во входную цепь операционного усилителя 5. Вход управления полярностью источника 6 соединен с выходом блока 7 определения знака результата деления, входы которого связаны со знаковыми триггерами регистров 1 и 2 операндов. Под действием сигналов кодов операндов N, N2 коммутируются ключи матрицы 3, подключая во входную цепь усилителя 5 соответствующие резисторы матрицы 4 с весами (2) так, что проводимость входной цепи определится по формуле YBX. - YO Если в цепи обратной связи усилителя 5 установлен постоянный резистор с проводимостью УО, то выходное напряжение на выходе 8 делительного устройства имеет вид С/а„, ±.t/ „, где знак зависит от соотнощения знаков кодов N, NZ и вырабатывается блоком 7 но сигналам знаковых триггеров входных регистров 1 и 2. Из сравнения (1) и (4) следует, что предлагаемое устройство не имеет методической погрещности; это выгодно отличает его от аналогичных известных устройств. Быстродействие предлагаемого делительного устройства определяется рабочей полосой ключей (2-4 ГГЦ для МОП-ключей) матрицы 3 ключевых элементов и полосой операционного усилителя 5 (до 1 ггц для монолитного кремниевого ОУ). Предмет изобретения Делительное устройство, содержащее регистры делимого и делителя и матрицы ключевых элементов и резисторов, отличающееся тем, что, с целью повышения точности и быстродействия, выходы регистров делимого и делителя подключены к входам управления матрицы ключевых элементов, соединенной с матрицей резисторов, выходные клеммы которой соединены с входом дополнительно введенных операционного усилителя и источника опорного напряжения, клеммы которого соединены с дополнительно введенным блоком определения знака, входы которого соединены со знаковыми входами регистров делимого и делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Время-импульсное делительное устройство | 1977 |

|

SU721830A1 |

| УСТРОЙСТВО для ДЕЛЕНИЯ двоичных ЧИСЕЛ | 1968 |

|

SU220633A1 |

| Устройство для деления | 1986 |

|

SU1397903A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Аналоговое делительное устройство | 1983 |

|

SU1153331A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ ДЕЛИТЕЛЬ С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1998 |

|

RU2130639C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2019 |

|

RU2713758C1 |

| Многоканальный преобразователь угла поворота вала в код | 1980 |

|

SU947895A1 |

| Преобразователь однофазного напряжения | 1983 |

|

SU1302398A1 |

Авторы

Даты

1975-08-30—Публикация

1974-07-11—Подача