Изобретение относится к вычислительной технике и предназначено для использования в системах обработки и преобразования информации, для выполнения арифметических операций со смешанной формой представления входной и выходной информации с совмещением обработки и преобразования информации: умножения, деления, сложения, вычитания, умножения со сложением, деления с вычитанием, вычисления квадрата, умножения с повышенной точностью.

Наиболее близким по технической сущности является множительно-делительное устройство [1], содержащее реверсивный счетчик, переключатель, элемент И, тактовый генератор, цифроаналоговый преобразователь (ЦАП), первую и вторую схемы выбора аналогового операнда, компаратор, два ключа, два элемента памяти, генератор синхроимпульсов, первый, второй и третий аналоговые входы, цифровые входы, первый и второй аналоговые выходы, цифровые выходы, причем вход переключателя соединен с выходом элемента И, первый вход которого соединен с выходом тактового генератора, управляющий вход переключателя соединен с выходом компаратора, а управляющий вход реверсивного счетчика, второй вход элемента И, управляющие входы первого и второго ключей, первый и второй управляющие входы первой и второй схемы выбора аналогового операнда соединены с соответствующими выходами генератора синхроимпульсов, цифровые входы устройства соединены с цифровыми установочными входами реверсивного счетчика, выходы которого соединены с соответствующими входами цифроаналогового преобразователя и с соответствующими цифровыми выходами устройства, первый и второй аналоговые входы через первую схему выбора аналогового операнда соединены с аналоговым входом цифроаналогового преобразователя, аналоговый выход первого ключа соединен со входом первого элемента памяти, аналоговый выход которого соединен с первым аналоговым выходом устройства и с соответствующими аналоговыми входами первой и второй схем выбора аналогового операнда, аналоговый выход второго ключа соединен со входом второго элемента памяти, выход которого соединен со вторым аналоговым выходом устройства, выход цифроаналогового преобразователя соединен с аналоговыми входами первого и второго ключей и с инвертирующим входом компаратора, третий аналоговый вход через вторую схему выбора аналогового операнда соединен с неинвертирующим входом компаратора.

Устройство имеет следующие недостатки:

1) устройство имеет ограниченные функциональные возможности, выражающиеся в отсутствии операций сложения и вычитания, что создает трудности при реализации произвольных алгоритмов;

2) устройство выполняет операцию умножения с одинарной точностью, что создает трудности при реализации алгоритмов, требующих выполнения операции умножения с повышенной точностью (от одинарной до двойной точности).

Известны устройства [2, 3], реализующие способ умножения с двойной точностью путем разделения операндов на две части и последующего вычисления полного произведения с двойной точностью через сумму произведений частей операндов. Недостатком такого способа вычисления, изначально ориентированного на цифровую форму представления информации и точное вычисление частичных произведений и точное сложение с получением промежуточных и окончательных результатов вычисления в цифровой форме и реализованного в этих устройствах на цифровых вычислительных устройствах [2, 3], является невозможность выполнения умножения с двойной точностью путем разделения операндов на две части и последующего вычисления полного произведения с двойной точностью через сумму произведений частей операндов на не цифровых вычислительных устройствах (аналого-цифровых, аналоговых), имеющих случайную погрешность вычисления операций. Такие свойства погрешности при вычислении произведения частей операндов и вычислении суммы частичных произведений делают невозможным применение метода вычисления с двойной точностью применяемого в устройствах [2, 3] на устройствах, обладающих случайной погрешностью вычисления произведения, одним из которых является множительно-делительное устройство [1].

Цель изобретения - расширение области применения устройства за счет расширения функциональных возможностей через реализацию операций умножения со сложением и вычитания с делением и увеличения точности вычислений операции умножения.

Поставленная цель достигается тем, что в устройство, содержащее реверсивный счетчик, переключатель, элемент И, тактовый генератор, цифроаналоговый преобразователь, первую и вторую схемы выбора аналогового операнда, компаратор, два ключа, два элемента памяти, генератор синхроимпульсов, первый, второй и третий аналоговые входы, цифровые входы, первый и второй аналоговые выходы, цифровые выходы, причем вход переключателя соединен с выходом элемента И, первый вход которого соединен с выходом тактового генератора, управляющий вход переключателя соединен с выходом компаратора, а управляющий вход реверсивного счетчика, второй вход элемента И, управляющие входы первого и второго ключей, первый и второй управляющие входы первой и второй схемы выбора аналогового операнда соединены с соответствующими выходами генератора синхроимпульсов, цифровые входы устройства соединены с цифровыми установочными входами реверсивного счетчика, выходы которого соединены с соответствующими входами цифроаналогового преобразователя и с соответствующими цифровыми выходами устройства, первый и второй аналоговый вход через первую схему выбора аналогового операнда соединены с аналоговым входом цифроаналогового преобразователя, аналоговый выход первого ключа соединен со входом первого элемента памяти, аналоговый выход которого соединен с первым аналоговым выходом устройства и с соответствующими аналоговыми входами первой и второй схем выбора аналогового операнда, аналоговый выход второго ключа соединен со входом второго элемента памяти, выход которого соединен со вторым аналоговым выходом устройства, выход цифроаналогового преобразователя соединен с аналоговыми входами первого и второго ключей и с инвертирующим входом компаратора, третий аналоговый вход через вторую схему выбора аналогового операнда соединен с неинвертирующим входом компаратора; дополнительно введены третья схема выбора аналогового операнда, регистр, первый масштабный резистор, два элемента ИЛИ, устройство сравнения двух чисел, представленных в дополнительном коде, четвертый аналоговый вход, вторая группа цифровых выходов устройства.

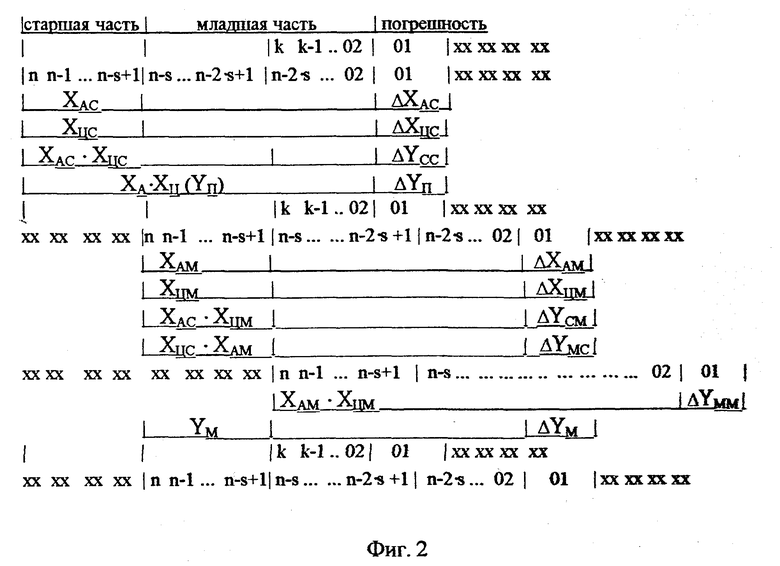

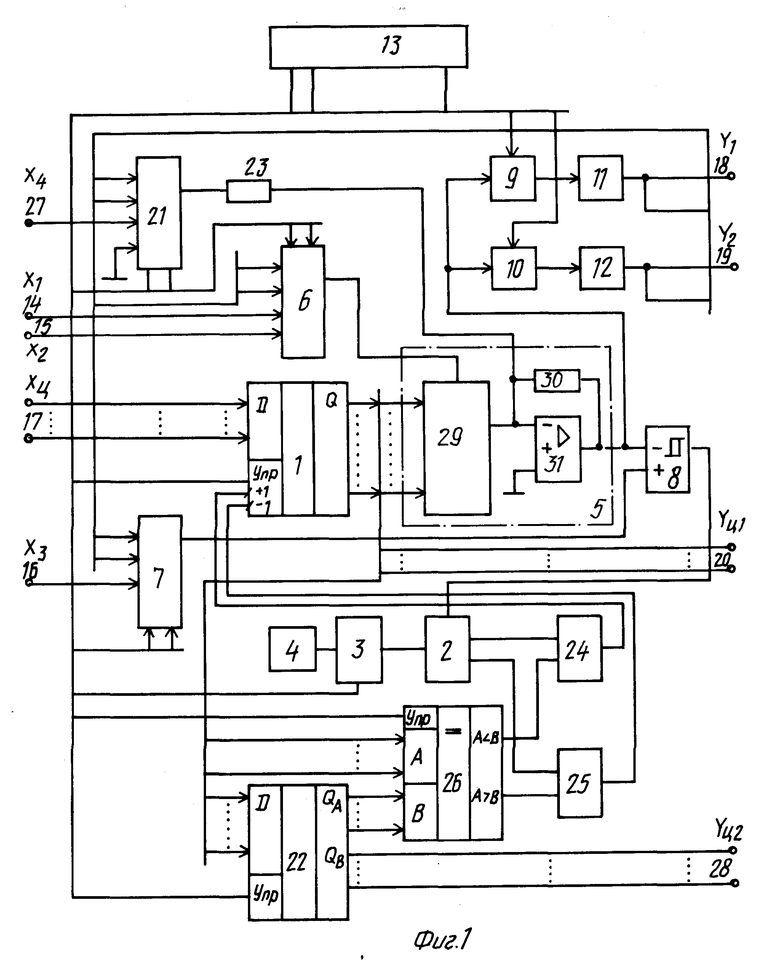

Функциональная схема устройства представлена на фиг. 1, на фиг. 2 показано расположение разрядов при выполнении операции умножения с повышенной точностью. Устройство содержит реверсивный счетчик 1, переключатель 2, элемент И 3, тактовый генератор 4, цифроаналоговый преобразователь 5, первую и вторую схемы выбора аналогового операнда 6, 7, компаратор 8, два ключа 9, 10, два элемента памяти 11, 12, генератор синхроимпульсов 13, первый, второй и третий аналоговые входы 14, 15, 16, цифровые входы 17, первый и второй аналоговые выходы 18, 19, цифровые выходы 20, третью схему выбора аналогового операнда 21, регистр 22, первый масштабный резистор 23, два элемента ИЛИ 24, 25, устройство сравнения двух чисел, представленных в дополнительном коде 26, четвертый аналоговый вход 27, вторая группа цифровых выходов 28 устройства, а цифроаналоговый преобразователь 5 содержит кодоуправляемый делитель напряжения 29, второй масштабный резистор 30, операционный усилитель 31, выход которого является выходом цифроаналогового преобразователя 5 и соединен через второй масштабный резистор 30 с инвертирующим входом операционного усилителя 31 и с выходом кодоуправляемого делителя напряжения 29, аналоговый и управляющий входы которого являются соответственно аналоговым и цифровым входом цифроаналогового преобразователя 5, причем инвертирующий вход операционного усилителя 31 подключен через первый масштабный резистор 23 через соответствующий вход третьей схемы выбора аналогового операнда 21 к четвертому аналоговому входу устройства 27, вход переключателя 2 соединен с выходом элемента И 3, первый вход которого соединен с выходом тактового генератора 4, управляющий вход переключателя 2 соединен с выходом компаратора 8, управляющий вход реверсивного счетчика 1, второй вход элемента И 3, управляющие входы первого и второго ключей 9, 10, первый и второй управляющие входы первой, второй и третьей схемы выбора аналогового операнда 6, 7, 21, управляющие входы регистра 22 и устройства сравнения двух чисел 26, представленных в дополнительном коде, соединены с соответствующими выходами генератора синхроимпульсов 13, цифровые входы устройства 17 соединены с цифровыми установочными входами реверсивного счетчика 1, выходы реверсивного счетчика 1 соединены с соответствующими входами цифроаналогового преобразователя 5 и с соответствующими цифровыми выходами устройства 22, первый и второй аналоговые входы устройства 14, 15 через первую схему выбора аналогового операнда 6 соединены с первым аналоговым входом цифроаналогового преобразователя 5, аналоговый выход первого ключа 9 соединен со входом первого элемента памяти 11, аналоговый выход которого соединен с первым аналоговым выходом устройства 18 и с соответствующими аналоговыми входами первой и второй схем выбора аналогового операнда 6, 7, аналоговый выход второго ключа 10 соединен со входом второго элемента памяти 12, выход которого соединен со вторым аналоговым выходом устройства 19, выход цифроаналогового преобразователя 5 соединен с аналоговым входом первого и второго ключей 9, 10 и с инвертирующим входом компаратора 8, третий аналоговый вход 16 через вторую схему выбора аналогового операнда 7 соединен с неинвертирующим входом компаратора 8, выход первого элемента памяти 11 соединен с соответствующим аналоговым входом третьего устройства выбора аналогового операнда 21, выход второго элемента памяти 12 соединен с соответствующими аналоговыми входами всех трех устройств выбора аналогового операнда 6, 7, 21, соответствующий аналоговый вход третьей схемы выбора аналогового операнда 21 соединен с шиной нулевого потенциала, первый выход переключателя 2 соединен с первым входом первого элемента ИЛИ 24, выход которого соединен с инкрементирующим входом реверсивного счетчика 1, второй выход переключателя 2 соединен с первым входом второго элемента ИЛИ 25, выход которого соединен с декрементирующим входом реверсивного счетчика 1, первая группа цифровых выходов реверсивного счетчика 1 соединена с первой группой цифровых входов устройства сравнения двух чисел 26, представленных в дополнительном коде, вторая группа цифровых выходов реверсивного счетчика 1 соединена с цифровыми входами регистра 22, управляющие входы регистра 22 и устройства сравнения двух чисел 26, представленных в дополнительном коде, соединены с соответствующими выходами генератора синхроимпульсов 13, первая группа цифровых выходов регистра 22 соединена со второй группой цифровых входов устройства сравнения двух чисел 26, представленных в дополнительном коде, вторая группа цифровых выходов регистра 22 соединена со второй группой цифровых выходов устройства 28, первый выход устройства сравнения двух чисел 26, представленных в дополнительном коде, устанавливающийся в единицу при условии, что двоичный код, установленный на первой группе входов устройства сравнения двух чисел 26, представленных в дополнительном коде, меньше значения кода, установленного на второй группе входов этого устройства, соединен со вторым входом первого элемента ИЛИ 24, второй выход устройства сравнения двух чисел 26, представленных в дополнительном коде, устанавливающийся в единицу при условии, что двоичный код, установленный на первой группе входов устройства сравнения двух чисел 26, представленных в дополнительном коде, больше значения кода, установленного на второй группе входов этого устройства, соединен со вторым входом второго элемента ИЛИ 25.

Устройство работает следующим образом.

Операция умножения цифровой величины на аналоговую величину со сложением с аналоговой величиной с получением результата в аналоговой форме реализуется по формуле:

Y1 = Xц • X1 + X4, (1)

где

Y1 - результат операции умножения со сложением в аналоговой форме;

Xц, X1 - первый и второй операнды сомножителей в цифровой и аналоговой форме;

X4 - третий операнд слагаемого в аналоговой форме.

При этом цифровая входная величина 17 Xц первого сомножителя записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 14 выбирается аналоговая величина второго сомножителя, с четвертого аналогового входа X4 27 поступает аналоговая величина слагаемого, сомножитель X1 поступает на аналоговый вход ЦАП 5, на инвертирующий вход операционного усилителя 31 подается напряжение с выхода кодоуправляемого делителя напряжения 29, соответствующее произведению Xц • X1, которое суммируется с аналоговой величиной слагаемого X4, поданной на второй аналоговый вход цифроаналогового преобразователя 5, на инвертирующий вход операционного усилителя 31, для обеспечения операции суммирования по формуле (1) номинал первого масштабного резистора 23 выбирается равным номиналу второго масштабного резистора 30, установленного в цифроаналоговом преобразователе 5, обеспечивающего режим отрицательной обратной связи операционного усилителя 31, результат выполнения операции сформирован на выходе операционного усилителя 31 и на выходе цифроаналогового преобразователя 5, ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (1) запоминается элементом 11 и устанавливается на выходе устройства Y1 18.

Операция умножения цифровой величины на аналоговую величину со сложением с аналоговой величиной с получением результата в цифровой форме реализуется по формуле:

Yц1 = Xц • X1 + X4, (2)

где

Yц1 - результат операции умножения со сложением в цифровой форме;

Xц, X1 - первый и второй операнды в цифровой и аналоговой форме;

X4 - третий операнд слагаемого в аналоговой форме.

При этом выполняются преобразования по формуле (1) и затем на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп, через соответствующий аналоговый вход с элемента памяти 11 выбирается аналоговая величина результата, вычисленного по формуле (2), с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, при этом опорное напряжение Eоп и аналоговая величина результата поступают на аналоговый вход ЦАП 5 и на неинвертирующий вход компаратора 8 соответственно, на управляющий вход устройства сравнения двух чисел, представленных в дополнительном коде 26, с генератора синхроимпульсов 13 подается закрывающий сигнал и выходы устройства сравнения двух чисел, представленных в дополнительном коде 26, устанавливаются в логический ноль, на управляющий вход элемента И 3 с генератора синхроимпульсов 13 подается логическая единица, что разрешает прохождение сигналов с тактового генератора 4 на вход переключателя 2, выход компаратора 8 управляет переключателем 2 для прохождения сигналов либо через элемент ИЛИ 24 на инкрементирующий вход реверсивного счетчика 1, либо через элемент ИЛИ 25 на декрементирующий вход реверсивного счетчика 1, производится цикл преобразования Eоп•N=Y1, где N - выходной двоичный код счетчика 1 и устанавливается на выходе устройства Yц1 20.

Операции сложения двух операндов в аналоговой или цифровой формах представления с формированием результата в аналоговой или цифровой форме представления выполняется путем установки единичных значений не используемого операнда сомножителя тернарных операций, вычисляемых по формулам (1, 2). Для цифрового операнда сомножителя Xц единичное значение соответствует единичным значениям всех двоичных разрядов. Для аналогового операнда сомножителя X1 единичное значение соответствует опорному напряжению Eоп.

Операция сложения двух операндов в цифровой форме представления с формированием результата в аналоговой или цифровой форме представления выполняются путем предварительного преобразования одного из цифровых операндов в аналоговую форму представления с запоминанием результата в элементе памяти и последующим выполнением операции сложения второго цифрового операнда со значением, запомненным в элементе памяти с предварительной установкой единичного значения операнда сомножителя тернарных операций, вычисляемых по формулам (1, 2).

Операция деления разности двух аналоговых величин на третью аналоговую величину с представлением результата в цифровой форме реализуется по формуле:

Yц1 = (X3 - X4)/X1, (3)

где

Yц1 - результат операции деления в цифровой форме;

X3, X4 - исходный операнд и вычитаемое в аналоговой форме;

X1 - делитель в аналоговой форме.

При этом на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 14 выбирается аналоговая величина делителя, с третьего аналогового входа X3 16 выбирается аналоговая величина делимого, с четвертого аналогового входа X4 27 выбирается аналоговая величина вычитаемого, при этом аналоговые величины делителя и делимого поступают на аналоговый вход ЦАП 5 и на неинвертирующий вход компаратора 8 соответственно, на тактовый вход счетчика 1 поступают импульсы и производится цикл преобразования X1 • N = (X3 - X4), где N - выходной двоичный код счетчика 1, сформированный в счетчике 1 код, соответствующий формуле (3), устанавливается на выходе устройства Yц1 20.

Операция деления двух аналоговых величин с представлением результата в аналоговой форме реализуется по формуле:

Y1 = (X3 - X4)/X1, (4)

где

Y1 - результат операции деления в аналоговой форме;

X3, X4 - исходный операнд и вычитаемое в аналоговой форме;

X1 - делитель в аналоговой форме.

При этом выполняются преобразования по формуле (3) и затем на управляющие входы первой схемы выбора аналогового операнда 6 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп и поступает на аналоговый вход ЦАП 5, ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (4) запоминается элементом 11 и устанавливается на выходе устройства Y1 18.

Операции вычитания двух операндов в аналоговой форме представления с формированием результата в аналоговой или цифровой форме представления выполняются путем установки единичного значения операнда делителя Eоп тернарных операций, вычисляемых по формулам (3, 4).

Операция вычитания двух операндов, один из которых в цифровой форме, а другой в аналоговой форме представления, с формированием результата в аналоговой или цифровой форме представления выполняется путем предварительного преобразования цифрового операнда в аналоговую форму представления с запоминанием результата в элементе памяти и последующим выполнением операции вычитания значения, запомненного в элементе памяти, и оставшегося операнда в аналоговой форме путем установки единичных значений операнда делителя Eоп тернарных операций, вычисляемых по формулам (3, 4).

Операция вычитания двух операндов в цифровой форме представления с формированием результата в аналоговой или цифровой форме представления выполняется путем предварительного преобразования цифровых операндов в аналоговую форму представления с запоминанием результата в элементах памяти и последующим выполнением операции вычитания значений, запомненных в элементах памяти, путем установки единичных значений операнда делителя Eоп тернарных операций, вычисляемых по формулам (3, 4).

Операция умножения двух аналоговых величин с представлением результата в аналоговой форме реализуется по формуле:

Y1 = X1 • X3, (5)

где

Y1 - результат операции умножения в аналоговой форме;

X1, X3 - первый и второй операнды в аналоговой форме.

При этом на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп, с третьего аналогового входа X3 16 выбирается аналоговая величина второго сомножителя, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция деления с вычитанием с формированием результата преобразования аналоговой величины второго сомножителя X3 в двоичный код счетчика 1.

Затем на управляющие входы первой схемы выбора аналогового операнда 6 поступают сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 14 выбирается аналоговая величина первого сомножителя и выполняется операция умножения со сложением, ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (5) запоминается элементом 11 и устанавливается на выходе устройства Y1 18.

Операция умножения двух аналоговых величин с представлением результата в цифровой форме реализуется по формуле:

Yц1 = X1 • X3, (6)

где

Yц1 - результат операции умножения в цифровой форме;

X1, X3 - первый и второй операнды в аналоговой форме.

При этом выполняются преобразования по формуле (5) и затем на управляющие входы первой, второй, третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп, через соответствующий аналоговый вход с элемента памяти 11 выбирается аналоговая величина результата, вычисленного по формуле (6), при этом опорное напряжение Eоп и аналоговая величина результата поступают на аналоговый вход ЦАП 5 и на неинвертирующий вход компаратора 8, выполняется операция деления с вычитанием с формированием результата преобразования аналоговой величины элемента памяти 11 в двоичный код счетчика 1 и устанавливается на выходе устройства Yц1 20.

Операция умножения аналоговой величины на цифровую величину с представлением результата в аналоговой форме реализуется по формуле:

Y1 = Xц • X1, (7)

где

Y1 - результат операции умножения в аналоговой форме;

Xц, X1 - первый и второй операнды в цифровой и аналоговой форме.

При этом на управляющие входы третьей схемы выбора аналогового операнда 21 поступают сигналы с генератора синхроимпульсов 13, по которым с соответствующего аналогового входа выбирается напряжение 0 В, и выполняется операция умножения со сложением по формуле (1), результат вычисления, соответствующий формуле (7), запоминается элементом 11 и устанавливается на выходе устройства Y1 18.

Операция умножения аналоговой величины на цифровую величину с представлением результата в цифровой форме реализуется по формуле:

Yц1 = Xц • X1, (8)

где

Yц1 - результат операции умножения в цифровой форме;

Xц, X1 - первый и второй операнды в цифровой и аналоговой форме.

При этом на управляющие входы третьей схемы выбора аналогового операнда 21 поступают сигналы с генератора синхроимпульсов 13, по которым с соответствующего аналогового входа выбирается напряжение 0 В, и выполняется операция умножения со сложением по формуле (2), результат вычисления, соответствующий формуле (8), формируется в счетчике 1 и устанавливается на выходе устройства Yц1 20.

Операция деления двух аналоговых величин с представлением результата в цифровой форме реализуется по формуле:

Yц1 = X3/X1, (9)

где

Yц1 - результат операции деления в цифровой форме;

X3, X1 - делимое и делитель в аналоговой форме.

При этом на управляющие входы третьей схемы выбора аналогового операнда 21 поступают сигналы с генератора синхроимпульсов 13, по которым с соответствующего аналогового входа выбирается напряжение 0 В, и выполняется операция деления с вычитанием по формуле (3), результат вычисления, соответствующий формуле (9), формируется в счетчике 1 и устанавливается на выходе устройства Yц1 20.

Операция деления двух аналоговых величин с представлением результата в аналоговой форме реализуется по формуле:

Y1 = X3/X1, (10)

где

Y1 - результат операции деления в аналоговой форме;

X3, X1 - делимое и делитель в аналоговой форме.

При этом на управляющие входы третьей схемы выбора аналогового операнда 21 поступают сигналы с генератора синхроимпульсов 13, по которым с соответствующего аналогового входа выбирается напряжение 0 В, и выполняется операция деления с вычитанием по формуле (4), результат вычисления, соответствующий формуле (10), запоминается элементом 11 и устанавливается на выходе устройства Y1 18.

Операция деления цифровой величины на аналоговую величину с представлением результата в цифровой форме реализуется по формуле:

Yц1 = Xц/X1, (11)

где

Yц1 - результат операции деления в цифровой форме;

Xц, X1 - делимое и делитель в цифровой и аналоговой форме.

При этом цифровая входная величина 17 Xц делимого записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп и поступает на аналоговый вход ЦАП 5, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция умножения со сложением, ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат запоминается элементом 11. Затем на управляющие входы второй схемы выбора аналогового операнда 7 поступают сигналы с генератора синхроимпульсов 13, по которым через первый аналоговый вход с элемента памяти 11 выбирается аналоговая величина, соответствующая цифровому операнду Xц, и подается на неинвертирующий вход компаратора 8, на управляющие входы первой схемы выбора аналогового операнда 6 подаются сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 14 выбирается аналоговая величина делителя и выполняется операция деления с вычитанием по формуле (3), результат вычисления, соответствующий формуле (11), формируется в счетчике 1 и устанавливается на выходе устройства Yц1 20.

Операция деления цифровой величины на аналоговую величину с представлением результата в аналоговой форме реализуется по формуле:

Y1 = Xц/X1, (12)

где

Y1 - результат операции деления в аналоговой форме;

Xц, X1 - делимое и делитель в цифровой и аналоговой форме.

При этом выполняются преобразования по формуле (7) и затем на управляющие входы третьей схемы выбора аналогового операнда 21 поступают сигналы с генератора синхроимпульсов 13, по которым с соответствующего аналогового входа выбирается напряжение 0 В, и выполняется операция деления с вычитанием по формуле (4), результат вычисления, соответствующий формуле (12), запоминается элементом 11 и устанавливается на выходе устройства Y1 18.

Операция возведения в квадрат аналоговой величины с представлением результата в аналоговой форме реализуется по формуле:

Y1 = X3 • X3, (13)

где

Y1 - результат операции возведения в квадрат в аналоговой форме;

X3 - операнд в аналоговой форме.

При этом на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп, с третьего аналогового входа X3 16 выбирается аналоговая величина операнда, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция деления с вычитанием по формуле (3), результат преобразования сомножителя X3 формируется в счетчике 1, затем ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат запоминается элементом 11. Затем на управляющие входы первой схемы выбора аналогового операнда 6 поступают сигналы с генератора синхроимпульсов 13, по которым через соответствующий аналоговый вход с элемента памяти 11 выбирается аналоговая величина, соответствующая операнду X3, которая поступает на аналоговый вход ЦАП 5, ключ 10 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (13) запоминается элементом 12 и устанавливается на выходе устройства Y2 19.

Операция возведения в квадрат цифровой величины с представлением результата в аналоговой форме реализуется по формуле:

Y1 = Xц • Xц, (14)

где

Y1 - результат операции возведения в квадрат в аналоговой форме;

Xц - операнд в цифровой форме.

При этом цифровая входная величина 17 Xц записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 12 выбирается напряжение Eоп и поступает на аналоговый вход ЦАП 5, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется преобразование цифровой величины в аналоговую, ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат запоминается элементом 11. Затем на управляющие входы первой схемы выбора аналогового операнда 6 поступают сигналы с генератора синхроимпульсов 13, по которым через соответствующий аналоговый вход с элемента памяти 11 выбирается аналоговая величина, соответствующая операнду Xц, и сомножитель Xц поступает на аналоговый вход ЦАП 5, ключ 10 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (14) запоминается элементом 12 и устанавливается на выходе устройства Y2 19.

Вычисление операции умножения с повышенной точностью выполняется следующим образом.

Для вычисления операции умножения с повышенной точностью на заявляемом устройстве выполняется разделение исходных операндов на две части. Для операндов зафиксированы формат разделения и порядок подачи операндов для вычисления. Операнды, представленные в виде двоичных слов длиной n разрядов, разделяются на s старших разрядов и m младших разрядов. При вычислении на известном устройстве точность вычисления соответствует n двоичным разрядам.

Цифровые операнды в устройстве интерпретируются как числа в диапазоне от нуля до единицы, представленные в прямом n-разрядном двоичном коде, записанном в виде одного слова. Старший n-й разряд расположен слева. Вычисления на известном устройстве выполняются с погрешностью в младшем (первом) двоичном разряде. Погрешность выполнения последовательности операций на известном устройстве накапливается в младших "разрядах" результата операций.

Вариант разделения для известного вычислительного устройства выбирается исходя из соотношений:

n=s+m, m=s+k, s≥1, k≥1, (15)

где

n - количество разрядов слова операндов,

s - количество старших разрядов;

m - количество младших разрядов;

k - количество контрольных разрядов.

Расширение динамического диапазона выполняется за счет переноса значащих разрядов в старшую часть числа с обнулением младших незначащих разрядов. При последующем выполнении операций над числами с расширенным диапазоном уменьшается влияние инструментальных ошибок известного устройства за счет "удаленности" значащих разрядов исходных операндов от ошибочных младших разрядов.

Исходные операнды представлены в цифровой Xц и аналоговой форме Xа с точностью, обеспечиваемой известным устройством - n разрядов. Для вычисления с повышенной точностью от n+1 до 2•n-s-k+1 разрядов, в зависимости от варианта разделения операндов, предварительно подготавливаются части операндов. Формулы разделения на части:

Xа = Xас + Nмсм • Xам;

Xц = Xцс + Nмсм • Xцм, (16)

где

Xа - первый исходный операнд в аналоговой форме;

Xц - второй исходный операнд в цифровой форме;

Xас, Xам - старшая и младшая части операнда Xа в аналоговой форме;

Nмсм - масштабный коэффициент в цифровой форме;

Xцс, Xцм - старшая и младшая части операнда Xц в цифровой форме.

Масштабный коэффициент вычисляется по формуле:

Nмсм = 2-s, (17)

где

Nмсм - масштабный коэффициент в цифровой форме;

s - количество старших разрядов.

При умножении с повышенной точностью вычисляются частичные произведения Xас • Xцм, Xам • Xцс, Xам • Xцм с суммированием с масштабным коэффициентом для произведения младших частей по формуле:

Yм = Xас • Xцм + Xам • Xцс + Nмсм • Xам • Xцм, (18)

где

Yм - сумма частичных произведений младших частей;

Xас, Xам - старшая и младшая части операнда Xа в аналоговой форме;

Nмсм - масштабный коэффициент в цифровой форме;

Xцс, Xцм - старшая и младшая части операнда Xц в цифровой форме.

Погрешности выполнения операций (умножения, умножения со сложением) накапливаются в младших разрядах Yм. При последующем формировании результата выполнения операции умножения Y, то есть при сложении Yм с соответствующими масштабными коэффициентами со старшей частью результата, погрешности Yм, перенесенные в конечный результат, уменьшаются в 2-s раз.

Учитывая "просачивание" ошибки в старшие разряды результата способ вычисления старших разрядов операции умножения с повышенной точностью состоит в использовании априорной информации о старших разрядах двоичного кода результата. Полное произведение исходных операндов вычисляется с точностью n разрядов по формуле:

Yп = Xа • Xц. (19)

Вычисление Yп подменяет вычисление произведения старших частей Yсс разделенных операндов и вычисление точного полного произведения Y:

Yсс = Xас • Xцс;

Y = Yсс + Nмсм • Yм. (20)

Операция арифметического суммирования с масштабным коэффициентом Nмсм заменяется сочленением соответствующих двоичных разрядов Yп и Yм.

Расположение разрядов при выполнении операции умножения по частям на известном устройстве по методу разделения операндов показано на фиг. 2. Числа, показанные на фиг. 2, представлены в прямом n разрядном двоичном коде без знака. На фиг. 2 выделены границы расположения старших s разрядов, старших 2•s разрядов, граница расположения погрешности вычисления на известном устройстве при вычислении с n старшими разрядами находится в первом разряде и может расширятся в сторону старших разрядов при выполнении цепочки операций с накоплением погрешности вычисления.

Сумма частичных произведений Yм вычисляется с погрешностью ΔYM. Полное произведение Yп вычисляется с погрешностью ΔYП. Вместо сложения произведений частей Yсс, Yм в результат Y с масштабным коэффициентом Nмсм по формуле (20), возможное при устранении погрешности ΔYCC, используется сочленение полного произведения Yп, вычисленного по формуле (19), и суммы частичных произведений Yм в единый результат Y с предварительным устранением погрешности ΔYП из полного произведения Yп с целью получения точного значения старших разрядов результата  и сочленения

и сочленения  и Yм в единый результат Y.

и Yм в единый результат Y.

"Просачивание" ошибки в старшие разряды и накопление ошибок в младших разрядах при вычислении полного произведения на известном устройстве с точностью вычисления n разрядов может привести к искажению значения кода старших разрядов Yп. Восстановление истинного значения кода старших разрядов Yп выполняется путем коррекции этого кода по априорной информации о значении старших разрядов кодов суммы частичных произведений младших разрядов Yм. Совпадение разрядов Yп начинается с n-2s-го разряда и заканчивается на первом разряде Yп и соответствует разрядам Yм начиная с n-s-го разряда и заканчивая на k-м разряде Yм, что показано на фиг. 2. Коды суммы частичных произведений младших разрядов Yм начиная с n-s-го разряда и заканчивая на k-м разряде используются в качестве контрольных для коррекции Yп по Yм.

Старшая часть результата формируется в счетчике 1 в виде n разрядного слова. Младшая часть произведения, вычисленного с повышенной точностью Yм, сформирована с точностью n-s разрядов (точность n разрядов, обеспечиваемая известным устройством для вычисления Yм за вычетом пересечения старших n .. n-s разрядов, непригодных для использования в качестве контрольных из-за их несовпадения с n-s .. n-2s разрядами Yп) и записана в регистре 22 начиная с n-s разряда (с отбрасыванием старших s разрядов) до первого разряда, кроме того, отбрасываются k контрольных разрядов, уже сформированных в младших k разрядах счетчика 1, что соответствует разрядам повышенной точности от n+1-го до 2n-s-k-го.

Учитывая совпадение разрядов Yм начиная с n-s-го разряда и заканчивая k-м разрядом Yм с соответствующими разрядами Yп начиная с n-2s-го разряда и заканчивая первым разрядом Yп, разряды Yм начиная с n-s-го разряда и заканчивая k-м разрядом, могут быть использованы в качестве эталонных разрядов для коррекции разрядов Yп, содержащих ошибку, и назначены как k двоичных контрольных разрядов, удовлетворяющих условиям:

2s+k=n, k≥1, (21)

где

k - количество контрольных разрядов;

s - количество старших разрядов;

n - количество достоверно вычисленных старших разрядов, совпадающее с количеством разрядов, обеспечиваемых устройством.

Для вычисления операции умножения с повышенной точностью на заявляемом устройстве выполняется разделение исходных операндов заранее, вне устройства, и формируется следующий порядок подачи операндов: один операнд представлен в цифровой форме, второй операнд в аналоговой: 1) Xцм, Xам; 2) Nмсм; 3) Xцс, Xам; 4) Xцм, Xас; 5) Xц, Xа.

Вычисление младших частей результата.

Операция умножения аналоговой величины младшей части операнда Xа на цифровую величину младшей части операнда Xц реализуется по формуле:

Yмм = Xам • Xцм, (22)

где

Yмм - произведение младших частей;

Xам - младшая часть операнда Xа в аналоговой форме;

Xцм - младшая часть операнда Xц в цифровой форме.

При этом на управляющий вход реверсивного счетчика 1 подается сигнал начальной установки и цифровая входная величина 17 Xц первого сомножителя Xцм записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой и третьей схем выбора аналоговых операндов 6, 21 поступают сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 14 выбирается аналоговая величина второго сомножителя Xам и поступает на аналоговый вход ЦАП 5, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция умножения со сложением по формуле (1), ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (22) запоминается элементом 11.

Следующая операция выполняет умножение аналоговой величины произведения младших частей операнда Yмм на цифровую величину масштабного коэффициента операнда Nмсм по формуле:

Yмм1 = Nмсм • Yмм, (23)

где

Yмм1 - произведение младших частей с учетом масштабного коэффициента;

Yмм - произведение младших частей;

Nмсм - масштабный коэффициент в цифровой форме.

При этом на управляющий вход реверсивного счетчика 1 подается сигнал начальной установки и цифровая входная величина 17 Xц первого сомножителя Nмсм записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой и третьей схем выбора аналоговых операндов 6, 21 поступают сигналы с генератора синхроимпульсов 13, по которым с выхода первого элемента памяти 11 выбирается аналоговая величина второго сомножителя Yмм и поступает на аналоговый вход ЦАП 5, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция умножения со сложением по формуле (1), ключ 10 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (23) запоминается элементом 12.

Следующий шаг - умножение цифровой величины Xцс на аналоговую величину Xам со сложением с аналоговой величиной Yмм1 с получением результата в аналоговой форме реализуется по формуле:

Yм1 = Xцс • Xам + Yмм1. (24)

При этом цифровая входная величина 17 Xц первого сомножителя записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой и третьей схем выбора аналоговых операндов 6, 21 поступают сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 14 выбирается аналоговая величина второго сомножителя Xам, поступает на аналоговый вход ЦАП 5, на суммирующий вход ЦАП подается аналоговая величина Yмм1, запомненная ранее во втором элементе памяти 12, выполняется операция умножения со сложением по формуле (1), ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (24) запоминается элементом 11.

Следующий шаг - умножение цифровой величины Xцм на аналоговую величину Xас со сложением с аналоговой величиной Yм1 с получением результата в цифровой форме реализуется по формуле:

Yм = Xцм • Xас + Yм1. (25)

При этом цифровая входная величина 17 Xц первого сомножителя записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой и третьей схем выбора аналоговых операндов 6, 21 поступают сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 14 выбирается аналоговая величина второго сомножителя Xас, поступает на аналоговый вход ЦАП 5, на суммирующий вход ЦАП подается аналоговая величина Yм1, запомненная ранее в первом элементе памяти 11, выполняется операция умножения со сложением по формуле (1), ключ 10 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (25) запоминается элементом 12.

Затем на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп, через соответствующий аналоговый вход с элемента памяти 12 выбирается аналоговая величина результата, вычисленного по формуле (25), с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция деления с вычитанием по формуле (3) и результат формируется в счетчике 1. Группа разрядов результата вычисления младшей части произведения по формуле (18), сформированного в счетчике 1, начиная с n-s старшего разряда до первого младшего разряда, то есть без старших s разрядов, по сигналам с генератора синхроимпульсов 13, записывается в регистр 22.

Затем выполняется умножение исходных, не разделенных на части, операндов по формуле (19) с точностью вычисления известного устройства n-разрядов. На аналоговый вход X1 14 подается операнд Xа на цифровой вход Xц 17 подается цифровой операнд Xц, на управляющий вход реверсивного счетчика 1 подается сигнал начальной установки и цифровая входная величина 17 Xц первого сомножителя записывается в счетчик 1 через входы его начальной установки, на управляющие входы первой и третьей схем выбора аналоговых операндов 6, 21 поступают сигналы с генератора синхроимпульсов 13, по которым с первого аналогового входа X1 11 выбирается аналоговая величина второго сомножителя Xа, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция умножения со сложением по формуле (1), ключ 9 открывается сигналом, установленным генератором синхроимпульсов 13, и результат преобразования по формуле (19) запоминается элементом 11. Затем на управляющие входы первой, второй и третьей схем выбора аналоговых операндов 6, 7, 21 поступают сигналы с генератора синхроимпульсов 13, по которым со второго аналогового входа X2 15 выбирается напряжение Eоп, через соответствующий аналоговый вход с элемента памяти 11 выбирается аналоговая величина результата, вычисленного по формуле (19) Yп, с соответствующего аналогового входа третьей схемы выбора аналогового операнда 21 выбирается напряжение 0 В, выполняется операция деления с вычитанием по формуле (3) и результат формируется в счетчике 1.

Следующий шаг вычисления с повышенной точностью - коррекция не точно вычисленного по формуле (19) полного произведения Yп, хранящегося в счетчике 1, по значению k - контрольных разрядов суммы частичных произведений младших частей Yм, вычисленных ранее по формуле (18) и хранящихся в регистре 22. Контрольные разряды назначаются начиная со старших n-s до n-s-k и показаны на фиг. 2.

Старшие разряды полного произведения по формуле (18) вычисляются с точностью n разрядов. Погрешность в первом разряде при выполнении цифроаналоговых преобразований может распространиться в старшие разряды. Несмотря на удаленность значащих разрядов исходных операндов от ошибочных младших разрядов, блокирование "просачивания" ошибки в старшие разряды, выраженное в виде заема или переноса в старшие разряды (например: 0.01111111 + 1 => 0.10000000, 0.0100000 - 1 => 0.0011111) не выполняется. Такие ошибки присутствуют как в исходных операндах с расширенным диапазоном, так и в результате выполнения операции умножения на известном устройстве. То есть существует неоднозначность младшего значащего разряда даже после расширения диапазона.

Расширение динамического диапазона каждой части числа и вычисление произведений частей вместо произведений неразделенных операндов позволяет получать результаты с точностью выполнения операции умножения на известном устройстве с ошибкой ± 1 (и более) в младшем значащем разряде (первом разряде результата). Этот эффект мешает при вычислениях со старшими частями разделенных операндов, так как неоднозначность младшего разряда старшей части эквивалентна ошибке в разряде в середине полного сочлененного числа, а это очень грубые ошибки, перечеркивающие весь результат выполнения операции.

Для устранения погрешности в младших разрядах старшей части используется априорная информация о точном значении младших разрядов, сформированных при выполнении команды по формуле (19) в регистре 22 хранения младшей части результата вычисления с повышенной точностью. По сигналам с генератора синхроимпульсов 13 элемент И 3 закрывается и выбирается устройство сравнения двух чисел, представленных в дополнительном коде 26, последовательно g тактов с целью коррекции кодов неточно вычисленной старшей части на g квантов младшего разряда счетчика 1. Рекомендуемое значение g - 3 такта. Минимальное значение g - не менее 1 такта - для коррекции ошибок в одном младшем первом разряде Yп. В случае совпадения групп контрольных разрядов, подаваемых на входы A и B устройства сравнения двух чисел, представленных в дополнительном коде 26, коррекция считается выполненной и на дальнейших тактах работы схемы значение выхода счетчика 1 не изменяется.

В качестве эталона выбираются k старших разрядов. Расположение контрольных разрядов начинается с n-s-го разряда и заканчивается n-s-k-ым. Группа k контрольных разрядов Qа с выхода регистра 22 подается на вторую группу входов операнда B устройства сравнения двух чисел, представленных в дополнительном коде 26 - k-разрядных чисел в дополнительном коде, на первую группу входов операнда A устройства сравнения двух чисел, представленных в дополнительном коде 26, с выхода счетчика 1 подается группа от k-го до первого корректируемого разряда. В результате сравнения k контрольных разрядов, представленных в дополнительном коде, поданных на первый и второй входы A и B устройства сравнения двух чисел, представленных в дополнительном коде 26, вырабатывается сигнал либо на первом выходе устройства сравнения двух чисел, представленных в дополнительном коде 26, устанавливающийся в единицу при условии A<B, то есть двоичный код, установленный на первой группе входов (входы A) устройства сравнения двух чисел, представленных в дополнительном коде 26, меньше значения кода, установленного на второй группе входов (входы B) этого устройства, который подается через элемент ИЛИ 24 на инкрементирующий вход счетчика 1, и выполняется увеличение кода счетчика на один квант, либо на втором выходе устройства сравнения двух чисел, представленных в дополнительном коде 26, устанавливающийся в единицу при условии A>B, то есть двоичный код на группе входов A устройства сравнения двух чисел, представленных в дополнительном коде 26, больше значения кода, установленного на группе входов B этого устройства, который подается через элемент ИЛИ 25 на декрементирующий вход счетчика 1, и выполняется уменьшение кода счетчика на один квант.

Коды контрольных разрядов интерпретируются как числа, представленные в дополнительном коде: старший k-й разряд интерпретируется как знак числа, 0 - положительное число, 1 - отрицательное с распространением единиц вправо (дополнительный код). По окончании коррекции на выходе счетчика 1 сформированы n старших разрядов результата выполнения операции умножения с повышенной точностью, которые установлены на цифровых выходах 20 устройства. Группа n-s-k разрядов Qб с выхода регистра 22 соответствует разрядам результата вычисления с повышенной точностью, начиная с n+1-го и заканчивая n+(n-s-k+1)= 2n-s-k+1-ым разрядом, по сигналам с генератора синхроимпульсов 13 подается на вторую группу цифровых выходов 28 устройства.

Сравнение рассмотренного устройства с прототипом, точность вычисления которого n разрядов и функциональные возможности ограничены операциями умножения, деления и возведения в квадрат с различными сочетаниями форм представления входных операндов и результата, показывает, что схемное построение рассмотренного устройства путем введения действий сложения и вычитания за счет подключения требуемых операндов к суммирующей точке преобразователя код-напряжение обеспечивает: расширение функциональных возможностей, состоящее в том, что в дополнение ко всем реализованным в известном устройстве операциям вводятся тернарные операции умножения со сложением и деления с вычитанием с представлением результата как в аналоговой, так и в цифровой форме, и операция умножения с повышенной точностью; достигается увеличение точности вычисления операции умножения до 2n-s-k разрядов. При этом для выполнения новых операций сложения и вычитания в устройстве используются те же блоки, что и для операций умножения и деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| МЕТАЛЛОПОРИСТЫЙ КАТОД И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1995 |

|

RU2087983C1 |

| СПОСОБ И СОСТАВ ДЛЯ БОРОХРОМИРОВАНИЯ СТАЛЬНЫХ ИЗДЕЛИЙ В ПСЕВДООЖИЖЕННОМ СЛОЕ | 1996 |

|

RU2157859C2 |

| Цифровой фильтр | 1984 |

|

SU1205152A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1983 |

|

SU1120347A1 |

| СПОСОБ БОРОНИКЕЛИРОВАНИЯ СТАЛЬНЫХ ИЗДЕЛИЙ В ПСЕВДООЖИЖЕННОМ СЛОЕ | 1995 |

|

RU2149917C1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА | 1991 |

|

RU2006917C1 |

Изобретение относится к вычислительной технике и предназначено для использования в системах обработки и преобразования информации. Технический результат заключается в расширении области применения устройства за счет расширения функциональных возможностей через реализацию операций умножения со сложением и вычитания с делением и увеличения точности вычисления операций умножения. Технический результат достигается за счет того, что устройство содержит в своем составе реверсивный счетчик, переключатель, элемент И, тактовый генератор, три схемы выбора аналогового операнда, компаратор, два ключа, два элемента памяти, генератор синхроимпульсов, регистр, масштабный резистор, два элемента ИЛИ, устройство сравнения двух цифровых величин, цифровые входы, четыре аналоговых входа, два аналоговых выхода, две группы цифровых выходов, цифроаналоговый преобразователь, содержащий кодоуправляемый делитель напряжения, второй масштабный резистор и операционный усилитель. 2 ил.

Аналого-цифровое вычислительное устройство, содержащее реверсивный счетчик, переключатель, элемент И, тактовый генератор, цифроаналоговый преобразователь, две схемы выбора аналогового операнда, компаратор, два ключа, два элемента памяти, генератор синхроимпульсов, три аналоговых входа, цифровые входы, два аналоговых выхода, цифровые выходы, причем вход переключателя соединен с выходом элемента И, первый вход элемента И соединен с выходом тактового генератора, а второй вход элемента И, управляющий вход реверсивного счетчика, цифровые управляющие входы первого и второго ключей, первый и второй управляющие входы первой и второй схем выбора аналогового операнда соединены с соответствующими выходами генератора синхроимпульсов, управляющий вход переключателя соединен с выходом компаратора, цифровые входы соединены с цифровыми установочными входами реверсивного счетчика, выходы реверсивного счетчика соединены с соответствующими входами цифроаналогового преобразователя и с соответствующими цифровыми выходами устройства, аналоговый вход цифроаналогового преобразователя через третий аналоговый вход первой схемы выбора аналогового операнда соединен с первым аналоговым входом устройства и через четвертый аналоговый вход первой схемы выбора аналогового операнда соединен с вторым аналоговым входом устройства, аналоговый выход первого ключа соединен с входом первого элемента памяти, выход которого соединен с первым аналоговым выходом устройства и с первыми аналоговыми входами первой и второй схем выбора аналогового операнда, аналоговый выход второго ключа соединен с входом второго элемента памяти, выход которого соединен с вторым аналоговым выходом устройства, выход цифроаналогового преобразователя соединен с аналоговыми входами первого и второго ключей и с инвертирующим входом компаратора, третий аналоговый вход соединен с третьим входом второй схемы выбора аналогового операнда, выход которой соединен с неинвертирующим входом компаратора, отличающееся тем, что в устройство дополнительно введены третья схема выбора аналогового операнда, регистр, первый масштабный резистор, два элемента ИЛИ, устройство сравнения двух чисел, представленных в дополнительном коде, четвертый аналоговый вход, вторая группа цифровых выходов устройства, а цифроаналоговый преобразователь содержит кодоуправляемый делитель напряжения, второй масштабный резистор, операционный усилитель, выход которого является выходом цифроаналогового преобразователя и соединен через второй масштабный резистор с инвертирующим входом операционного усилителя и с выходом кодоуправляемого делителя напряжения, аналоговый и управляющий входы которого являются соответственно аналоговым и цифровым входами цифроаналогового преобразователя, причем инвертирующий вход операционного усилителя подключен через первый масштабный резистор, через соответствующий вход третьей схемы выбора аналогового операнда к четвертому аналоговому входу устройства, выход первого элемента памяти соединен с соответствующим аналоговым входом третьего устройства выбора аналогового операнда, выход второго элемента памяти соединен с соответствующими аналоговыми входами первого, второго и третьего устройств выбора аналогового операнда, соответствующий аналоговый вход третьей схемы выбора аналогового операнда соединен с шиной нулевого потенциала, первый выход переключателя соединен с первым входом первого элемента ИЛИ, выход которого соединен с инкрементирующим входом реверсивного счетчика, второй выход переключателя соединен с первым входом второго элемента ИЛИ, выход которого соединен с декрементирующим входом реверсивного счетчика, первая группа цифровых выходов реверсивного счетчика соединена с первой группой цифровых входов устройства сравнения двух чисел, представленных в дополнительном коде, вторая группа цифровых выходов реверсивного счетчика соединена с цифровыми входами регистра, первый и второй управляющие входы третьей схемы выбора аналогового операнда, управляющие входы регистра и устройства сравнения двух чисел, представленных в дополнительном коде, соединены с соответствующими выходами генератора синхроимпульсов, первая группа цифровых выходов регистра соединена с второй группой цифровых входов устройства сравнения двух чисел, представленных в дополнительном коде, вторая группа цифровых выходов регистра соединена с второй группой цифровых выходов устройства, первый выход устройства сравнения двух чисел, представленных в дополнительном коде, устанавливающийся в единицу при условии, что двоичный код, установленный на первом входе устройства сравнения двух чисел, представленных в дополнительном коде, меньше значения кода, установленного на втором входе этого устройства, соединен с вторым входом первого элемента ИЛИ, второй выход устройства сравнения двух чисел, представленных в дополнительном коде, устанавливающийся в единицу при условии, что двоичный код, установленный на первой группе входов устройства сравнения двух чисел, представленных в дополнительном коде, больше значения кода, установленного на второй группе входов этого устройства, соединен с вторым входом второго элемента ИЛИ.

| Множительно-делительное устройство | 1976 |

|

SU674042A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| US 4893267 A, 09.01.90 | |||

| US 4722068 A, 26.06.88. | |||

Авторы

Даты

1998-12-20—Публикация

1997-10-23—Подача