1

Изобретение относится к области вычислительной техники и может быть использовано в полиоточных ЗУ, элемент памяти которых состоит из 3-4 феррнтовых сердечников, объединенных витком связи.

Известен способ заннси информацнн в полноточных ЗУ, основанный на неремагничнвании компенсирующих сердечников в процессе записи.

Иедостатками известного способа записи являются малое быстродействие и сравнительно большая нотребляемая мощность,

Целью изобретения является повыщение быстродействия и уменьшение потребляемой мош.иости при записи информации в полноточных ЗУ.

Поставленная цель достигается за счет того, что перемагничивают постоянным током селектирующие сердечники в состояние «1, а компенсирующие сердечники - в состояние «О, подают ток записи в селектирующие сердечники одновременно во все разряды числа и нри записи «О подают поразрядно управляющие токи в компенсирующие сердечники соответствующих разрядов всех чисел.

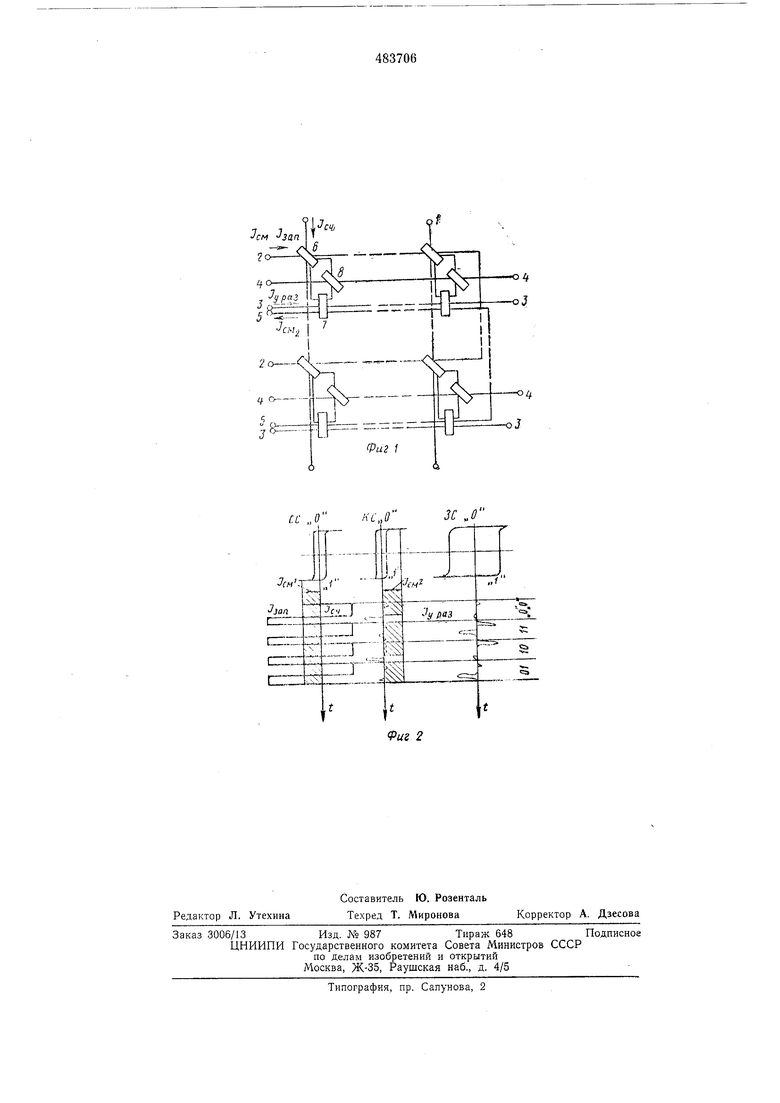

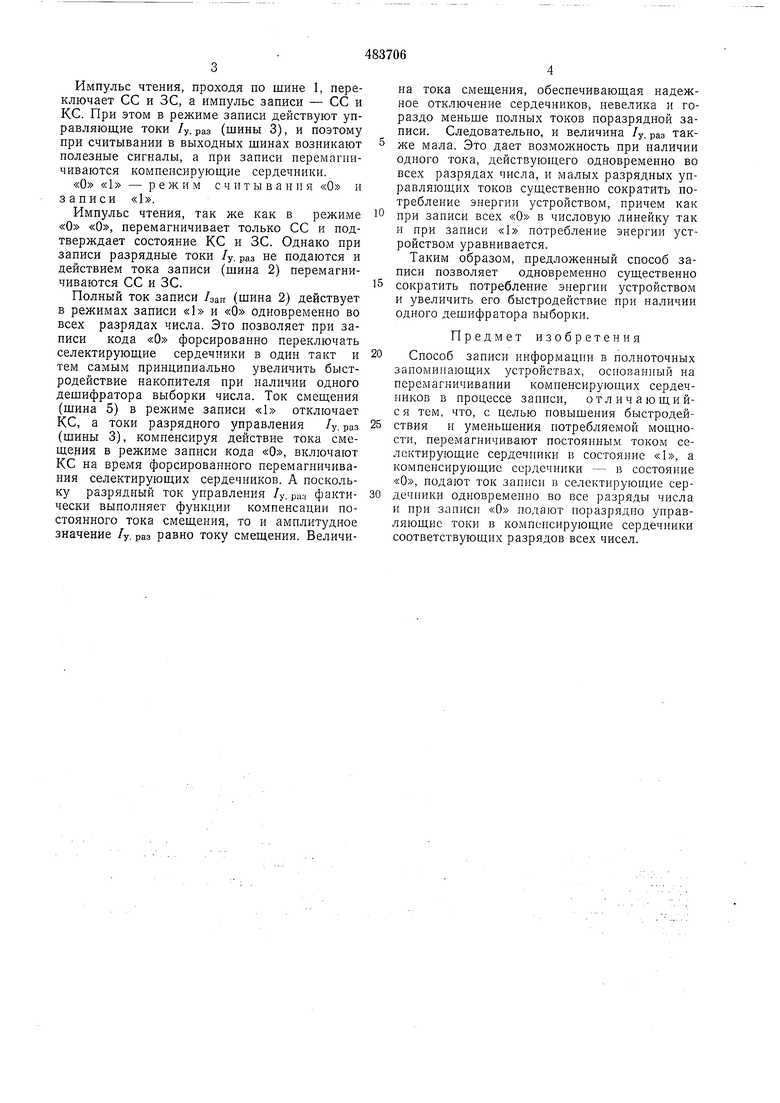

На фиг. 1 изображено ЗУ, реализующее способ; на фиг. 2 - импульсная диаграмма работы ЗУ.

На фиг. 1 и 2 приняты следующие обозначения: щины чтения 1, щины смещения и записи 2, разрядные управляющие шины - 3, выходные щины 4, щины смещения - 5, селектирующие сердечники (СС) 6, компенсирующие сердечники (КС) 7 и запоминающие сердечники (ЗС) - 8.

Запись информации в ЗУ происходит следующим образом.

«О «О - режим

считывания «О и записи «О.

Импульс чтения

проходя но шине 1, перемагничнвает СС и подтверждает состояние КС и ЗС. Импульс записи (щина 2) /зап форсированно переключает СС и КС, так как в последних при записи ток смещения /см. постоянно действующий в щине 5, компенсируется разрядными управляющими токами /у. раз (щина 3). На импульсной диаграмме (фиг. 2) на оси ЗС показаны сигналы помех, а на оси КС - сигнал перемагничивания в режиме записи.

«1 «1 - режим считывания «1 и записи «1.

Импульс чтения (щина 1) перемагничивает СС и ЗС, подтверждая состояния КС. Импульс записи (щина 2) возвращает в исходные состояния ЗС и СС.

«1 «О - режим считывания и записи «О.

Импульс чтения, проходя по шине 1, переключает СС и ЗС, а импульс записи - СС и КС. При этом в режиме записи действуют управляющие токи /у. раз (шины 3), И ПОЭТОМу

при считывании в выходных шинах возникают полезные сигналы, а при записи перемагпичиваются компенсируюш.ие сердечники.

«О «1 - режим считывания «О и записи «1.

Импульс чтения, так же как в режиме «О «О, перемагничивает только СС и подтверждает состояние КС и ЗС. Однако при записи разрядные токи /у. раз не подаются и действием тока записи (шина 2) перемагничиваются СС и ЗС.

Полный ток записи /зап (шина 2) действует в режимах записи «1 и «О одновременно во всех разрядах числа. Это позволяет при записи кода «О форсированно переключать селектирующие сердечники в один такт и тем самым принципиально увеличить быстродействие накопителя при наличии одного дешифратора выборки числа. Ток смещения (шина 5) в режиме записи «1 отключает КС, а токи разрядного управления /у. раз (шины 3), компенсируя действие тока смещения в режиме записи кода «О, включают КС на время форсированного перемагничивания селектирующих сердечников. А поскольку разрядный ток управления /у. раз фактически выполняет функции компенсации постоянного тока смещения, то и амплитудное значение /у. раз равно току смещения. Величина тока смещения, обеспечивающая надежное отключение сердечников, невелика и гораздо меньше полных токов поразрядной записи. Следовательно, и величина /у. раз также мала. Это дает возможность при наличии одного тока, действующего одновременно во всех разрядах числа, и малых разрядных управляющих токов существенно сократить потребление энергии устройством, причем как

при записи всех «О в числовую линейку так и при записи «1 потребление энергии устройством уравнивается.

Таким образом, предложенный способ записи позволяет одновременно существенно

сократить потребление энергии устройством и увеличить его быстродействие при наличии одного дешифратора выборки.

Предмет изобретения

Способ записи информации в полноточных запоминающих устройствах, основанный на перемагничивании компенсирующих сердечников в процессе записи, отличающийся тем, что, с целью повышения быстродействия и уменьщения потребляемой мощности, перемагничивают постоянным током селектирующие сердечники в состояние «1, а компенсирующие сердечники - в состояние «О, подают ток записи в селектируюп1ие сердечники одновременно во все разряды числа и при записи «О подают поразрядно управляющие токи в компенсирующие сердечники соответствующих разрядов всех чисел.

-04

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| Магнитный запоминающий элемент | 1977 |

|

SU739649A1 |

| Запоминающее устройство | 1973 |

|

SU446107A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОс-:;?:ооюснАЯг.шн'но-ТЕх;1:г^Е идяЕИБЛИО-ГКА | 1970 |

|

SU276166A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1969 |

|

SU249059A1 |

| Оперативное запоминающее устройство | 1954 |

|

SU126660A1 |

| ФЕРРИТОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЛИНЕЙНОЙ | 1973 |

|

SU377876A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU388299A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386442A1 |

Г.С

ЗС J

Авторы

Даты

1975-09-05—Публикация

1973-04-11—Подача