Предлагаемое устройство относится к области вычислительной техники и может быть использовано в универсальных и специализированных вычислительных системах, содержащих магнитное запоминающее устройство на ферритовых парах с петлей связи между селектирующим и информационным сердечниками.

Цифровые логические устройства на магнитном накопителе известны. В этих устройствах применяются для логических преобразований магнитные накопители различных типов, так или иначе использующие при записи информации на сердечнике факт совпадения двух или больщего числа импульсов тока, подаваемых по различным шинам. Этим обстоятельством обусловливается ограниченный коэффициент селекции накопителя, а следовательно, и всего логического устройства. Ограничение коэффициента селекции, н свою очередь, обусловливает относительно узкий диапазон допустимых изменений параметров элементов накопителя, параметров импульсов записи и температуры окружающей среды.

Цель изобретения заключается в повышении коэффициента селекции при выполнении логических операций и в расширении допусков на параметры элементов и импульсов, а также допусков на температуру окружающей среды. Эта цель достигается благодаря применению

в цифровом логическом устройстве полноточного накопителя на ферритовых парах с петлей связи между селектирующим и информационным сердечниками.

Отличие устройства заключается в использовании магнитного оперативного запоминающего устройства (МОЗУ) на ферритовых парах с элементами и связями, позволяющими выполнять логические операции конъюнкции,

дизъюнкции, инверсии в одном или нескольких адресах запоминающего устройства при записи информации. Нововведенные связи и элементы позволяют выполнять логические операции при воздействии в момент записи на

информационный сердечник одного полного тока. МОЗУ строптся по системе с линейной выборкой. К адресной щине, проходящей через селектирующие сердечники одного адреса, подсоединяется нереверсивный формирователь;

к адресной шине, проходящей через информационные сердечники одного адреса, также подсоединяется нереверсивный формирователь.

Формирователи, подсоедпненпые к адресным щинам, могут возбул даться в произвольном

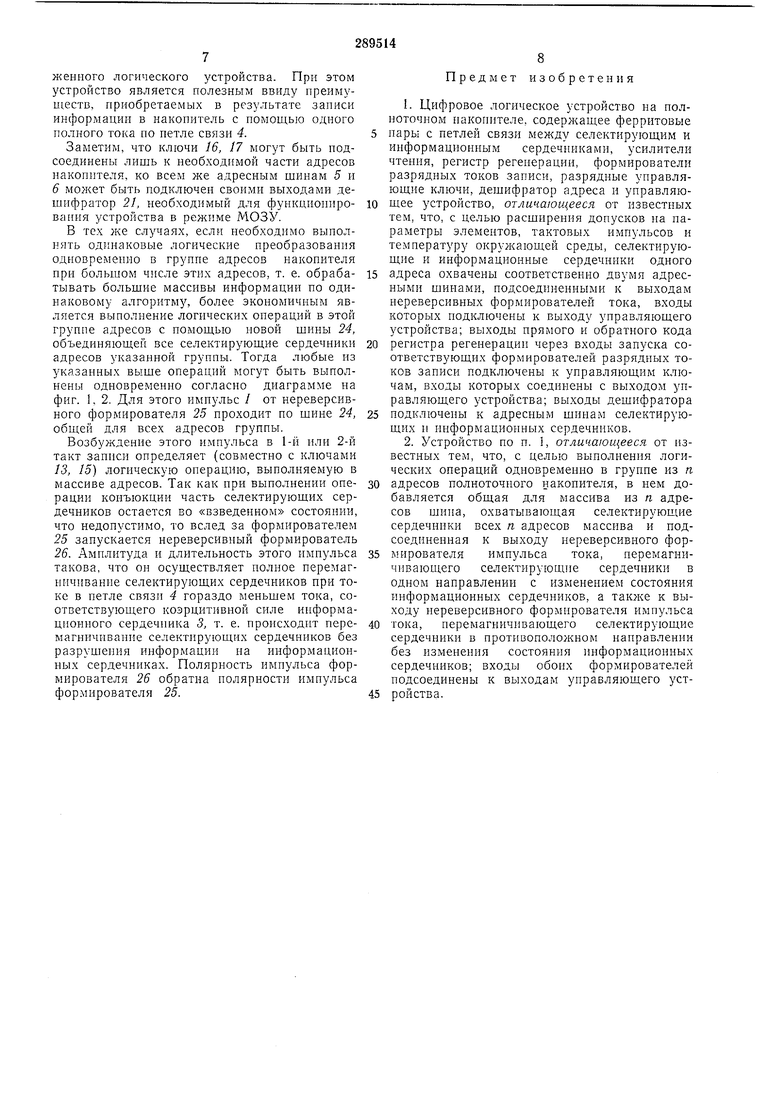

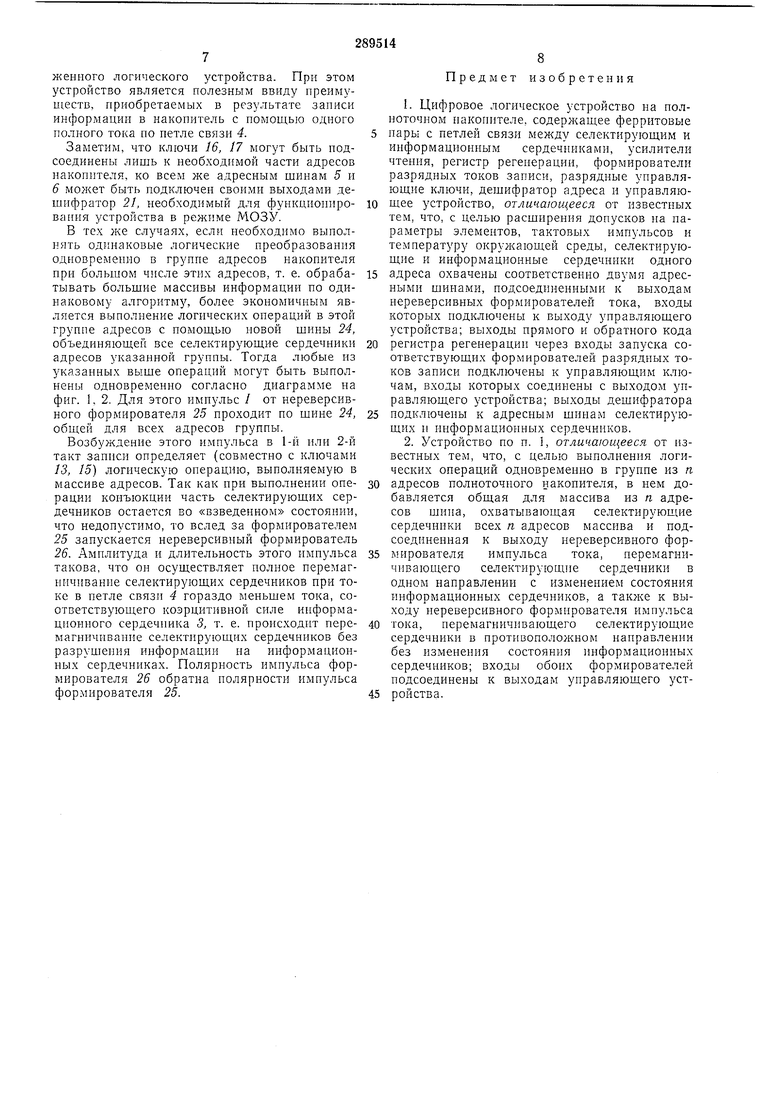

сочетан 1п импульсами, подаваемыми на пх входы из управляющего устройства. Выполнеппе той или иной логической операции в любом адресе определяется моментом возбуждения адресных формпрователей относительно рядных шинах записи, объединяющих селектирующие сердечники одного разряда всех адресов. Регистр регенерации устройства имеет выход ирямого и обратного значения записываемого кода. Выходы прямого значения кода через управляющий ключ подсоединяются ко входам формирователей разрядных токов записи, выходы обратпого значения кода также через свой управляющий ключ подсоединяются ко входам тех же формирователеГк Открытие того или иного управляющего разрядного ключа определяется и.миульсами на их входах, подсоединенных к выходам уиравляющего устройства. Различные сочетания возбуждения адресных формирователей и унравляющпх ключей и определяют выполняемую логпческую операцию в одном или нескольких адресах накопителя. При этом операции, выиолненные в разных адресах, могут быть различными. При выполнении логической операции одновременно над массивом слов с большим числом адресов, с целью экономии адресных формирователей, вводится общая адресная шииа, проходящая через селектирующие сердечники всех адресов массива. К нововведенной общей шине подсоединяется выход формирователя импульса, перемагничивающего селектирующие сердечники с разрушением информации; к этой же шине подсоединяется выход формирователя импульса, перемагничивающего селектирующие сердечники без разрущения информации. Ьоз&уждение формирователей общей адресной шины в различные моменты времени определяет выполняемую логическую операцию над всеми словами одного или нескольких массивов одновременно. На фиг. 1, а представлен один адрес полноточного МОЗУ на ферритовых парах; на фиг. 1, б, в, г приводятся временные диаграммы работы адреса в режиме считывания с регенерацией и выполнения логических функций; на фиг. 2 приведено предложенное цифровое логическое устройство на полноточном МОЗУ. Адрес / нолноточного МОЗУ (накопителя) предполагает линейную организацию выборки и содержит количество ферритовых пар но числу разрядов. Каждая пара состоит из селектирующего сердечника 2 и информационного сердечника 3, соединенных между собой петлей связи 4. Через все селектирующие сердечники 2 одного адреса проходит адресная шина 5, а через информационные сердечники - адресная шина 6. Через селектирующие сердечники 2 проходит разрядная шина записи 7, а через информационные сердечники - разрядная шина чтения 8. Шины 7 и 5 объединяют, соответственно, селектирующие и информационные сердечники одного разряда всех адресов накопителя. Разрядные шины чтения 8 подсоединяются ко входам усилителей чтения 9 (см. фиг. 2), выход каждого усилителя чтения подсоединен ко входу триггера 10 регистра регенерации; выходы П прямого значеИЯ кода регистра регенерации через входы азрядных формирователей записи 12 постуают па вход разрядного управляющего ключа 13; выходы 14 обратпого значения кода регистра регенерации через входы разрядных формирователей записи 12 поступают на вход разрядного управляющего ключа 15. Выходы разрядных формирователей записи 12 подсоединяются к разрядным шинам запиСП 7 накопителя. Шины 7 и 5 накопителя на фиг. 2 показаны лишь в одном адресе; через все остальные адреса накопителя шины 7 и 5 проходят аналогично, последовательпо объединяя селектирующие и информационные сердечппкп одного разряда всех адресов. К адресной шипе 5 подсоединяется выход нереверсивпого адреспого формирователя 16, к адресной шине 6 подсоединяется выход нереверсивного адресного формирователя П. Вход формирователя 16 подсоединен к выходу 18 управляющего устройства 19; вход формирователя П подсоединен к выходу 20 управляющего устройства 19. Помимо выходов адресных формирователей 16 и П адресные шины 5 и 5 накопителя подсоединяются к выходам дешифратора адреса 21. Заиускающий вход управляющего ключа 13 подсоединен к выходу 22 управляющего устройства /5; запускающий вход ключа 15 - к выходу 23 унравляющего устройства 19. Шина 24 проходит через селектирующие сердечники группы адресов накопителя и подсоединяется к выходам нереверсивных формирователей 25 и 26. Входы формирователей 25 и 26 подсоединены соответственно к выходам 27 и 28 управляющего устройства 19. Для пояснения работы предложенного цифрового логического устройства рассматриваются способы выполнения логических функций непосредственно в адресе нолноточного магнитного накопителя, представленного на фиг. I, а. Реализация способов выполнения логических функций в накопителе требует введения новых элементов и связей, совокупность которых и определяет новизну предложенного логического устройства. На фиг. 1, б и В показаны временные диаграммы адресных и разрядных токов в режиме считывания и регенерации МОЗУ на ферритовых парах. При этом возмолсно выполнение логических операций в адресах накопителя. Диаграмма на фиг. 1, б предполагает использование двух нереверсивных дешифраторов, с числом выходов, равным числу адресов накопителя. Выходы одного дешифратора подсоединены к адресным шинам 5 через селектирующие сердечники; выходы другого к адресным щинам 6 через информационные сердечники. Импульс тока /с направляется в такт считывания в щину 5 выбранного адреса, при этом происходит перемагничивание се лектирующих сердечников 2 и по петле связи информационных сердечников 5. Сигнал с разрядных шин 8 поступает на усилители чтения.

Регенерация или запись информации г. г:ыбранный адрес осуществляется за два такта: 1-й и 2-й. В 1-й такт записи по разрядным шинам 7 поступает обратный код записываемого числа; в соответствующих разрядах выбранного адреса происходит перемагничивание селектирующих сердечников, при этом информационные сердечники не перемагничиваются ввиду их импульсного смещения током /и по шине 6 от второго дешифратора. Во 2-й такт записи по шинам 7 поступает прямой код записываемого числа, перемагничивая оставшиеся селектируюшие сердечники и по петле связи - информационные, записывая в них единицы.

Диаграмма на фиг. 1. b предполаг- ет использование одного нереверсивного дешифрятора с числом выходов равным числу При этом шины 5 V. 6 соединяются последовательно и подсоединяются к выходам дешифратора. Импульс /с и /и в этом случае один и тот же. Длительность его такова, что он практически перекрывает весь 1-й такт записи. Импульс /р по разрядным шинам 7 в 1-й такт записи превосходит /с и /и, так что селектируюшие сердечники перемагничиваются в соответствии с обратным кодом записываемого числа. Информационные сердечники при этом находятся под воздействием импульсного смещения (/с, /в) и не перемагничиваются. Во 2-й такт записи импульсами /р прямого кода записываемого числа перемагничиваются оставшиеся селектирующие сердечники 2 и по петле связи 4 - информационные сердечники 3. В них оказывается записанной едииица.

Поступление импульсов обратного и прямого кода в 1-й и 2-й такты записи обеспечивается связями 11 и 14, коммутируемым управляющими разрядными ключами 13 и 15. Открытие ключей 13 и 15 определяется сигиалами от уиравляющего устройства 19 по связям 22 или 23. При открытии ключа 13 на разрядные шины 7 поступает прямой код числа, при открытии ключа 15 - обратный код числа.

В предложенном устройстве возможно выполнение операций инверсии, дизъюнкции («ИЛИ) и конъюнкции («И) в одном или нескольких адресах. Выполненне всех операций происходит в 1-ом и 2-ом тактах записи. Способы выполнения этих операций одинаковы для случая фиг. I, б и I, Ь.

Операция инверсии осуществляется за счет изменения порядка следования обратного и прямого кода записи в 1-ом и 2-ом тактах записи. Если в 1-й такт записи открывать ключ 13, а во 2-й такт записи - ключ 15, то в выбранной ячейке окажется записанным обратный код считанного числа. В случае, если это записываемое число является аргументом для выполнения операций «И, «ИЛИ, то операции будут производится над обратным кодом считанного из определенного адреса

числа.

рительно считанным с другого адреса. При этом ячейки, в которых производится оиерация «ИЛИ, в такт считывания не опрашиваются. Выиолиение этой операции показано на фиг. 1. г. В 1-й такт записи в адресные шины 5 нужных адресов подается импульс /с. Этот импульс по длительности и амплитуде перекрывается импульсом /р на шинах 7. В случае, если в даииом разряде в 1-ом такте записи на шине 7 отсутствует импульс /р, то импульс /с перемагничивает селектирующий сердечник и по петле связи информационный сердечник (последиес не обязательно). Если /р гписутствует в 1-олг такте записи, то селекти люпаи сердечиик ие перемагничнвается, будучи смещен этим нмп -льсом Во 2-ом такте пси в обпятн-М на1раклен1Н1 по крутому астку гямоугольной петли гистерезиса перем гничиваться те сердечники, которые в 1-ом такте перемагнитились током /с, загисывая ри этом на информационные сердечники единицы. Таким образом, на информационных сердечниках окажется записанной информация, соответствующая аД/й, если в 1-ом такте записи был открыт ключ 15, а во 2-ом такте записи - ключ 13: или - cii / Ь, если в 1-ом такте записи открыт ключ 13, а во 2-ом - ключ 15.

Операция «И также может быть выполиена в адресе накопителя согласно фнг. 1, г. Для этого импульс /с по шпне 5 подается во 2-й такт записи. Те ииформационные сердечники данного адреса, в разрядах которых отсутствует ток /р, во 2-й такт записи оказываются установленными в состояние 0. Таким образом, после 2-го такта записи на информационных сердечниках оказывается записанной ииформация, соответствующая а.{ Д 6;, если во 2-ом такте записи открыт ключ 13, или а Д bi, если во 2-ом такте записи открыт ключ 15. Заметим, однако, что при этом часть селектирующих сердечников данного адреса остается во «взведенном состоянии. Поэтому в очередной цикл обращення следует нровести обычное считывание и регенерацию данного адреса. Тогда (или ) окажется вновь записанным на его информационные сердечники, а кроме того, поступая по разрядным шинам 7 в 1-й и 2-й такты записи, может быть использовано как аргумент при выполнении очередных логических преобразований.

Заметим, что во всех рассмотреиных способах сохранен принцип полноточности ири записи информации в адрес накопителя. Индивидуальный выбор адресов, в которых производятся логические онерации в произвольном их сочетании, производится нереверсивными ключами 16 и 17, подсоединенными отдельно к шинам 5 т 6 адреса накопителя. Эти соединения совместно со связями 11, 14, ключами 13, 15 обеспечивают возможность выполнения функционально полного набора логических операций в одном или группе адресов нредложениого логического устройства. При этом устройство является полезным ввиду преимуществ, приобретаемых в результате записи информации в накопитель с помощью одного полного тока по нетле связи 4.

Заметим, что ключи 16, 17 могут быть подсоединены лишь к необходимой части адресов накопителя, ко всем же адресным шинам 5 и 6 может быть подключен своими выходами дешифратор 21, необходимый для функционировамня устройства в МОЗУ.

В тех же случаях, если необходимо выполнять одинаковые логические нреобразования одновременно в группе адресов накопителя при большом числе этих адресов, т. е. обрабатывать большие массивы информации по одинаковому алгоритм , более экономичным является выполнение логических операций в этой группе адресов с помошью новой шины 24, объединяющей все селектирующие сердечники адресов указанной группы. Тогда любые из указанных выше операций могут быть выполнены одновременно согласно диаграмме на фиг. 1, 2. Для этого импульс / от нереверсивного формирователя 25 нроходит по шине 24, общей для всех адресов группы.

Возбуждение этого импульса в 1-й или 2-й такт записи определяет (совместно с ключами 13, 15) логическую операцию, выполняемую в массиве адресов. Так как при выполнении операции конъюкции часть селектирующих сердечников остается во «взведенном состоянии, что недопустимо, то вслед за формирователем 25 запускается нереверсивный формирователь 26. Амплитуда и длительность этого импульса такова, что он осуществляет полное перемагничиванне селектирующих сердечников при токе в петле связи 4 гораздо меньшем тока, соответствующего коэрцитивной силе информационного сердечника 5 т. е. происходит перемагничиванне селектирующих сердечников без разрушения информации иа информационных сердечниках. Полярность импульса формирователя 26 обратна полярности импульса формирователя 25.

Предмет изобретения

1.Цифровое логическое устройство на полноточном накопителе, содержащее ферритовые

пары с петлей связи между селектирующим и информационным сердечниками, усилители чтения, регистр регенерации, формирователи разрядных токов записи, разрядные управляющие ключи, дешифратор адреса и управляющее устройство, отличающееся от известных тем, что, с целью расширения допусков на параметры элементов, тактовых импульсов и температуру окружающей среды, селектирующие и информационные сердечники одного

адреса охвачены соответственно двумя адресными щинами, подсоединенными к выходам нереверсивных формирователей тока, входы которых подключены к выходу управляющего устройства; выходы прямого и обратного кода

регистра регенерации через входы запуска соответствующих формирователей разрядных токов записи подключены к управляющим ключам, входы которых соединены с выходом управляющего устройства; выходы дешифратора

подключены к адресным шинам селектирующих и информационных сердечников.

2.Устройство по п. 1, отличающееся от известных тем, что, с целью выполнения логических операций одновременно в группе из п

адресов нолноточного накопителя, в нем добавляется общая для массива из п адресов шина, охватывающая селектирующие сердечники всех п адресов массива и нодсоеднненная к выходу нереверсивного формирователя импульса тока, перемагничивающего селектирующие сердечники в одном направлении с изменением состояния информационных сердечников, а также к выходу нереверсивного формирователя импульса

тока, перемагничивающего селектирующие сердечники в противоположном направлении без изменения состояния информационных сердечников; входы обоих формирователей подсоединены к выходам управляющего устройства.

Q

-i-/

Thi LiJl

u

-,- -h-L, I.-.J

:n.:j:imj

I A I A I M 1 1 I

I 1 6

так1п 2 fпан т (. janucu записи

c Г 1 Зо:шси jiiiucu

..HZ

, L.l--t f

и pIf, (01

,, .№-

а.

i --

f/j,

„„.D,

Vua. I

-t -t

Фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОСЙ1Ч '^ | 1972 |

|

SU436389A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU277852A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| ЬИЬЛИО', ЕКА | 1973 |

|

SU365707A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

Авторы

Даты

1971-01-01—Публикация