Изобретение относится к обларгги хелемехаинки II предназначено для нередачи ииформацни от удаленных контролируемых объектов на riyi.-KT сбора информацией.

Известно многоканальное телеснгнализанионпое устройство с временным раздслепиом каналов.

Недостатком этого устройства является нер.ысокая скорость передачи инфор.маини от контролируемого объекта на пункт сбора нн(j)OpMauHH (в среднем велнчнна времени, необходнмого для нередачи ииформанин, составляет ноловииу нериода опроса всех входящих в состав устройства нерифернр1ных унлотннтельных устройств).

Другим недостатком этого устройства является малый об7зем информацнн, выводимой Tia выход устройства (индинируется только иомер нернферийного устройства, в которбм воз1Н1кла аварийная снтуаиня, но отсутствует класснфикания возможных аварнйиых ситуаций) .

Еще одним недостатком этого устройства является большое количество избыточиой информации, вывод мой на выход устройства (вывод информации от аварийной снтуации нродолжается вплоть до ее устранення).

Целью нзобретення является новышенне скорости передачи информацнн от контролируемых обт ектов на пункт сбора инфюрмацнн.

Указанная цель достнгается тем, что п нрнемное устройство введены блок обратного числового преобразования, блок логической обработки, блок памяти, блок местного унровления, амплитудный днскримннатор. диппкрр;;тор нулевого кода н вентили, причем нервын вход блока чнс.ювого преобр;13овання под ключен ко входу амплнтудного днскрнмииатора и через mecToii вентиль --- к нсрвому в.чоду второго регистра, к которому подключен выход блока чнслового нреобразования через седьмой вер тиль; ко второму входу второго регистра подключен выход расиределите.чя и второй вход блока чнслового преобразования.

нервый н второй входы дешнфратора нулевого кода подключеьн т соответственно второму выходу второго регистра н второму входу блока соиряжения, а выход - к соотьетствуюн1ему входу блока управления; нервьн вы

ход второго регистра через восьмой вен гиль соединен с третьнм входом б.юка сонря.женпм; выход блока обратного чнслового нреобрл.зоваиня подключен через девятый вентиль к первому входу первого регистра, с нервым

выходом которого соедннен нервый вход блока обратного числового преобразования, второй вход которого соединен со вторым входом первого регнстра; выход амплитудного дискр1 лииатора гюдключен к первым входам

блока намяти и блока логической обработки.

второй вход которого соединен с первым выходом блока памяти, а выходы - с соответствующими входами блока управления, один из сигнальных выходов которого соединен со вторым входом блока памяти, третий вход которого соединен со вторым выходол иервого регистра, четвертый - с выходом блока местного управления, ко входам которого соответствепио подключены выходы генератора тактовых импульсов и формирователя синфазирующих импульсов; соответствующие выходы блока управления подключены ко вторым входам шестого, седьмого, восьмого и девятого вентиля, а сигнальные выходы - к блоку оконечного преобразования.

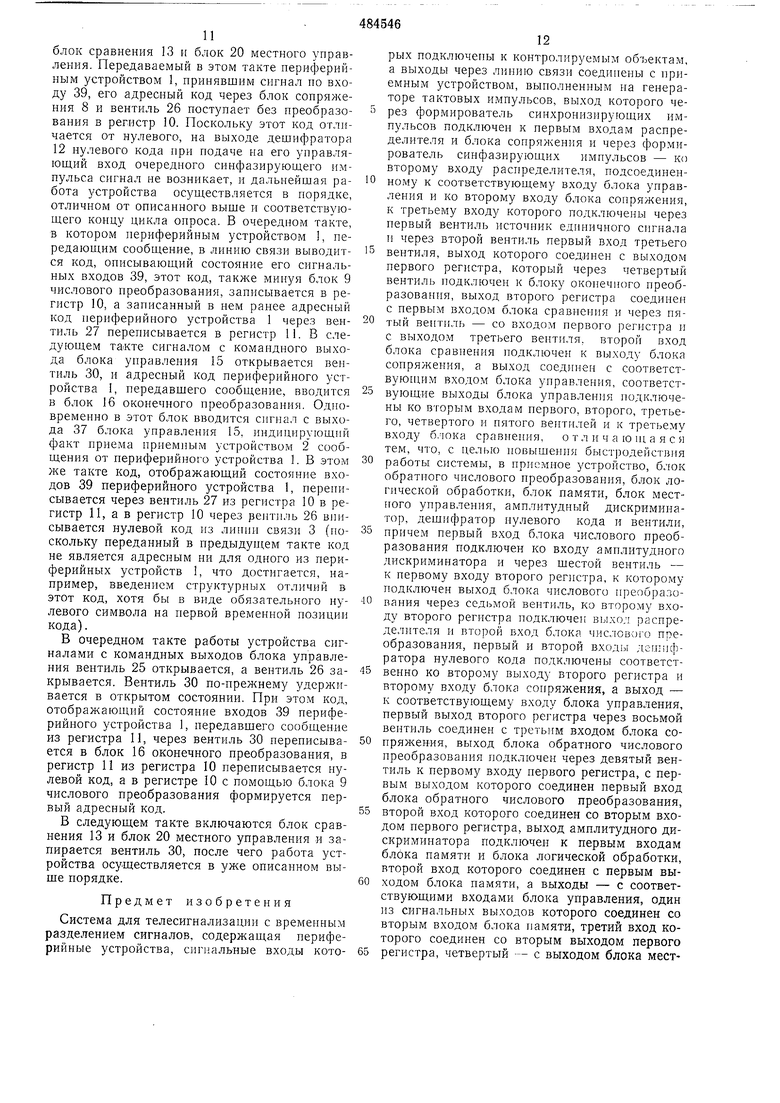

Блок-схема предлагаемой систе лы приведена на чертеже, где 1 - группа периферийных устройств; 2 - приемное устройство; 3- линия связи.

Приемное устройство 2 содержит генератор 4 тактовых 1мпульсов, формирователь 5 синхронизирующих имиульсов, формирователь 6 синфазируюн1их нмпульсов, распределитель 7, блок сопряжения 8, блок 9 числового нреобразования, регистры 10 и 11, дешифратор 12 нулевого кода, блок сравнення 13, блок 14 обратного числового преобразования, блок управления 15, блок 16 оконечного нреобразования, амнлитудный дискриминатор 17, блок 18 логической обработки, блок памяти 19 с блоком 20 местного управления, источник 21 едииичного сигнала и управляемые вентилн 22-30, выходы 31, 32, 33 блока логической обработки, сигнальные выходы 34-38 блока управления, сигнальные входы 39 нериферийных устройств. Командные выходы блока управления 15 подключены к управляющим входам вептилей 22-30, блока сравнения 13 и блока 20 местного управления (эти связи на чертеже обозначены буквои «к).

Блок 9 числового преобразования обеспечивает прибавление к числовому выражению поданного па его вход кода числовой константы, например «1.

Блок 14 обратного числового преобразования обесиечивает вычитание из числового выражения поданного на его вход кода той же числовой константы.

Блок управлеиия 15 может быть выполнен в виде группы регистров сдвига, каждый из которых подключен к своему адресному входу, а выходы этих регистров объединены через комбинационную логическую схему.

Блок памяти 19 может быть выполнен на базе оперативного запоминающего устройства любой известной конструкции с адресной структурой.

Периферийные унлотнительные устройства 1 через свои сигнальные входы 39 связаны с контролируемыми объектами. Эти устройства обеспечивают при поступлении на их входы через линию связи 3 индивидуальиых адресных кодов генерацию в линию связи индивидуальных ответных кодов той же структуры, что и адресные, а также спорадическую передачу в линию связи сообщений о фактах изменения состояний подключенных к ним контролируемых объектов в виде последовательности кодов, содержаи;ей код пачала передачи (состоящий из одних единичных символов), собственный адресный код и код, нозиционно отображающий значения сигналов иа сигнальных входах 39 в момент нередачи сообщения.

Ответные (так же, как и адресные) коды всех нериферийных устройств 1 на первой временной позиции обязательно содержат единичный символ, нричем эта позиция кода преобразования в блоках прямого 9 н обратного 14 нреобразования не подвергается.

Работу устройства удобио рассмотреть первоначально в нредположещш, что сигналы на входах 39 всех нериферийных устройств 1 отсутствуют. Для удобства рассмотрепия целесообразно также считать, что нодключснные к линии связи 3 периферийные устройства i образуют полный комнлект, характеризуюндийся тем, что ответный код каждого уст;5.)йства отличается от адресного кода этого устройства па величину, равную значеи;но числовой константы, иснользусмой в блоке У числового нреобразован1 я, i, кро.ме того, яьляется адресным кодо.м другого устройства, а коды, состоящие из одних единичных п.

нулевых символов не являются ад : еснымн ни для одного нз нериферийных устройств.

Генераторо.м 4 тактовых импульсов приемного устройства 2 осуп ествляется постоянная генерация последовательности имнул.ьсов, на

основе которой формирователями синхронизирующих имнульсов 5 и синфазирующих имнульсов 6 осуществляется генерация последовательностей соответствующих имнульсов, выводимых через блок сопряжения 8 в линию

связи 3. При этом синхронизируюнше импульсы исиользуются для ограпичения временных позиций передаваемых но линии связи 3 кодов, синфазирующие импульсы служат для временного разделения этих кодов, иричем интервал между двумя соседними синфазирующими импульсами образует такт работы устройства.

Если как это было оговорено выше, но линии связи передается неискаженная последовательность адресных (ответных) кодов, сигналы на командных выходах блока управления 15 таковы, что вентилн 25 и 27 открыты, на входах блока сравнения 13 и блока 20 местиого управления присутствуют разрешающие

сигиалы, остальные вентили закрыты, а сигиалы на сигнальных выходах 34, 35, 36, 37 и 38 блока управления 15 отсутствуют.

Пусть в некоторый момент времени но линии связи 3 нередается адресный код одного

из нериферийных устройств 1. Этот код одновременно вводится во все периферийные устройства, а также через блок сравнения 8 в блок 9 числового преобразования, откуда увеличенный на величину числовой константы

через открытый вентиль 25 вводится в регистр

10, сдвиг которого обеспечивается подачей на его тактирующий вход импульсов с выхода распределителя 7. Таким образом, к концу передачи данного кода по линии связи 3 в регистре 10 оказывается записанным код, передача которого по линии связи ожидается i5 последующем такте. Одновременно код, ранее записанный в регистре 10, т. е. равный коду, передаваемому по линии связи 3 в данном такте, через открытый вентиль 27 переписывается в регистр И, т. е. к концу такта в регистре 11 оказывается записанным адресный код периферийного устройства 1, которое должно отвечать в следующем такте.

Очередным синфазирующим импульсом с выхода формирователя 6, оиределяющим иачало нового такта, осуществляется запуск блока 20 местного управления, который подает сигнал считывания в блок памяти 19. При этом осуществляется считывание информации из ячейки памяти с адресом, равным адресному коду периферийного устройства 1, ответ которого ожидается в этом такте. Ячейка содержит два идентификатора, значение одпого из них (например, 1-го) вводится в блок 18 логической обработки (этот индентификатор равен «1, если данное иериферийное устройство 1 отвечало в предыдущем цикле опроса, и «О (в противном случае), а значение другого (2-го) идентификатора содержит «О, если данное периферийное устройство 1 отвечало правильно в предыдумшм цикле опроса, и «1 Б противном случае.

Далее пернферийпым устройством 1. принявшим в прелыдун1,ем такте свой адресной код, осуществляется генерация в линию связи 3 ответного кода, который, как и ранее, через блок сопряжения 8 и блок 9 числового преобразования .поступает в регистр 10.

При этом первый символ кода (всегда единичный, как это было отмечено выше) поступает в амплитудный дискриминатор 17, с выхода которого единичный сигнал, свндетельствующий о наличии сигиала иа выходе дискриминатора 17, поступает в блок 18 логической обработки и одновременно на одни из входов блока памяти 19. При наличии единичных сигналов на обоих своих входах блок 18 логической обработки не вырабатывает никаких сигналов ни на одном из своих выходов 31, 32, 33. При этом блоком управления 15 также удерживается нулевой сигнал на выходе 38, в результате чего прп подаче на управляюп;пй вход блока памяти 19 сигнала записи с выхода блока 20 местного управления в его ячейку с адресом, равным адресному коду отвечающего в этом такте периферийного устройства 1, записывается «1 с выхода амплитудного дискриминатора и «О с выхода 38 блока управления 15 (т. е. значения обоих идеитификаторов не :1зменяются по сравнению с предыдущими) .

Код. генерируемый периферпйным устройством 1, поступает также через блок сопряжения 8 на один из входов блока сравнепия 13,

на другой вход которого одновременно ностуиает код с выхода регистра 10. При этом, если периферийное устройство 1 отвечает правильно, оба этих кода совпадают, и блоком сравиения 13 никаких сигналов Lie вырабатывается. Код с выхода регистра 10 через открытый вентиль 27 переписывается, как и в предыдущем такте, в регистр 11.

Таким образом пропсходпт работа устройства, когда в каждом последующем такте по линии связи передается код, от;п1чаюп1,ийся от кода, переданного в предыдуишм такте, на числовую величину, равную числовой конста те, нспользуемой для преобразования кодов в блоке 9 числового преобразования, т. е. когда никакой ниформации через периферийные устройства 1 в устройство ие поступает, а все периферийные устройства функцио1 груют нормально.

При отсутствии ответа от какого-либо нериферийиого устройства (вызваином отказом этого устройства, нарушением в линии связи 3 или отключеиием этого устройства от источника питания или от линии связи) в соответствующем тагсте на первой времешюй позиции сигнал на вход алшлитудного днскримпнатора 17 не иоступает, в результате чего с выхода амплитудного дис С1М : 111матора на вход блока 18 логической обработки поступает пулевой спгнал. в то время как с Г:Ь хо1а блока памяти 19 на другой вход бгклп 18 .югической обработки поступает еди;; ;чиос Злаченпе идентифткатора г --:лЮ1С1110го состояп1:я данного перифсри1;|,ого устройства I. В этом случае блоком 18 ,итическо15 обтаботкп вырабатывается с;;гпал па его выходе 3. поступаюнлкй на соответствуюпии вход блока управления 15. Одповре:лепно нулс;зоп сигнал с выхода амплитудного дпскрпмиплтора 17 поступает на вход блока палтяти 19, куда после подачн на другой его вход сигнала записп с выхода блока 20 местного упразлеп 1я за1П1сывается пулевое значеппс соотвстствуюпюго идентификатора.

5

Блоком уп; а:;ления 15 после получения пускового сигнала с выхода 31 блоко 18 логической обработк ; с)суп:естнл5;ет1я вь;дача командных сигналов, отпираюп1; Х в данном такте вентили 24 п 30. в рсзул тате чего код из

0 регистра 10 через блок сопря:лС П я 8 зыводптся в липию связи 3, за леп1ая там ответный кол отключенного перибсршпюго устройства 1, а код из регистра 11 (равный адресному коду неответпвшего периферийного уст5ройства) вводится в блок 16 прсобразоваппя. где лпбо осуществляется его визуальная пнд1;кацпя. либо прсобразовап1;е в вид, удобпый для дальнейшего пспользопапня в каких-лпбо регистрирующих устройствах.

0 Туда же в данном такте вводгптя сигнал с выхода 34 блока управленпя 15, пнднцпруюн,нй характер возникшей аварпйной ситуации (в данном случае - отсутствие ответа от нериферийного устройства). Все сигналы на выходах блока 15 гасятся

5 после поступления на тактирующий вход блока управления ближайшего синфазирующего импульса с выхода формирователя 6 синфазирующих импульсов. В дальнейшем, в последующих циклах работы устройства, при повторном отсутствии сигналов с выхода данного периферийного устройства 1 в момент прохождения первой временной позиции кода в блок 18 логической обработки с выхода блока памяти 19 будет поступать уже нулевое значение идептифигсатора включенного состояния данного иериферийного устройства 1, что в сочетании с иулевым значением сигнала на выходе амплитудного дискриминатора 17 будет вызыват1 появление сигнала на выходе 32 блока 18 логической обработки, который, поступая на соответствующий вход блока управления 15, будет, в свою очередь, вызывать появление на его командном выходе сигнала, отпирающего лищь вентиль 24. Таким образом, каждый раз будет осуществляться замещение отсутствуюп1его ответного кода в линии связи 3 кодом, выводимым из регистра 10, а в блок 16 оконечного нреобразования информация об отключении данного периферийного устройства, являющаяся теперь избыточной, поступать не будет. Если в одном из циклов работы устройства данным периферийным устройством 1 вновь будет выведен, ответный код в линию связи 3 (аварийная ситуация устранена), на первой временной позиции кода на выходе ямплп- удного дискриминатора 17 воз 1икнет единичный сигнал, который в сочетании с нулевым значением идентификатора, поступающего из блока памяти 19, вызовет появление сигнала на выходе 33 блока 18 логической обработки, поступающего далее на соответствующий вход блока управления 15, на командном выходе которого появится сигнал, отпнраюп ий только вентиль 30. При этом адресный код данного периферийного устройства из регистра 11 вводится в блок 16 оконечного преобразования, и туда же одновременно вводится сигнал с выхода 35 блока управления 15, индицирующий характер возникшей ситуации (в данном случае - включение периферийного устройства 1). В этом же такте, благодаря наличию единичного сигнала на выходе амплнтудного дискриминатора 17, в блок памяти 19 будет вновь записано единичное значение идеитификатора включенного состояния данного иериферийного устройства 1, и в дальнейнльх циклах работы устройства при наличии ответного кода этого периферийного устройства будет осуществляться, как это было описано выще. Если каким-либо периферийным устройством 1 в линию связи 3 будет выведен неверный ответный код (но с наличием единичного символа на первой временной позипни), этот код, поступ,ая через блок сопряжения 8 на вход блока сравнения 13 вызовет ноявление нд его выходе сигнала (вследстВке несовнаеипя этого кода хотя бы в оЛиом симвг)ле с кодом, вводимым через другой вход в блок сравнения 13 из регистра 10). В результате на соответствующий вход блока унравления i5 будет иода и сигнал, который в следующем такте работы устройства вызовет на командных выходах блока управления появлепие сигналов, отпираюи1,их вентили 22 и 29, запирающих вентиль 27 п отключающих блок сравнения 13 н блок 20 местного управления. При этом в линяю связи 3 через вентиль 22 и блок сопряжения 8 от источника 21 единичного сигнала будет выве.т.еи код, содержащий только единичные символы и заглущаюицш ответный код иериферийного устройства I, воспринявщего неверный ответный код, переданный по линии связи 3 в предыдуш.ем такте, как свой адресный код. Запираппе веи1иля 27 исключает передачу в регистр II из регистра 10 неверного кода, Bruiсаниого в него через блок сопряжения 8 и блок 9 числового преобразования 0 предыдущем такте. Отиирание вентиля 29 обеспечивает нередачу кода, записанного в регистре П., па его же вход через блок 14 обратиого числового нреобразова 1ия, благодаря чему в данном такте в регистре 11 восстанавливаете; значение адресного кода периферийного устройства I, выдавщегс) в иредь ду1цем такте неверный ответный код. Подача запреи1,ающих сигналов на входы блока сравнения 13 и блока 20 местного управления исключает их работу ;з данном такте. После подачи lia тактируюпиш вход блока унравленял 15 очередного сиифазируюн1,его импульса с выхода формирователя 6 синфазируюидих импульсов происходит смена сигналов на его командных входах. Прн этом в очередном также вентиль 22 запирается, вентиль 27 удержпвается в запертом состоянии, вентиль 30 отпирается, веитиль 29 запирается, на соответствующем входе блока сравнения 13 удерживается запирающий сигнал, на вхол, блока 20 местного управления подается разрешающий сигнал, а также выдаются сигналы на выходах 36 и 38 блока управления 15. В результате этого в блок памяти 19 по адресу, равному адресному коду периферийного устройства 1, ответивщего неверно, запнсыиается еднничное значение второго идеитификатора, в .iiii-iHio связи выводится код, состоящий только из нулевых символов, а в блок 16 окоиечиого преобразования через вентиль 30 из регистра 11 вводится адреспыГ; код периферийного устройства , ответившего неверно, а также с выхода 36 блока уиравления 15 сигнал, индицируюн1,ий данную ситуацию (неверный ответ периферийного устройства). При этом нулевой код, постунает через блок сонряжения 8 и блок 9 числового преобразования в регистр 10, преобразуется в нем в первый адресный код, а в регистре 11 оказывается затесанным нулевой код. Очередным синфазирующим импульсом восстаиавливаются исходьые значения сигналов на выходе блока управления 15. Поскольку на переданный в линию связи 3 предыдущем такте нулевой код не отвечает ни одно из периферийных устройств 1, а из блока памяти 19 по нулевому адресу считывается также нулевое значение первого идентификатора, блоком 18 логической обработки на его выходе 32 формируется сигнал, который, как это было описано выше, поступая в блок управления 15, приводит к выводу в данном такте кода из регистра 10 через вентиль 24 и блок сопряжения 8 в линию связи 3, после чего начинается новый цикл опроса периферийных устройств 1. В последуюи1их циклах работы устройства в такте, следующем за тактом, в котором по линии связи передается адресный код периферийного устройства 1, ответившего ранее неверно, из блока памяти 19 считывается единичное значение второго идентификатора, которое, поступая на соответствующий вход блока управления 15, вызывает появление на его командных выходах сигналов, отпирающих в этом такте вентиль 22 и отключающих блок сравнения 13. В результате в этом такте в линию связи 3 от источника 21 единичного сигнала через вентиль 22 и блок соирял ения 8 выводится единичный код, заглущающий в линии связи 3 неверный ответный код периферийного устройства 1, а в регистр 11 переписывается правильный ответный код этого устройства из регистра 10. В следующем такте работы устройства осуществляется смена сигналов на командных выходах блока управления 15, причем вентили 22 и 27 запираются, отпираются вентили 23 и 28 и подаются запрещающие сигналы на унравляющие входы блока сравнения 13 и блока 20 местного управления. В результате в линию связи 3 через вентиль 23 и блок сопряжения 8 с линией связи из регистра 11 выводится правильный ответный код отвечающего неверно периферийного устройства 1, этот же код, благодаря включению обратной связи через вентиль 28, вновь переписывается в регистр 11, а обращення к блоку памяти 19 не производится. Очередным сннфазирующим импульсом нроизводится восстановление исходных сигналов на командных выходах блока управления 15, после чего устройство входит в обычный режим работы. Изменение значения второго идентификатора в блоке памяти 19 для данного периферийного устройства 1 осуществляется иосле отключения этого устройства для его замены или ремонта. При этом на первой познции ответного кода этого устройства будет принят нулевой символ, вызывающий затем иоявление сигнала на выходе 31 блока 18 логической обработки и иоследующую работу устройства ио уже описанной программе, гд:е на вход блока памяти 19 в момент выполнения им записи с выхода 38 блока управления 15 подается сигнал, соответствующий нулевому значению второго идентификатора. В конце каждого никла опроса периферийых устройств 1 последним оирашиваемым пеиферийным устройством в линию связи 3 геерируется код, состояищй только из единичых символов. Этот код заппсывается через блок сопряжения 8 и блок 9 числового преобразования в регистр 10 в виде кода, содержащего только нулевые символы, в результате чего при поступлении на управляюпгий вход дешифратора 12 нулевого кода ближайщего синфазирующего импульса на его выходе возникает сигнал, поступающий иа соответствующий вход блока управления 15, на командных выходах которого в следуюихем такте возникают сигналы, запирающие вентиль 25 и отпираюнще вентиль 26. Поскольку в этом такте ни одно из нериферийных устройств 1 не отвечает, по лииии связи 3 проходит код, состоянии только из нулевых символов, который через блок сопряжения 8 и вентиль 26 без преобразования записывается в регнстр 10, вызывая при поступлении очередного синфазируюи1,его импульса на управляющий вход дешифратора 12 нулевого кода вновь появление сигиала на его выходе, который, поступая на вход блока управления 15, вызывает появление на его командных выходах в следуюн,ем такте снгналов, запирающих вентиль 26 и отпирающих вентиль 25, а также отключающих блок сравнения 13 и блок 20 местного управления. Поскольку в этом такте по линии связи 3 вновь передается код, состоящий только из нулевых символов, он, поступая в регистр 10, теперь уже через блок 9 числового преобразования, записывается в йен в виде первого адресного кода, после чего в начале следующего такта возникает снгнал на выходе 32 блока 18 логической обработки, и работа устройства продолжается уже описанным выше способом. При возникновении сигнала от контролируемого объекта на одном из входов 39 какоголибо периферийного устройства 1 это ycTpoiiство передает в линию связи 3 в течение трех тактов сообщение, состоящее из кода начала передачи (в первом такте), адресного кода этого периферийного устройства (во втором такте) и кода, позиционно отобрал ающего состояние его входов 39 (в третьем такте). При этом код начала иередачи, состоящий только из единичных символов, через блок сопряжения 8 и блок 9 числового преобразования поступает в виде кода, состоящего только из иулевых символов, в регистр 10, после чего при подаче на управляющий вход дешифратора 12 нулевого кода ближайшего синфазирующего импульса с выхода формирователя 6 синфазирующих имиульсов на выходе этого дешифратора возникает сигнал, поступающнй на соответствующий адресный вход блока управления 15. На командных выходах этого блока в очередном такте возникают сигналы, благодаря которым в этом такте запирается вентиль 25, отпирается вентиль 26 и отключаются

11

блок сравнения 13 и блок 20 местного управления. Передаваемый в этом такте периферийным устройством 1, принявшим сигнал но входу 39, его адресный код через блок сопряжения 8 и вентиль 26 поступает без преобразования в регистр 10. Поскольку этот код отличается от нулевого, на выходе дешифратора 12 нулевого кода при подаче на его управляюш,ий вход очередиого сннфазируюш,его импульса сигнал не возникает, и дальнейшая работа устройства осуществляется в порядке, отличном от описанного выше и соответствующего концу цикла опроса. В очередном такте, в котором иериферийным устройством 1, передающим сообщение, в линию связи выводится код, описывающий состояние его сигнальных входов 39, этот код, также минуя блок 9 числового преобразования, записывается в регистр 10, а записанный в нем ранее адресный код периферийного устройства 1 через вентиль 27 переписывается в регистр 11. В следующем та-кте сигналом с командного выхода блока управления 15 открывается веитиль 30, и адресный код периферийного устройства 1, нередавшего сообщение, вводится в блок 16 оконечного преобразования. Одновремеиио в этот блок вводится сигнал с выхода 37 блока управления 15, индицирующий факт приема приемным устройством 2 сообщения от периферийного устройства 1. В этом же такте код, отображающий состояние входов 39 периферийного устройства 1, переписывается через вентиль 27 из регистра 10 в регистр 11, а в регистр 10 через ре1ггиль 26 вписывается нулевой код из лииии связи 3 (поскольку переданный в предыдун1;ем такте код не является адресным ни для одного из периферийных устройств 1, что достигается, например, введением структурных отличий в этот код, хотя бы в виде обязательного нулевого символа на иервой временной иозиции кода).

В очередном такте работы устройства сигналами с командных выходов блока управления вентиль 25 открывается, а вентиль 26 закрывается. Вентиль 30 по-прежнему удерживается в открытом состоянии. При этом код, отображающий состояние входов 39 периферийного устройства 1, передавшего сообщение из регистра 11, через вентиль 30 переписывается в блок 16 оконечного преобразования, в регистр 11 из регистра 10 переписывается нулевой код, а в регистре 10 с помощью блока 9 числового преобразования формируется первый адресный код.

В следующем такте включаются блок сравнения 13 и блок 20 местного управления и запирается вентиль 30, после чего работа устройства осуществляется в уже описанном выше порядке.

Предмет изобретения

Система для телесигнализации с временным разделением сигналов, содержащая периферийные устройства, сигнальные входы кото12

рых подключены к контролируемым обьектам, а выходы через линию связи соедииены с приемным устройством, выиолненным на генераторе тактовых импульсов, выход которого через формирователь синхронизирурощих нмпульсов подключен к первым входам распределителя и блока сопряжения и через формирователь сиифазирующих импульсов - ко второму входу распределителя, подсоединеиному к соответствующему входу блока управления и ко второму входу блока сопряжения, к третьему входу которого подключены через первый вентиль источник единичного сигнала и через второй вентиль первый вход третьего

вентиля, выход которого соединен с выходом первого регистра, который через четвертый вентиль подключен к блоку оконечного преобразования, выход второго регистра соедииен с первым входом блока сравнения и через пятый вентиль - со входом первого регистра и с выходом третьего вентиля, второй вход блока сравнения подключен к выходу блока сопряжения, а выход соединен с соответствующим входом блока управления, соответствующие выходы блока управления подключены ко вторым входам первого, второго, третьего, четвертого и пятого вентилей и к третьему входу б/юка сравнения, о т л и ч а ю ni а я с я тем, что, с целью повышения быстродействия

работы системы, в приемное устройство, блок обратного числового нреобразовання, блок лог 1ческой обработки, блок памяти, блок местного управлеиия, амплитудный дискриминатор, дешифратор нулевого кода и вентили,

причем первый в.ход блока числового преобразования подключен ко входу амплитудного дискриминатора и через шестой вентиль - к первому входу второго регистра, к которому подключен выход блока числового преобразования через седьмой вентиль, ко второму входу второго регистра подключен выхол распределителя и второй вход блока числового преобразования, первый и второй входы дегппфратора нулевого кода подключены соответственно ко второму выходу второго регистра и второму входу блока сопряжения, а выход - к соответствующему входу блока управления, первый выход второго регистра через восьмой вентиль соединен с третьим входом блока сопряжения, выход блока обратного числового преобразования подключен через девятый вентиль к первому входу первого регистра, с первым выходом которого соединен первый вход блока обратного числового преобразования,

второй вход которого соединен со вторым входом первого регистра, выход амплитудного дискриминатора подключен к первым входам блока памяти и блока логической обработки, второй вход которого соединен с первым выходом блока памяти, а выходы - с соответствующими входами блока управления, один из сигнальных выходов которого соединеи со вторым входом блока памяти, третий вход которого соединен со вторым выходом первого

регистра, четвертый - с выходом блока местного управления, ко входам которого соответственно подключены выходы генератора тактовых импульсов и формирователя спнфазлруюп их импульсов, соответствующие выходы блока управления подключены ко вторым входам шестого, седьмого, восьмого и девятого вентилей, а сигнальные выходы - к блоку оконечного преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный телесигнализационная система с временным разделением каналов | 1974 |

|

SU519754A1 |

| Система для телесигнализации с временным разделением сигналов | 1974 |

|

SU478346A1 |

| Система телесигнализации | 1978 |

|

SU748489A1 |

| Телемеханическая система | 1975 |

|

SU610099A1 |

| Приемное устройство системы телесигнализации | 1979 |

|

SU773673A1 |

| Устройство для ввода информации | 1977 |

|

SU737941A1 |

| Приемное устройство системы телемеханики | 1976 |

|

SU596996A1 |

| Приемное устройство для системы телемеханики | 1975 |

|

SU561214A1 |

| Система для телесигнализации с временным разделением сигналов | 1974 |

|

SU518789A1 |

| Телемеханическая система с временным разделением каналов | 1976 |

|

SU616648A1 |

Авторы

Даты

1975-09-15—Публикация

1974-03-13—Подача