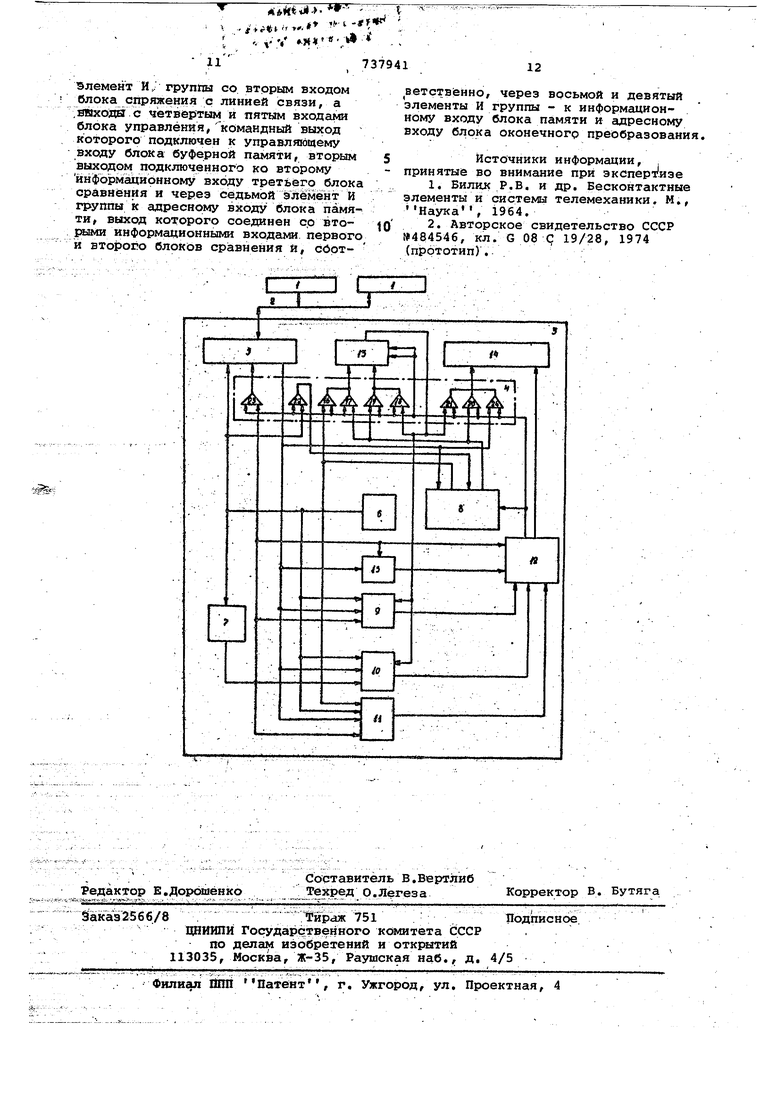

Изобретение относится к автоматике, телемеханике и вычислительной технике и может быть использовано в рассредоточенных системах для ввода информации о состоянии удаленных объектов, Известна устройства для ввода информации содержащие блоки синхронизации и синфазирования,генератор адресов и управляемый приемник ответ ных сигналов, выходом соеди11енный со входом блока оконечного преобразования, осуществляющему вывод информации из устройства. Такие устрой ства осуществляют циклическую генерацию адресов объектов, по которым передается информация -р состоянии периферийных устройств объектов 1 Недостаток таких устройств заключается в их низкой пропускной способности из-за большого объема избыточной информации, обрабатываемой устройством, так как опрос источник и пе)едача данных о его состояний .осуществляется на каждом цикле работы, независимо от того, изменялось ли состояние объекта или нет. Наиболее близким техническим ре шением к предлагаемому является уст ство для ввода информации, содержащё блоксбЬряжения с линией связи, соединенный л иней входом и выходом, соответственно, с линейными входом и выходом устройства, груйпу элементов И, блок синфазирования, блок синхронизации, блок управления, блок памяти, блок оконечного преобразования, блок дешифрации и первый блок сравнения, причете выход блока синхронизации соеданен с первым входом блока сопряжения с линией связи, входом блока синфазирования и контактирующим входом первого блока сравнения, первый вход которого соединен со входом дешифратора и выходом блока сопряжения с линией связи, а управляющий вход - с выходом блока синфазирования, управляющим .входе б.пока дешифрации и первым входом; блока управления, соединенного соответствующими командными выходамис управляющими входами элементов И группы и входами записи и считывания блока памяти, а вторым и третьим входами и выходом соответственно с выходами блока .дешифрации и первогоблока сравнения и входом признака блока оконечного преобразования 2, . Недостатком этого устройства является низкое быстродействие. Цель изобретения - повышение быст .действия устройства. Поставленная цель достигаемся тем, чт6 в ус 1 ройство ввёдё ны блик буферной памяти и два блока сравнения, причем тактирующие входы второг 4 третьего блоков сравнения соединен с выходом блока синхронизации и чере .первый элемент И группы с тактиру рщим йходом блока буферной памяти, первый выход которого соединен, соот ветственно, через второй, третий и четвертый элементы И группы с адресным и информационнЕлм уходами блока памяти и адресным входом блока оконечного преобразования, первые информационные входы второго и третьег блоков сравнения йЬдклюЧены к выходу блока сопряжения с линией связи, вхо ду блока буферной памяти и через пятый, элемент И группы к адресному входу бдока оконечного преобразоваНИИ, управляющие входы второго.и третьего блоков сравнения соединены с выходом блока инфазирования.и чере шестой элемент И группы со вторым входом блока сопряжения с линией связи, а выходы с четверт1ым и пятым входс1ми блока управления, командный ;выход которого подключен к управляю1щему входу блока буферной памяти, вторым выходом подключенного ко - второму информационному входу третье го блока сравнения и через седьмой элемент И группы - к Адресному входу блока памяти,, выход которого соедине со вторыми информационными входами первого и второго блоков сравнения и, соответственно, через восьмой и д вятый элементы И группы - к. информационному входу блока памяти и адресному входу бдока оконечного преобразования. . . . На чертеже изображена блок-схема устройства-. Устройство содеЁ)жит периферийные устройства 1 контролируемых объектов подключенные через линию 2 связи к устройству 3 для ввода информации, включающему группу .4 элементов И, блок 5 сопряжения с линией связи, блок б синхронизации, блок 7 инфа зирования, блок 8 буфер юй памяти, первый, второй 10 и третий 11 блок сра(внелия,блок 12 управления, блок 13 пам/1ти, блок 14 оконечного преобразования, блок 15 дешифрации и элементы -и 16-24 группы 4 элементов И БЛ1ЭК..9 формируют ригнал на своем выходе и в случае неравенства операн дов, направляемых на его информацион ные входы, а блоки 10 и 11 формируюФ сигналы на своих выходах в случае, если разнос.ть операндЬё подаваемых н их первые и вторые информационные . входы имеет лоложитёльный знак. Блок 15 формирует на своем выходе CHl-Hал при поступлении на его вход кода, не .используемого в .качестве адресного и содержащего только единичнае симва

737941 Устройство работает следующим образом. . : В процессе работы системы блоком б постоянно осуществляется генерация последовательности синхроимпульсов, поступающих на входы соответствующих блоков устройства, а также через блок 5 и линию 2 связи на входы всех подключенных к. линии периферийных устройств 1, выполняя синхронизацию их работы. Блоком 7 осуществляется постоянная генерация последовательности синхронизирующих импульсов, также поступающих на входы соответствующих блоков устройства 3, и черезблок 5 сопряжения и линию 2 связи на входы периферийных устройств 1. При этом период следования синфазирующих Импульсов кратен периоду следования синхроимпульсов, причем интервал- между двумя соседними синфазирующими импульсами образует такт работы устройства, а содержащееся в одном такте число синхроимпульсов равно значности адресных кодов периферийных устройств 1. . Предположим, что в линии 2 связи подключённо ппериферийных устройств 1, причем п меньше N, где N - максимальное количество периферийных устройств 1, которое вообще может быть подключено к системе при условии, что адресные коды всех этих устройств отличаются друг от друга, и, кроме того, никаких сигналов от контролируемых объектов на входы периферийных уплотнительных устройств 1 не поступает. , Пусть в пределах некоторого такта по линий 2 связи не передается ни одного сигнала (пер.едается нулевой адресный код). Этот факт регистрируется всеми периферийными устройствами 1, после чего в следующем также каждым из этих устройств в линию 2 начинает в последовательной форме /старшими разрядами вперед выводиться его адресный коД.При этом каждым из периферийных устройств 1 осуществляется посимвольное сравнение формируемого им кода с кодом, реально передаваемым по линии 2 связи, и в случае обнаружения ча любой из временных позиций,, кода импульса в -линии 2 связи при отсутствии импульса на выходе устройства формирование кода этим устрой.ством прекращается. Таким образом, к концу такта передачу адресного кода прекращают все периферийные устройства 1, за исключением одного, имеющего максималь.йое числовое выражение адресного кода, причем именно этот код и передается по линии 2 связи В данном такте. ,- , . В Следующем такте все периферийные устройства 1 вновь ос5т1ествляют формирование своих адресных кодов, исключением устройства, код которог был передан в предыдущем такте и которое теперь прекращает формирова ние сврего адресного кода вплоть до очередной передачи по линии 2 свйэи нулевого кода. Взаимодей ствие остальных пер 1ферийных устрой ств 1 в этом такте рсуществляется так же, как и в предыдущем, в резул тате чего по линии 2 связи в данном такте передается адресный код устро ства, имеющего второе по величине среди подключенных в данный момент к линии 2 связи периферийных устройств 1 числовое выражение кода, после чего это устройство также прекращает формирование своего адресного кода вплоть до очередной передачи по линии 2 связи нулевого кода. Процесс продолжается аналогичным образом до тех пор, пока по линии 2 связи передаются адресные коды всех периферийных устройств 1, подключенных в данный момент в системе. Сформированная таким образом группа адресных кодов образует цикл работы системы, причем длительность этого цикла, выраженная в тактах, равна п. По окончании цикла все периферийные устрой ства 1 прекращают формирование своих адресных кодов, в результате Чего в очередном такте по линии 2 связи передается нулевой код и формирование цикла начинается сначала тем же образом. Предполагается, что в процессе передачи двух соседних циклов никаких изменений в составе подключенны к линии 2 связи периферийных устройств 1 не происходит, т.е, очередной передаваемый по линии 2 связи цикл адресных кодов ничем не отличается от предыдущего.- В этом случае к началу очередного цикла в блоке 13, содержащем п ячеек, в каждой ИЗ ячеек, имеющей номер, равный числовому выраясению одного из адресных кодов, участвующихв данный момент в формировании цикло оказывается записанным код, переда ваемый в данной структуре цикла вслед за данны1Л кодом. ; В ячейке с нулевым, номером оказ вается записанншл код, передаваемы в составе цикла первым. В ячейке с номером, равным наименьщему из передаваемых по линии связи в цикле кодов, оказывается записанным нулевой кодо В ячейках- блока 8 к началу очере ного такта оказываются записанными коды, соответственно, переданные по 2 связи в только что окон чившемся такте и в предшествующем ему такте.

Ь

737941 Перед началом такта блоком 12 формируются сигналы на его командных выходах, noctynaHKaHe на элемент И 17 и на вход считЕДэания блока 13, в результате чего из ячейки с номером, равным коду перёдаваекому в предыд ём такте, считывается код, который должен быть передан в данЕЮм такте, поступающий в последовательной форме в течение такта на вторые информационные входы блоков 9 и 10. На второй информационный вход блока 11 в течение такта выводится код, переданный по линии 2.связи тактом ранее. - - . 1 В течение такта из линии 2 связи через блок 5 поступает адресный код, который вводится в первую ячейку блока 8, через первые информацион,ные входы в блок 9 и в блок 15. Одновременно в блоке 8 осуществляется перенос кода, записанного в предыдущем такте в первой ячейке, во вторую ячейку, а кода, записанного во второй ячейке - в третью ячейку. В момент формирования очередного синфазирующего импульса производится анализ, поступившего в приемное устройство 3, адресного кода. Поскольку цикл, .передаваемый в данный момент времени по Линии 2 связи, абсолютно идентичен циклу, переданному ранее, : код принятый из линии 2 связи, оказывается равным коду, выведенному из блока памяти 13. Ори этом на выходах блоков 9, 10 и. 11 и блока 15 никаких сигнгшов не 3)ормируется,- В этой ситуации на командных выходах блока 12 формируется сигнал, отпирающий элемент И 17, в результате чего, адресный код, принятый в данном такте из лянии 2 связи, Г1оступает-из первой ячёйки блока 8 через первый выход на адрес;ный вход блока 13; сигнал, поступающий на вход считывания 13, в результате чего с выхода этого блока в очередном такте считывается код, прием которого из линии 2 связи ожидается; сигналы, удерживающие в пре-, делах очередного такта в закрытом состоянии элементьа И 16, 18, 19, 20, 21 и 24 и в открытом состоянии элементы И 22 и i3, . , . . Таким образом работа,устройства рсуществляется до тех пор, пока сохраняется идентичность цикла адресных кодов по линий 2 связипредыдущему циклу. : . При ЭТОМ никаких сигналов на вхой блока 14 оконечного преобразования не поступает.-. -В процессе работы систёмы могут возника -ь следующие ситуации, вызывающие измерения в составе очередного цикла:

отключение ot линии 2 связи одного или нескольких периферийных устptiftCTS 1;

подключение к линии 2 связи одного или нескЬльких периферийных устройств 1, отключенных ранее;

отказ периферийного устройства 1, выражающийся в том, что оно пройолжает формировать свой адресный код после того, как он е5ыл передан по линии Связи;

поступление сигнала на вход одного из периферийных устройств 1 об изменении состояния контролируемого объекта. ,

Возникновение первой ситуаций

означает, что в некотором такте

код, принятый из .линии 2 связи оказывается меньше кода, прием которого ожидается, В этом случае В-конце такта блоком 9 вырабатывается сигнал о неравенстве принятого и ожидаемого кодов, поступающий на вход блока 12. Блоками 10 и 11 и

блоком 15 йикаких сигналов на их выходах по-прежнему не формируется,. При блоком 12 на его командных выходах формируются: сигнал, отпирающий элемент И Гб, в результате чего, код, принятый в предвадущем. такте, постула ет из второй ячейки блока 8 черезвторой выход на адресный вход блока 13; сигнал, отпирающий элемент И 19; -сигнал, поступающий на вход считывания блока 13, в ре- . зультате чего,, код, прием которого ожидается в данном.такте, поступает на адресный вход блрка 14; сиг.нал, отпираюЩий элемент riI9f, в результате чего, код, принятый в данном такте из линии 2 связи, -поступает из первой ячейки блока 8 через э.ле- мент И 19 в блок 13; сигнал, поступающий на вход записи .блока 13, в результате чего в ячейку с номером, равным коду, принятому из линии 2

связи в предыдущем такте, запИсывае.тся код, .принятый в данном такте, ;

На выходе блока 12 формируется сигнал, лоступающйй на признаковый . вход блока 14 и идентифицирующий факт откЛ очёния от линии 2 связи периферийного устройства I, адресный код которого введен в блок 14, Этот, блок осуществляет индикацию принятых им сигналов. . Таки.м в результате.выполнения/операций, адресный код отключившегося от линии связи периферийного устройства 1 вычеркивается из

.списка, заложенного в блоке 13. .

. Далее на командных выходах блока-, 12 формируются .сигналы, аналогичные

.случаю,. когда изменений в цикле, не обнаружено, и работа устройства прО

лолжается описанным выйе образом.

8

737941

Возникновение второй ситуации означает, что в некотором такте, код, принятый из линии 2 связи, оказывается больше кода, прием которого ожидается, но меньше кода, принятого в предыдущем такте, В этом случае в конце такта блоком 5 вьфабатывается сигнал о неравенстве принятого и ожидаемого кодов, а :блоком 10 формируется сигнал о превышении принятым кодом величины . ожидаемого кода. Блоки 11 и 15 никаких сигналов на своих выходах по-прежнему не формируют. В результате блоком 12 на его командных выходах формируются следующие сигналы: путем последовательного отпирания элементов.И J6 и 18 и подачи сигнала на вход считывания блока 13 осуществляется подача на его адресный вход кода, прием которого ожидается в данном такте; путем оттгарания элемента И 17 и подачи сигнала навход записи блока 13 осуществляется запись этого кся в ячейку с номером, равным коду, принятому в данном такте; путем отпирания элементов И 16 и 19 и подачи сигнала . на вход записи блока 13 осуществляется запись кода, принятого в данном такте, и, наконец, путем отпирания элемента И 20, осуществляется передача кода, принятого в данном такте, на адресный вход блока 14,. . .

Одновременно, на выходе блока 12 формируётся сигнал, поступающий на признаковый вход блока 14 и идентифицирующий факт подключения к линии 2 связи периферийного устройства 1, адресный код которого был введен в блок 14. ,

Таким образом, в результате выполнения перечисленных операций осуществляется исключение вно.вь подключившегося к .линии 2 связи периферийного устройства 1 в список, содержащийся в блоке 13. .

Возникновение третьей ситуации означает, что в некотором такте, код, принятый из линии 2 связи, оказывэ тся больше кода, прием которого ожидается в данном такте, и кода, принятого в предыдущем такте. В этом случае в конце такта блоком вырабатывается сигнал о неравенстве принятого и ожидаемого кодов, а блоками 10 и 11 формируются сигналы о превышении величины принятого кода над кодами, прием которого о жийаётся и принятого в предыдущем такте,

Блоком 12 при этом й:а его командлных выходах формируется сигнал, поспающий на управляющий вход блока 8 вызывающий в нем восстановление содержимого первой и второй ячеек, прествующего началу данного такта, после чего осуществляется формирование сигнала в той же последовательности, что и в случае полного совпадения принятых кодов. На выходе блока 12 формируется также сигнал, поступающий на признаковый вход блока 14 и идентифицирующий возникновение отказной ситуации в системе.

Если в очередном такте ситуация повторяется, периферийное устройство 1, дваждрл подряд передавшее свой адресный код, полностью самоотключается, и работа системы продолжается описанным выше образом, а факт отключения этого устройства регистрируется способом, рассмотренным при описании работы системы в первой ситуации,

В четвертой ситуации, при поступлении на вход какого-либо периферийного устройства 1 сигнала об изменении срстояния контролируемого объекта, этим устройством формируется сообщение стандартного формата, содержащее код-идентификатор начала сообщения, состоящий из одних единичных символов,- адрейный код этого устройства, код, несущий информацию об изменении состояния контролируемого объекта.

При этом код-индентификатор начала сообщения передается по линии 2 связи в устройство 3,где вписывается в первую ячейку блока 8 и вызывает к концу Такта появление на выходе блока 15 сигнала, по которому блок 12 формирует сигнал, запирающий до конца передачи сообщения элемент И 23 и прекращающий поступление в линию 2 связи через блок 5 синфазирующих импульсов, что исключает формирование адресных кодов всеми периферийными устройствами 1 во время передачи сообщения и, следовательно, искажение этого сообщения aдpecньuvш кодами других периферийных устройств 1; сигнал, запирающий элемент И 22, прекращающий поступление на вход блока 8 синхроимпульсов; сигнал вызывающий восстановление в . блоке 8 содержимого первой и второй ячеек, предшествующего началу передачи сообщения; сигнал, отпирающий элемент 24, в результате чего принятое сообще1 ие поступает на блок 14,.

На выходе блока 14 формируется также сигнал, поступающий на признаковый вход блока 14 и индентифицйрующий факт приема сообщения от периферийного устройства 1, адресный код которого содержится в составе принятого сообщения.

По окончании приёма сообщения, фиксируемого блоком 12по числу поступающих на его управляющий вход синфазирующих импульсов, на команд- , ных выходах этого блока восстанавлиВёнотся сигналы, обеспечивающие дальнейшую работу системы в режиме совпадения циклов.

Таким образом, устройство погволяет организовать длительность цикла oripoba периферийных устройств 1 пропорциональную числу этих устро.йств, фактически подключенных к линии связи, что обеспечивает повышение его быстродействия.

Формула изобретения

Устройство для йвода информации, содержаще .- блок сопряжения с линией

5 связи, соединенный линейными входом и выходом, соответственно, с линейными входом и, выходом устройства, группу элементов И, блок синфазирования, блок синхронизации, блок

0 управления, блок памяти , блок оконечного преобразования, блок дешифрации и первый блок сравнения, причеТл выхой блока синхрбниз ии соединен с первым входом блока сопряжения с ли5нией связи, входом блока синфазирования и тактирующим входом первого блока сравнения, первый вход которого соединен со входом дешифратора и выходом блока сопряжения с линией

0 связи, а управляющий вход - с выходом блеска синфазирования, управляющим входом блока дешифрации и первым входом блока управления, соединен, ного соответствующими командными

5 выходами с управляющими входами эле-. .. ментов И группы и входами записи и считывания .блока памяти, а вторым и третьим входами и выходом - соответственно с выходами блока дешифрации и первого блока сравнения и входом

0 признака блока оконечного .преобрзбванйя, -от л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в устройство введены.блок Ьуферной памяти и два -блока сравне-

5 кия, причем тактирующие входы Ього и третьего блоков сравнения соединены с выходом блока синхронизации и через первый элемент И группы с тактирующим входом блока

0 буферной .памяти, первый выход которого соединен,. соответственно, через второй, третий и четвертый элементы И группы с адресным и информационным входами блока памяти и адресным

5 входом блока оконечного преобразования, первые информационные входы второго и третьего блокрв сравнения подключены к выходу блока сопряжения с линией связи, входу блока бу60ферной памяти и через пятый элемент И группы к адресному входу блока оконечного преобразования, управ- ляющие входы, второго и третьего блоков сравнения соединены с выходом

65 блока инфазирования и через шестой - -,.

.......

;к««:«

V

и

Элемент И . группы со вторым входом блока спряжения с линией связи, а .яихода с четвертым и пятым входами блока управления, командный выход которого подключен к управляющему входу блока буферной памяти, вторым выходом подключенного ко второму йнфо рмационному входу третьего блока сравнения и через седьмой элемент И группы к адресному входу блока памяти, выход которого соединен с,о вторыми информационными входами первого и второго блоков сравнения и, сдрт737941

12

ветствённо, через восьмой и девятый элементы И группы - к информационному входу блока памяти и адресному входу блока оконечного преобразовани

Источники информации, принятые во внимание при экспертизе

1.Билкк Р.В. и др. Бесконтактные элементы и системы телемеханики. М., Наука , 1964.

2.Авторское свидетельство СССР №484546, кл. G 08 (J 19/28, 1974 (прототип).: .

fi

| название | год | авторы | номер документа |

|---|---|---|---|

| Система телесигнализации | 1978 |

|

SU748489A1 |

| Многоканальный телесигнализационная система с временным разделением каналов | 1974 |

|

SU519754A1 |

| Система для телесигнализации с временным разделением сигналов | 1974 |

|

SU478346A1 |

| Система для телесигнализации с временным разделением сигналов | 1974 |

|

SU484546A1 |

| Приемное устройство для системы телемеханики | 1975 |

|

SU561214A1 |

| Приемное устройство системы телесигнализации | 1979 |

|

SU773673A1 |

| Устройство для телесигнализации | 1975 |

|

SU553649A1 |

| Телемеханическая система | 1975 |

|

SU610099A1 |

| Приемное устройство системы телемеханики | 1977 |

|

SU682933A2 |

| Система для телесигнализации с временным разделением каналов | 1981 |

|

SU978177A1 |

Авторы

Даты

1980-05-30—Публикация

1977-12-13—Подача