,1

Изобретение относится к многоканальному телесигнализационному устройству с временным разделением каналов, предназначенному для передачи информации от удаленных контролируемых объектов на пункт сбора информации по проводным линиям связи.

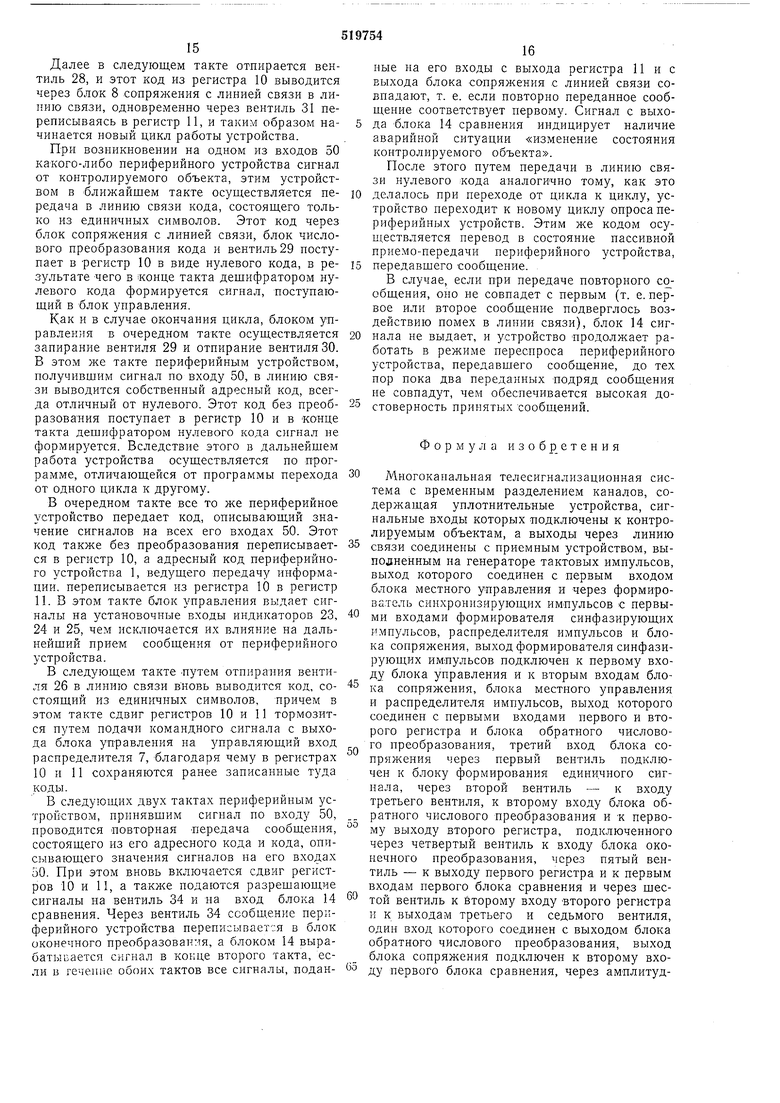

Известны системы, содержащие уплотнительные устройства, сигнальные входы которых подключены к контролируемым объектам, а выходы через линию связи - к приемному устройству, выполненному на генераторе тактовых импульсов, выход которого соединен с первым входом блока местного управления и через формирователь синхронизирующих импульсов с первыми входами формирователя синхронизирующих импульсов, распределителя импульсов и блока сопряжения. Выход формирователя синфазирующих импульсов подключен к первому входу блока управления и к вторым входам блока сопряжения, блока местного управления и распределителя импульсов, выход которого соединен с первыми входами первого и второго регистра и блока обратного числового преобразования. Третий вход блока сопряжения через первый вентиль подсоединен к блоку формирования единичного сигнала, через второй вентиль - к входу третьего вентиля, к второму входу блока обратного числового преобразования и к первому выходу второго регистра, подключенного через четвертый вентиль к входу блока оконечного преобразования, через пятый вентиль - к выходу первого регистра и к первым входам первого блока сравнения и через щестой вентиль к второму входу второго регистра и к выходам третьего и седьмого вентиля, один вход которого соединен с выходом блока обратного числового преобразования. Выход блока сопряжения подключен к второму входу первого блока сравнения, через амплитудный дискриминатор - к первому входу блока логической обработки, через восьмой вентиль непосредственно и через последовательно соединенные блок числового преобразования кода и девятый вентиль - к второму входу первого регистра, вторым выходом связанного с одним из входов дешифратора нулевого кода. Другой вход последнего подключен к первому входу блока сопряжения, а выход - к соответствующему входу блока управления, один выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу блока местного управления, к второму вы.ходу второго регистра, первый выход - к соответствующему входу блока управления, а второй - к второму входу блока логической обработки, первый выход которого соединен с соответствующим входом блока управления. Одна группа выходов блока управления подсоединена к EXOAaivi первого, второго, третьего, четвертого, г ятого, шестого, седьмого, восьмого и девятого вентилей, блока местного управления, первого блока сравнения и распределителя импульсов. Недостатком этих систем является возможность сбоев при приеме информации из-за возникновения помех в линии связи. Цель изобретения - повышение помехоустойчивости устройства. Это достигается тем, что в приемное устройство введены блоки аварийной ситуации, второй блок сравнения и дополнительные вентили. Выход первого блока сравнения соединен через десятый, одиннадцатый и двенадцатый вентили соответственно с входами первого блока аварийной ситуации, блока оконечного преобразования и блока управления, выходы первого блока аварийной ситуации - с вторыми входами одиннадцатого и двенадцатого вентилей, входы блока логической обработки соответственно через тринадцатый и четырнадцатый вентили - с четвертым входом блока памяти. Второй выход блока логической обработки подключен через пятнадцатый, шестнадцатый и семнадцатыи вентили соответственно к входам второго блока аварийной ситуации, блока оконечного преобразования и блока управления, выходы второго блока аварийной ситуации - к вторым входам шестнадцатого и семнадцатого вентилей, третий выход блока логической обработки через восемнадцатый, девятнадцатый и двадцатый вентили - к соответствующим входам третьего блока аварийной ситуации, блока оконечного преобразования и блока управления. Выходы третьего блока аварийной ситуации соединены с вторыми входами девятнадцатого и двадцатого вентилей, вход второго блока сравнения - с выходом блока сопряжения, другой - с первым выходом второго регистра, а выход - с соответствующими входами блока оконечного преобразования и блока управления, вторая группа выходов которого подключена соответственно к вторым входам десятого, тринадцатого, четырнадцатого, пятнадцатого и восемнадцатого вентилей, к соответствующим входам блоков аварийной ситуации и к третьему входу второго блока сравнения. Это позволяет в случае регистрации приемным устройством той или иной аварийной ситуации восстановить в линии связи сигналы, предшествующие приему информации о возникновении этой ситуации, и осуществить вывод информации о возникновении этой ситуации только в случае повторной ее регистрации, что значительно снижает вероятность ложной индикации устройством аварийной ситуации в результате приема из линии связи нестационарных сигналов помехи. На чертеже представлена схема многоканальной системы. Она включает в себя группу периферийных уплотнительных устройств 1 и приемное уст4ройство 2, соединенные между собой линией 3связи. Приемное устройство 2 содержит генератор 4тактовых импульсов, формирователь 5 синхронизируюших импульсов, формирователь 6 синфазирующих импульсов, распределитель 7 импульсов, блок 8 сопряжения, блок 9 числового преобразования кода, регистры 10 и И, дешифратор 12 нулевого кода, блоки 13 и 14 сравнения, блок 15 обратного числового преобразования кода, блок 16 управления, блок 17 оконечного преобразования, амплитудный дискриминатор 18, блок 19 логической обработки, блок 20 памяти с блоком 21 местного управления, блок 22 формирования единичного сигнала, индикаторы (блоки) 23, 24 и 25 аварийных ситуаций и управляемые вентили 26 - 45. Выход генератора 4 тактовых импульсов подключен к входам формирователя 5 синхронизируюш,их импульсов и блока 21 местного управления, выход формирователя синхронизируюп1,их импульсов - к входам формирователя 6 синфазирующих импульсов, распределителя 7 импульсов и к одному из входов блока 8 сопряжения с линией связи, выход формирователя синфазирующих импульсов - к одному из входов блока 21 местного управления, к тактирующему входу блока 16 управления, одному из входов распределителя 7 импульсов, управляющему входу дешифратора 12нулевого кода и к одному из входов блока 8 сопряжения с линией связи. Выход распределителя импульсов соединен с тактирующими входами регистров 10 и 11, блока 9 числового преобразования кода и блока 15 обратного числового преобразования кода. Выход блока 8 сопряжения с линией связи подсоединен к входу блока 9 числового преобразовалия кода, входу амплитудного дискриминатора 18, входам блоков 13 и 14 и чере вентиль 30 к входу регистра 10, выход блок; числового преобразования кода через вентил., 29 - к входу регистра 10, параллельный вы ход регистра 10 - к входу дешифратора ll нулевого кода. Последовательный выход этого регистра подключен к второму входу блока 13сравнения, через вентиль 31 к входу регистра 11 и через вентиль 28 к входу блока 8 сопряжения с линией связи. Параллельный выход регистра 11 соединен с адресным входом блока 20 памяти, последовательный выход этого регистра - с входом блока 15 обратного числового преобразования кода, вторым входом блока 14 сравнения, через вентиль 34- с входом блока 17 оконечного преобразования, через вентиль 27 - с входом блока 8 сопряжения с линией связи и через вентиль 32 с входом этого регистра, выход блока обратного числового преобразования кода через вентиль 33 - с входом регистра 11. Выход блока 14 связан с одним из входов блока 17 оконечного преобразования и с одним из пусковых входов блока 16 управления.

Выход амплитудного дискриминатора 18 подключен к одному из входов блока 19 логической обработки и через вентиль 44 к одному из сигнальных входов блока 20 памяти. К этому же сигнальному входу блока памяти через вентиль 45 подсоединен один из выходов блока 20 памяти, который одновременно подключен к второму входу блока 19 логической обработки, а управляющий вход блока памяти - к выходу блока 21 местного управления.

Выход блока 22 формирования единичного через вентиль 26 соединен с одним из входов блока 8 сопряжения с линией связи, выход блока 13 сравнения через вентиль 35 - с входом индикатора 23 аварийной ситуации, через вентиль 38 - с одним из пусковых входов блока 16 управления и через вентиль 41- с одним из входов блока 17 оконечного преобразования, управляющие входы вентилей 38 и 41 - с входами индикатора 23 аварийной ситуации.

Выход 46 блока 19 логической обработки подключен через вентиль 36 к входу индикатора 24 аварийной ситуации, через вентиль 39 к одному из пусковых входов блока 16 управления и через вентиль 42 к одному из входов блока 17 оконечного преобразования, управляющие входы вентилей 39 и 42 - к выходам индикатора аварийной ситуации.

Выход 47 блока логической обработки подсоединен через вентиль 37 к входу индикатора 25 аварийной ситуации, через вентиль 40 к одному из пусковых входов блока управления и через вентиль 43 к одному из входов блока 17 оконечного преобразования, управляющие входы вентилей 40 и 43 - к выходам индикатора 25 аварийной ситуации.

Выход дещифратора 12 нулевого кода, выход 48 блока логической обработки и второй выход блока 20 памяти подключены к пусковым входам блока 16 управления, выход 49 блока управления к второму сигнальному входу блока 20 памяти, командные выходы блока управления - к управляющим входам вентилей 26 - 37, 44 и 45, а также к управляющим входам блоков 13 и 14 сравнения, блока 21 местного управления и распределителя 7 и установочным входам индикаторов 23, 24 и 25 аварийных ситуаций (на чертеже эти соединения условно обозначены буквой «К).

Блок 9 числового преобразования кода обеспечивает прибавление к числовому выражению поданного на его вход кода числовой константы, например «1, блок 15 обратного числового преобразования кода - вычитание из числового выражения поданного на его вход кода той же числовой константы.

Блок 16 управления может быть выполнен в виде группы регистров сдвига, каждый из которых подключен к своему адресному входу, а выходы этих регистров объединены через комбинационную логическую схему.

Блок 20 памяти может быть изготовлен на базе оперативного запоминающего устройства

любой известной конструкции с адресной структурой.

Периферийные уплотнительные устройства 1 через свои сигнальные входы 50 связаны с

контролируемыми объектами. Эти устройства обеспечивают при поступлении на их входы через линию 3 связи индивидуальных адресных кодов генерацию в линию связи индивидуальных ответных кодов той структуры,

что и адресные, а также спорадическую передачу в линию связи сообщений о фактах изменения состояний подключенных к ним ICOHTролируемых объектов в виде последовательности кодов, содержащей код начала передачи (состоящий из одних единичных символов), собственный адресный код устройства и код, позиционно отображающий значения сигналов на сигнальных входах 50 устройства в момент передачи сообщения.

Б качестве периферийного уплотнительного устройства 1 может быть использовано, в частности, телесигнализационное устройство.

Ответные (так же, как и адресные) коды всех периферийных устройств на первой временной нозиЦии обязательно содержат единичный символ, причем эта позиция кода преобразованию в блоках числового преобразования 9 и обратного числового преобразования кода 15 не подвергается.

Работу устройства удобно рассмотреть первоначально в предположении, что сигналы на входах 50 всех периферийных устройств отсутствуют. Для удобства рассмотрения целесообразно также считать, что нодключенные к

линии связи периферийные устройства образуют полный комплект, характеризующийся тем, что ответный код каждого устройства отличается от адресного кода этого устройства на величину, равную значению числовой константы, используемой в блоке числового преобразования кода, и, кроме того, является адресным кодом другого перифери 1ного устройства, а коды, состоящие из одних единичных символов и одних нулевых символов не

являются адресными нн для одного из перисрерийных устройств.

Генератором 4 тактовых импульсов приемного устройства 2 осуществляется постоянная генерация последовательности импульсов, на основе которой формирователями синхронизирующих импульсов 5 и синфазирующих импульсов 6 осуществляется генерация носледовательностей соответствующих импульсов, выводимых через блок 8 сопряжения с линией связи в линию связи.

При этом синхронизирующие импульсы используются для ограничения временных позиций передаваемых по линии связи кодов, сипфазирующие импульсы служат для временного разделения этих кодов, причем интервал между двумя соседними синфазирующими импульсами образует такт работы устройства.

Если, как это было оговорепо, по линии связи передается неискаженная последовательность адресных (ответных) кодов, на пуско вые входы блока 16 управления никаких сигналов не ноступает и сигналы на его командных выходах таковы, что вентили 29, 31, 35, 36, 37 и 45 открыты, на управляющих входах блока 13 сравнения и блока 21 местного унравления присутствуют разрешающие сигналы, на управляющем входе блока 14 сравнения - запрещающий сигнал, остальные вентили закрыты, а сигнал на выходе 49 блока 16 отсутствует. При этом индикаторы 23, 24 и 25 находятся в таком состоянии, что на управляющих входах вентилей 38, 39 и 40 присутствуют разрещающие сигналы, а на входах вентилей 41, 42 и 43 - запрещающие. Пусть в некоторый момент времени по лиНИИ связи передается адресный код одного из периферийных устройств. Этот код одновременно вводится во все периферийные устройства, а также через блок 8 сопряжения с линией связи в блок 9 числового преобразования кода, откуда, увеличенный на величину числовой константы, через открытый вентиль 29 вводится в регистр 10, сдвиг которого обеспечивается подачей на его тактирующий вход импульсов с выхода распределителя 7. Таким образом, к концу передачи данного кода по линии связи в регистре 10 оказывается записанным код, передача которого по линии связи ожидается в следующем такте. Одновременно код, ранее записанный в регистре 10, т. е. равный коду, передаеваемому по линии связи в данном такте,через открытый вентиль 31 переписывается в регистр 11, т. е. к концу такта в регистре 11 оказывается записанным адресный код периферийного устройства, которое должно отвечать в следующем такте. Очередным синфазирующим импульсом с выхода формирователя 6, определяющим началом нового такта, осуществляется запуск блока 21 местного управления, который подает сигнал считывания в блок 20 памяти. При этом происходит считывание информации из ячейки памяти с адресом, равным коду, записанному в регистре 11, т. е. равным адресному коду периферийного устройства, ответ которого ожидается в этом такте. В ней содержится два идентификатора, причем зпачение одного из них (например, 1-го) вводится в блок 19 логической обработки (этот идентификатор равен «1, если данное периферийное устройство отвечало в предыдущем цикле опроса, и «О в противном случае), а значение другого (2-го) идентификатора содержит «О, если данное периферийное устройство отвечало правильно в предыдущем цикле опроса, и «1 в противном случае. Далее периферийным устройством 1, принявщим в предыдущем такте свой адресный код, осуществляется генерация в линию связи ответного кода, который, как и ранее, через блок сопряжепия 8 с линией связи и блок 9 числового преобразования кода поступает в регистр 10. Первый символ кода (всегда единичный, как это было отмечено) подается в амплитудный дискриминатор 18, с выхода которого единичный символ, свидетельствующий о наличии сигнала на выходе дискриминатора 18, поступает в блок 19 логической обработки. При наличии единичных сигналов на обоих своих входах блок логической обработки не вырабатывает никаких сигналов ни на одном из своих выходов 46, 47 и 48. Блоком 16 управления также удерживается нулевой сигнал на выходе 49, в результате чего при подаче на управляющий вход блока 20 памяти сигнала записи с выхода блока 21 местного управления в его ячейку с адресом, равным адресному коду, отвечающего в этом такте периферийного устройства записывается «1 с собственного выхода через вентиль 45 и «О с выхода 47 блока управления, т. е. значения обоих идентификаторов не изменяется по сравнению с предыдущими. Код, генерируемый периферийным устройством, поступает также через блок 8 сопряжения с линией связи на один из числовых входов блока 13 сравнения, на другой вход которого одновременно подается код с выхода регистра 10. При этом, если периферийное устройство, отвечает правильно, оба этих кода совпадают, и блоком 13 сравнения никаких сигналов не вырабатывается. Код с выхода регистра 10 через открытый вентиль 31 переписывается, как и в предыдущем такте, в регистр 11. Таким образом происходит работа устройства, когда в каждом последующем такте по линии связи передается код, отличающийся от кода, переданного в предыдущем такте, на числовую величину, равную числовой константе, используемой для преобразования кодов в блоке 9 преобразования кода, т. е. когда никакой информации через периферийные устройства от контролируемых объектов не поступает, а все периферийные устройства функционируют нормально. В случае отсутствия ответа от какого-либо периферийного устройства (вызванного отказом этого устройства, нарушением линии связи или отключением этого устройства от линии связи) в соответствующем такте на первой временной позиции сигнал на вход амплитудного дискриминатора 18 не поступает. С выхода амплитудного дискриминатора 18 на вход блока 19 логической обработки подается нулевой сигнал, в то время как с выхода блока 20 памяти на другой его вход проходит единичное значение идентификатора включенного состояния данного периферийного устройства. Блок логической обработки вырабатывает сигнал на его выходе 46, поступающий через ткрытые вентили 36 и 39 на вход индикатора 4, аварийной ситуации п один из пусковых ходов блока 16 управления. При этом передим фронтом этого сигнала осуществляется апуск блока управления, а задним фроном - взведение индикатора 24, сигналами с ыходов которого запирается вентиль 39 и отрывается вентиль 42. Единичный сигнал с выхода блока 20 памяти через вентиль 45 поступает на его сигнальный вход и записывается в него после поступления на управляющий вход блока памяти сигнала записи с выхода блока 21 местного управления по-прежнему в виде единичного значения соответствующего идентификатора. Блок 16 управления после получения пускового сигнала с выхода 46 блока 19 логической обработки выдает командные сигналы, отпирающие в данном такте вентили 26 и 32 и запирающие вентили 31, 35, 36, 37. В результате в данном такте осуществляется вывод от формирователя единичного сигнала через блок 8 сопряжения с линией связи в линию 3 связи кода, состоящего только из единичных символов, вход регистра 11 отключается от выхода регистра 10 и подключается к собственному выходу, а входы индикаторов 23, 24 и 25 блокируются. Одновременно на управляющие входы блоков сравнения 13 и местного управления 21 подаются запрещающие сигналы, исключающие их работу в данном такте. К концу такта код, состоящий из единичных символов из линии связи через блок 8 сопряжения с линией связи и блок 9 числового преобразования кода переписывается в регистр 10, преобразуясь при этом в нулевой код, а адресный код периферийного устройства, ответ которого не был получен в данном такте, восстанавливается в регистре 11. При этом в момент формирования очередного синфазирующего импульса, определяющего начало нового такта, на выходе дещифратора 12 нулевого кода формируется сигнал, поступающий на пусковой вход блока 16 управления, и совместно с синфазирующим импульсом, приходящим на тактирующий вход блока управления с выхода формирователя, осуществляющий переключение командных сигналов на выходе блока управления таким образом, что в очередном такте вентили 26 и 29 запираются, а вентиль 30 отпирается. Остальные командные сигналы в этом такте не изменяются. Таким образом в пределах этого такта по линии связи не передается никаких кодов (точнее передается нулевой код), поскольку на переданный в предыдун;ем такте единичный код не отвечает ни одно периферийное устройство, а вентили 26, 27, 28. связывающие выходы приемного устройства 2 с линией 3 связи, закрыты. При этом нулевой код через блок 8 сопряжения с линией связи и вентиль 30 без преобразования поступает в регистр 10, а адресный код не ответившего периферийного устройства вновь восстанавливается в регистре 11. В конне такта очередным синфазирующим импульсом опращивается дещифратор 12 нулевого кода, сигнал с выхода которого вновь гюдается на пусковой вход блока управления и совместно с синфазирующим импульсом, поступающим на тактирующий вход этого блока. переключает командные сигналы на выходах этого блока таким образом, что вентиль 30 запирается, а вентили 29 и 27 отпираются. В результате в очередном такте в линию 3 связи через блок 8 сопряжения с линией связи и вентиль 27 из регистра 11 выводится адресный код периферийного устройства, не ответившего ранее, причем код, поступая через блок 9 числового преобразования кода и вентиль 29 в регистр 10, преобразуется в нем в ответный код этого устройства. В регистре же 11 к концу такта вновь восстанавливается адресный код этого же устройства. Таким образом, в этом такте в линии связи и в регистрах ЮиП полностью восстанавливается ситуация, предшествующая моменту регистрации отсутствия ответа от данного периферийного устройства. При этом блоком 16 управления снимается запрещающий сигнал с управляющего входа блока 21 местного управления. Если теперь в очередном такте на месте первого символа ответного кода периферийного устройства в приемное устройство 2 вновь поступает нулевой символ, на выходе 46 блока 19 логической обработки вновь формируется сигнал, который на этот раз через вентиль 42 подается на вход блока 17 оконечного преобразования, индицируя факт регистрации устройством ситуации «периферийное устройство не отвечает. При этом блоком управления в этом такте вентили 32 и 45 запираются, а вентили 28, 31, 34 и 44 отпираются, в результате чего в блок 20 памяти с выхода амплитудного дискриминатора 18 записывается нулевое значение идентификатора включенного состояния периферийного устройства, в линию связи КЗ регистра 10 выводится ответный код периферийного устройства, не ответившего в данком такте, являющийся адресным кодом другого периферийного устройства. Адресный код не ответившего периферийного устройства переписывается в блок 17 оконечного преобразования, а адресный код периферийного устройства 1, которое должно отвечать в следующем такте, - из регистра 10 в регистр 11. Блок управления обеспечивает также подачу обнуляющего сигнала на установочные входы всех индикаторов 23, 24 и 25 аварийных ситуаций, после чего в очередном такте им восстанавливается исходное значение всех командных сигналов, и устройство продолжает свою работу о описанном режиме, когда никакой информации от периферийных устройств в приемное устройство не поступает. Блоком 17 оконечного преобразования осуществляется либо визуальная индикапия ввеенных в него данных, либо их преобразование вид, удобный для дальнейщего использования в каких-либо регистрирующих устройствах. Если же подтверждения возникшей аварийной ситуации не наступает (периферийное устройство отвечает при его переспросе правильно) сигнал на выходе 46 блока 19 логической обработки не вырабатывается и соответственно не поступает через вентиль 42 в блок оконечкого преобразования, чем исключается прием зтпм блоком кода с выхода регистра 11. В дальнейшем, в последующих циклах работы устройства, в случае повторного отсутствия сигналов с выхода данного периферийного устройства в момент прохождения первой временной позиции кода в блок 19 логической обработки с выхода блока 20 памяти подается уже нулевое значение идентификатора включенного состояния данного периферийного устройства, что в сочетании с нулевым значением сигнала на выходе амплитудного дискриминатора 18 вызвает появление сигнала на выходе 47 блока 19 логической обработки. Этот сигнал, попадая на соответствующий пусковой вход блока управления, в свою очередь, приводит к образованию на его командном выходе сигнала, отпирающего лищь вентиль 28. Таким образом, каждый раз осуществляется замещение отсутствующего ответного кода в линии связи кодом, выводимым из регистра 10, а в блок 17 оконечного преобразования информация об отключениях данного нериферийного устройства, являющаяся теперь избыточной, не поступает. Если в одном из последующих циклов работы устройства данным периферийным устройством вновь будет выведен ответный код в линию связи (аварийная ситуация устранена), на первой временной позиции кода на выходе амплитудного дискриминатора 18 возникает единичный сигнал, который в сочетании с нуле вым значением идентификатора, поступающего из блока 20 памяти, вызывает появление сигнала на выходе 48 блока 19 логической обработки. Этот сигнал поступает через открытый вентиль 40 на пусковой вход блока управления и на вход индикатора 25 аварийной ситуации, который взводится задним фронтом этого сигнала, отпирая вентиль 43 и запирая вентиль 40. Дальнейщая работа устройства происходит следующим образом. Сигналами с командных выходов блока управления запираются вентили 35, 36 и 37, фиксируя состояния индикаторов 23, 24 и 25, отпирается вентиль 26, обеспечивая вывод в линию связи единичного кода от формирователя единичного сигнала, а также отпирается вентиль 32 и запирается вентиль 31, обеспечивая восстановление к концу такта адресного кода отвечающего периферийного устройства в регистре 11. Далее, как и в описанном случае прекращения ответа периферийного устройства, с помощью дещифратора 12 нулевого кода индицируется отсутствие передачи информации по линии связи после прохождения по ней единичного кода, а затем из регистра 11 в линию связи выводится адресный код периферийного устройства, ответ которого был ранее принят. В случае повторного ответа этого устройства сигнал с выхода 48 блока 19 логической обраотки через вентиль 43 поступает в блок конечного преобразования, индицируя ситуаию «периферийное устройство включено. В локе 20 памяти путем отпирания вентиля 44 восстанавливается единичное значение иденификатора включенного состояния периферийного устройства, а адресный код этого устройства из регистра 11 через вентиль 34 подается в блок 17 оконечного преобразования, после чего передается обнуляющий сигнал ,на установочные входы индикаторов 23, 24 и 25, а на командных выходах блока управления восстанавливается исходная комбинация командных сигналов. Если же обнаруженная ранее ситуация («периферийное устройство отречает) не подтвердилась, сигнал на выходе 48 блока логической обработки не возникает и не поступает через вентиль 43 на вход блока 17 оконечного преобразования, который вследствие этого не принимает введенный в него из регистра 11 адресный код. При этом блоком управления отпирается вентиль 28, через который ответный код отключенного периферийного устройства выводится из регистра 10 в линию связи, после чего работа устройства продолжается уже онисанным порядком. В случае, если какое-либо периферийное устройство отвечает неправильным кодом (но содержащим «1 на первой временной позиции), этот факт индицируется в приемном устройстве сигналом с выхода блока 13 сравнения, обнаруживающим несовпадение кодов, поступающих на его входы с выходов блока 8 сопряжения с линией связи и регистра 10. Поскольку этот факт может быть окончательно установлен блоком 13 лишь в конце такта, в регистре 11 к этому моменту оказывается зэписанным правильный ответный код перифс рийного устройства, ответившего в данно случае неверно. Сигнал с выхода блока 13 сравнения через вентиль 38 поступает на пусковой вход блока 16 управления и через вентиль 35 на вход индикатора 23 аварийной ситуации, который взводится задним фронтом этого сигнала, открывая вентиль 41 и запирая вентиль 38. Далее, в следующем такте блоком управления, аналогично предыдущим случаям, осуществляется отпирание вентиля 26 и вывод в линию связи единичного кода, который «глущит в линии связи ответный код периферийного устройства, который может возникнуть там, если какое-либо из периферийных устройств воспримет неправильный ответный код периферийного устройства, переданный в предыдущем такте, как свой адресный код. В этом же такте за счет включения вентиля 33 и выключения вентиля 31 ответный код периферийного устройства, ответившего неверно, передается с выхода регистра 11 через блок 15 обратного числового преобразования на его же вход, благодаря чему к концу такта в регистре 11 восстанавливается адресный код этого периферийного устройства,

В следующем такте, как и в предыдущих случаях, дещифратором 12 нулевого кода анализируется наличие передачи информации по линии связи после прохождения по ней единичного кода и в случае отсутствия, передачи сигнал с выхода дешифратора 12 -поступаетна вход блока управления. После этого в следующем такте в линию связи из регистра И через вентиль 27 и блок 8 сопряжения с линией связи выводится адресный код периферийного устройства, ответившего неверно, и этот же КОД восстанавливается в конце такта в регистре 11, а в регистр 10 через вентиль 29 и блок чистового преобразования кода 9 записывается ответный код этого периферийного устройства.

Если в очередном такте ответный код периферийного устройства, переданный по линии связи 3, и его ответный код, записанный в ре-, гистре 10 вновь окажутся несовпадающими, блоком 13 сравнения выдается сигнал, поступающий через вентиль 41 в блок 17 оконечного Преобразования и индицирующий факт обнаружения аварийной ситуации «периферийное устройство отвечает неверно. Адресный код этого устройства из регистра 11 выводится в блок оконечного преобразования, а на установочные входы индикаторов 23, 24 и 25 блоком управления подается сигнал, осуществляющий их установку в исходное состояние. Кроме того, блоком управления 16 формируется единичный сигнал на выходе 49, в результате чего при подаче на управляющий вход блока 20 памяти сигнала записи, в ячейку с адресом, равным адресному коду периферийного устройства, ответивщего неверно, записывается единичное значение второго идентификатора.

Если же, как и ъ описанных ранее случаях, аварийная ситуация не подтверждается, т. е. коды, поданные на входы блока. 13 сравнения, оказываются одинаковыми, сигнал на его выходе не вырабатывается и не ноступает в блок 17 оконечного преобразования. В результате адресный код ответившего неверно периферийного устройства этим блоком не принимается, а блоком управления в очередном такте осуществляется установка индикаторов 23, 24 .и 25 в исходное состояние, после чего работа устройства продолжается описанным порядком. При этом в блоке 20 памяти сохраняется нулевое значение второго идентификатора.

В циклах, последующих за циклом, в котором зарегистрирован неверный ответ одного из периферийных устройств, в такте, в котором должен быть получен ответный код этого ус5;ройства, с выхода блока памяти в блок управления поступает единичное значение второго идентификатора, в результате чего на командных выходах блока управления вырабатываются сигналы, отпирающие в этом такте вентиль 26 и отключающие блок 13 сравнения. При этом в линию свя)и от формирователя 22 единичного кода через вентиль 26 и блок 8 сопряжения с линией связи выводится код, состоящий из одних единичных символов и «заглзшающий в линии связи неверный ответный код отказавшего периферийного устройства. Правильный ответный код этого устройства переписывается в этом такте из регистра

10в регистр 11.

В следующем такте вентили 26, 29 и 31 запираются, а вентили 30 и 32 отпираются, в результате чего по линии связи передается код, содержащий только нулевые символы, этот код через вентиль 30 записывается в регистр 10, а в регистре 11 сохраняется правильный ответный код отказавшего периферийного устройства. Дешифратор 12 нулевого кода в момент формирования очередного синфазирующего импульса анализируется наличие нулевого кода в регистре 10, после чего с его выхода поступает сигнал в блок управления, которым в

очередном такте запирается вентиль 30 и отпираются вентили 27 и 29. В результате в линию связи выводится из регистра 11 ответный код отказавшего периферийного устройства, этот код через блок 9 числового преобразования кода и вентиль 29 поступает в регистр 10, преобразуясь при этом в ответный код очередного периферийного устройства, а в регистре

11по-прежнему сохраняется ответный код отказавшего периферийного устройства.

В следующем такте все вентили возвращаются в исходное состояние. Таким образом, устройством осуществляется гащение неверных ответных кодов, отказавших, но не отключенных от линий связи периферийных устройств без вывода каждый раз в блок оконечного преобразования информации об отказе этих устройств.

В конце каждого цикла работы устройства

периферийным устройством, отвечающим в цикле последним, выводится в линию связи ответный код, состоящий из одних единичных символов. Этот код, постуная через блок 8 сопряжения с линией связи, блок 9 числового

преобразования кода 9 и вентиль 29 в регистр 10 преобразуется в нем в нулевой код. В конце такта очередным синфазирующим импульсом опрашивается дешифратор 12 нулевого кода, сигнал с выхода которого поступает

в блок управления.

В очередном такте блоком управления запирается вентиль 29 и отпирается вентиль 30 нулевой код, возникающий в связи вследствие отсутствия ответов от периферийных устройств, записывается без преобразования в регистр 10 и дешифратором 12 вновь вырабатывается сигнал, поступающий в блок управления. В очередном такте блоком управления проводится обратное переключение вентилей 29 и 30, и нулевой код, вновь переданный по линии связи, записывается в регистр 10 через блок 9 числового преобразования кода в виде адресного кода периферийного устройства,

опрашиваемого в каждом цикле первым. Далее в следующем такте отпирается вентиль 28, и этот код из регистра 10 выводится через блок 8 сопряжения с линией связи в линию связи, одновременно через вентиль 31 переписываясь в регистр 11, и таким образом начинается новый цикл работы устройства. При возникновении на одном из входов 50 какого-либо периферийного устройства сигнал от контролируемого объекта, этим устройством в ближайшем такте осуществляется передача в линию связи кода, состоящего только из единичных символов. Этот код через блок сопряжения с линией связи, блок числового преобразования кода и вентиль 29 поступает в регистр 10 в виде нулевого кода, в результате чего в «овце такта дешифратором нулевого кода формируется сигнал, поступающий в блок управления. Как и в случае окончания цикла, блоком управления в очередном такте осуществляется запирание вентиля 29 и отпирание вентиля 30. В этом же такте периферийным устройством, получившим сигнал по входу 50, в линию связи выводится собственный адресный код, всегда отличный от нулевого. Этот код без преобразования поступает в регистр 10 и в ко-нде такта дешифратором нулевого кода сигнал не формируется. Вследствие этого в дальнейщем работа устройства осуществляется по программе, отличающейся от программы перехода от одного цикла к другому. В очередном такте все то же периферийное устройство передает код, описывающий значение сигналов на всех его входах 50. Этот код также без преобразования переписывается в регистр 10, а адресный код периферийного устройства 1, ведущего передачу информации, переписывается из регистра 10 в регистр И. В этом такте блок управления выдает сигналы на установочные входы индикаторов 23, 24 и 25, чем исключается их влияние на дальнейший прием сообщения от периферийного устройства. В следующем такте -путем отпирания вентиля 26 в линию связи вновь выводится код, состоящий из единичных символов, причем в этом такте сдвиг регистров 10 и 11 тормозится путем подачи командного сигнала с выхода блока управления на управляющий вход распределителя 7, благодаря чему в регистрах 10 и И сохраняются ранее записанные туда коды. В следующих двух тактах периферийным устройством, принявшим сигнал по входу 50, проводится повторная -передача сообщения, состоящего из его адресного кода и кода, описывающего значения сигналов на его входах 50. При этом вновь включается сдвиг регистров 10 и И, а также подаются разрешающие сигналы на вентиль 34 и на вход блока 14 сравнения. Через вентиль 34 сообщение периферийного устройства переписывается в блок оконечного преобразования, а блоком 14 вырабатывается сигнал в конце второго такта, если в течение обоих тактов все сигналы, поданные на его входы с выхода регистра И и с выхода блока сопряжения с линией связи совпадают, т. е. если повторно переданное сообщение соответствует первому. Сигнал с выхода блока 14 сравнения индицирует наличие аварийной ситуации «изменение состояния контролируемого объекта. После этого путем передачи в линию связи нулевого кода аналогично тому, как это делалось при переходе от цикла к циклу, устройство переходит к новому циклу опроса периферийных устройств. Этим же кодом осуществляется иеревод в состояние пассивной приемо-передачи периферийного устройства, передавшего сообщение. В случае, если при передаче повторного со; общения, оно не совпадет с первым (т. е. первое или второе сообщение подверглось воЗ действию помех в линии связи), блок 14 сигнала не выдает, и устройство продолжает работать в режиме переспроса периферийного устройства, передавшего сообшение, до тех пор пока два переданных подряд сообщения не совпадут, чем обеспечивается высокая достоверность принятых сообщений. Формула изобретения Многоканальная телесигнализационная система с временным разделением каналов, содержащая уплотнительные устройства, сигнальные входы которых подключены к контролируемым объектам, а выходы через линию связи соединены с приемным устройством, выполненным на генераторе тактовых импульсов, выход которого соединен с первым входом блока местного управления и через формирователь синхронизирующих импульсов с первыми входами формирователя синфазирующих импульсов, распределителя импульсов и блока сопряжения, выход формирователя синфазирующих импульсов подключен к первому входу блока управления и к вторым входам блока сопряжения, блока местного управления и распределителя импульсов, выход которого соединен с первыми входами первого и второго регистра и блока обратного числового преобразования, третий вход блока сопряжения через первый вентиль подключен к блоку формирования единичного сигнала, через второй вентиль - к входу третьего вентиля, к второму входу блока обратного числового преобразования и к первому выходу второго регистра, подключенного через четвертый вентиль к входу блока оконечного преобразования, через пятый вентиль - к выходу первого регистра и к первым входам первого блока сравнения и через шестой вентиль к второму входу второго регистра и к выходам третьего и седьмого вентиля, один вход которого соединен с выходом блока обратного числового преобразования, выход блока сопряжения подключен к второму входу первого блока сравнения, через амплитудный дискриминатор - к первому входу блока логической обработки, через восьмой вентиль непосредственно и через последовательно соединенные блок числового преобразования кода и девятый вентиль - к второму входу первого регистра, второй выход которого соединен с одним из входов дешифратора пулевого кода, другой вход которого подключен к первому входу блока сопряжения, а выход-к соответствующему входу блока управления, один выход которого соединен с первым входом блока памяти, второй вход которого подключен к выходу блока местного управления, к второму выходу второго регистра, первый выход - к соответствующему входу блока управления, а второй - « второму входу блока логической обработки, первый выход которого соединен с соответствующим входом блока управления, одна группа выходов Kofoporo подключена к входам первого, второго, третьего, четвертого, пятого, щестого, седьмого, восьмого и девятого вентилей, блока местного управления, первого блока сравнения и распределителя импульсов, отличающаяся тем, что, с пелью повышения надежности работы системы, в нее в приемное устройство введены блоки аварийной ситуации, второй блок сравнения и дополнительные вентили, причем выход первого блока сравнения соединен через десятый, одиннадцатый и двенадцатый вентили соответственно с входами первого блока аварийной ситуации, блока оконечного преобразования и блока управления, выходы первого блока аварийной ситуации подключены к вторым входам одиннадцатого II двенадцатого вентилей, входы блока логической обработки соответственно через

тринадцатый и четырнадцатый вентили соединены с четвертым входом блока памяти, второй выход блока логической обработки подключен через пятнадцатый, шестнадцатый и семнадцатый вентили соответственно к входам

второго блока аварийной ситуации, блока оконечного преобразования и блока управления, выходы второго блока аварийной ситуации соединены с вторыми входами шестнадцатого и семнадцатого вентилей, третий выход блока

логической обработки подключен через восемнадцатый, девятнадцатый и двадцатый вентили к соответствующим входам третьего блока аварийной ситуации, блока оконечного преобразования и блока управления, выходы

третьего блока аварийной ситуации соединены с вторыми входами девятнадцатого и двадцатого вентилей, вход второго блока сравнения подключен к выходу блока сопряжения, а другой - к первому выходу второго регистра,

а выход соединен с соответствующими входами блока оконечного преобразования и блока управления, вторая группа выходов которого подключена соответственно к вторым входам десятого, тринадцатого, четырнадцатого, пятнадцатого и восемнадцатого вентилей, к соответствующим входам блоков аварийной ситуации и к третьему входу второго блока сравнения.

50 .У,

Rl

so f r

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для телесигнализации с временным разделением сигналов | 1974 |

|

SU484546A1 |

| Система для телесигнализации с временным разделением сигналов | 1974 |

|

SU478346A1 |

| Приемное устройство системы телемеханики | 1976 |

|

SU596996A1 |

| Приемное устройство для системы телемеханики | 1975 |

|

SU561214A1 |

| Система телесигнализации | 1978 |

|

SU748489A1 |

| Система для телесигнализации с временным разделением сигналов | 1974 |

|

SU518789A1 |

| Телемеханическая система | 1975 |

|

SU610099A1 |

| Приемное устройство системы телесигнализации | 1979 |

|

SU773673A1 |

| Приемное устройство системы телемеханики | 1977 |

|

SU682933A2 |

| Телемеханическая система с временным разделением каналов | 1976 |

|

SU616648A1 |

Авторы

Даты

1976-06-30—Публикация

1974-09-18—Подача