(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремального из @ чисел | 1984 |

|

SU1171779A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1795449A1 |

| Устройство для прямого и обратного преобразования кода системы остаточных классов в двоичный код | 1982 |

|

SU1075254A1 |

| Устройство для сравнения чисел | 1979 |

|

SU798813A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для сравнения п двоичных чисел | 1979 |

|

SU840888A1 |

| Устройство для обработки статистической информации | 1986 |

|

SU1320815A2 |

| Устройство для выделения экстремального из -разрядных двоичных чисел | 1978 |

|

SU752326A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств дискретной автоматики и цифровых вычислительных машин.

Известны устройства для сравнения двоичных чисел, содержащие ( fj + 1) поразрядных блоков сравнения, три. группы по ( fl + 1) элементов ИЛИ-НЕ, элементы ИЛИ, переключатель, причем прямые входы поразрядных блоков сравнения связаны со ВХОД11ЫМИ шинами устройства, а инверспые - с выходами элементов ИЛИ-НЕ тех |же разрядов,: а.соответствуюшие выходы поразрядных блоков сравнения /. -ых разрядов, ГА t О, 1, 2. . . tj подключены через переключатель к входам первой и второй группы элементов ИЛИ-НЕ и к .. входам переносов 0,1 . . .(/ -1)ой поразрядных блоков сравнения.

Однако известные устройства не позволяют наряду с формированием сигнала резу тата сравнения получить код экстремалЬ ного числа.

Здиль изобретения - расширение класса решаемых задач.

В предлагаемом устройстве выходы элементов ИЛИ-НЕ первой и второй группы подключены к входам элементов ИЛИ-Н третьей группы, а соответствующие выходы поразрядных блоков сравнения соединены с входами первого и второго элементов ИЛИ.

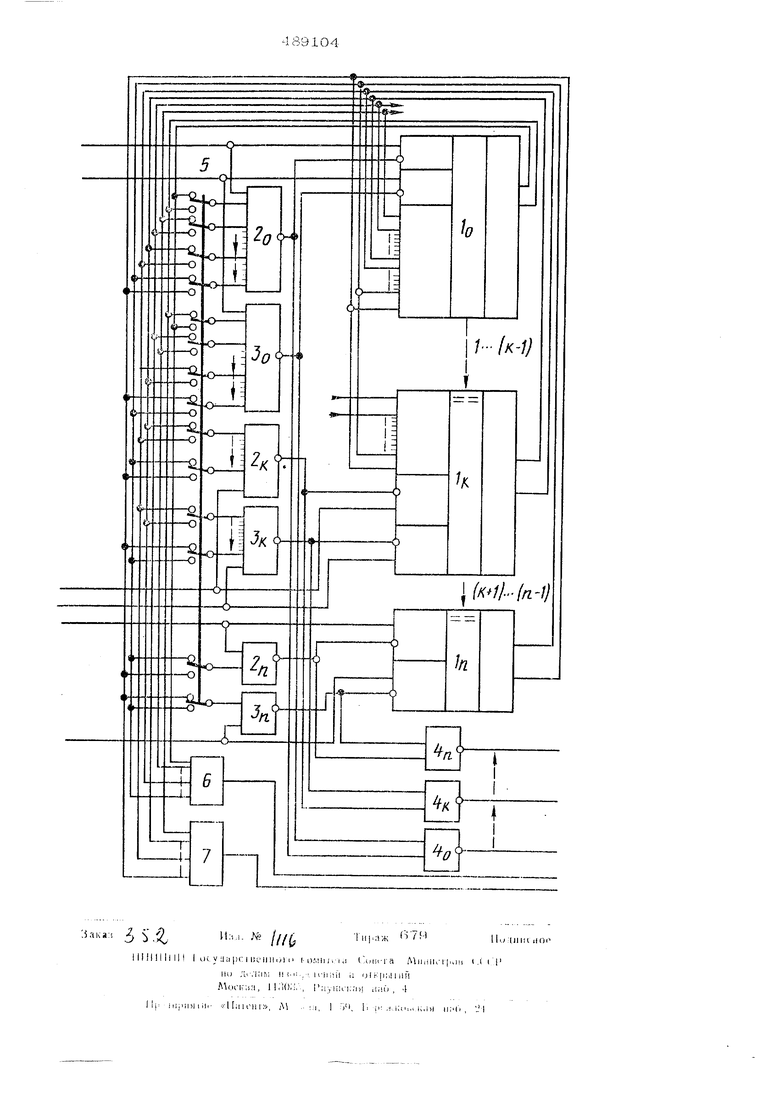

На чертеже приведена блок-схема устройства.

Устройство содержит (f,+ 1) поразрядных блоков сравнения IQ,.., Il,, . . Ifl,

элементы ИЛИ-НЕ 2,

П-k

ПО

4jj, переключатель 5, элементы ИЛИ 6 и 7.

Устройство работает следующим об разом.

Во всех разрядах, кроме К-го срав- ниваемые числа А и В равны между собой. В разряде, К возможны три различных состояния выходов поразрядного блока

сравнения 1 к: , , , при чем Б зависимости от положения переключателя 5 на выходак элементов ИЛИНЕ . . .4ц . . , 4j . . . 4j формируются коды наименьшего или наибольшего из чисел. Формирование выходных кодов во всех остальных разрядах осуществляется аналогично.

Рассмотрим работу схемы формирования сигналов выходного кода для случая, когда в одном из разрядов, например нулевом, выполняется соотношение АоЯЗо, а в любом старшем разряде, например, К-ом, . В этом случае на выходе поразрядно) блока сравнения 1к имеем 1 и О, а на выходе поразрядного блока сравнения 1о: О, О, так как сигнал блокируется сигналом . Формирование выходного кода для К-го разряда элементами ИЛИ-НЕ 2к, Зк, 4к происходит аналогично описанному. В разряде О при установке переключателя 5 в положение I (выдача кода меньшего числа) на выходе элементов ИЛИ-НЕ 2о и Зо единичные и нулевые сигналы, так как АО 1 (AoJBo) и 1.

В связи с этим на выходе элемента 4о фop 1 lpyeтcя сигнал логической единицы. Таким образом на выходе этого элемента формируется код меньи1е- го числа.

При установке переключателя 5 в по- лолсениеЯ (выдачи кода большего числа) на входах злe leнтoв ИЛИ-НЕ 2о и Зо устанавливаются сигналы АО 1, Во О 1, О и, следовательно.

на кх выходах сигналы логического нуля и единицы соответственно. При этом на

выходахэлементов 4о и 4к формируется

код большего числа. Аналогично схема работает при различных сочетаниях КОДОЕ во всех остальных разрядах сравниваемы чисел.

Если на выходе устройства необходима получить код только большего или только меньшего числа, то переключатель 3 не устанавливается.

Предмет изобретения

Устройство для сравнения двоичных чисел, содержащее (П+i) поразрядных блоков сравнения, три группы по (/ +1) элементов ИЛИ-НЕ, элементы ИЛИ, перек

лючатель, причем прямые входы поразрядных блоков сравнения связаны со входными шинами устройства, а инверсные - с выходами элементов ИЛИ-НЕ тех же разрядов, а соответствующие выходы порапрядных блоков сравнения /-ых разрядов, где I О, i, 2 . . . fi , подключены через переключатель ко входам первой и второй групп элементов ИЛИ-НЕ и ко входам переносов 0,1 ...... (i-l)-ro поразрядных блоков сравнения, отличию ш е 8 с я тем, что, р целью расширения класса решаемых задан, выходы элементов ИЛИ-НЕ первой и второй трупп подключены к входам элементов ИЛИ-НЕ третьей группы, а соответствующие выходь поразрядных блоков сравнения соединены с входами nepBoj o и второго элементов ИЛИ.

Авторы

Даты

1975-10-25—Публикация

1973-07-02—Подача