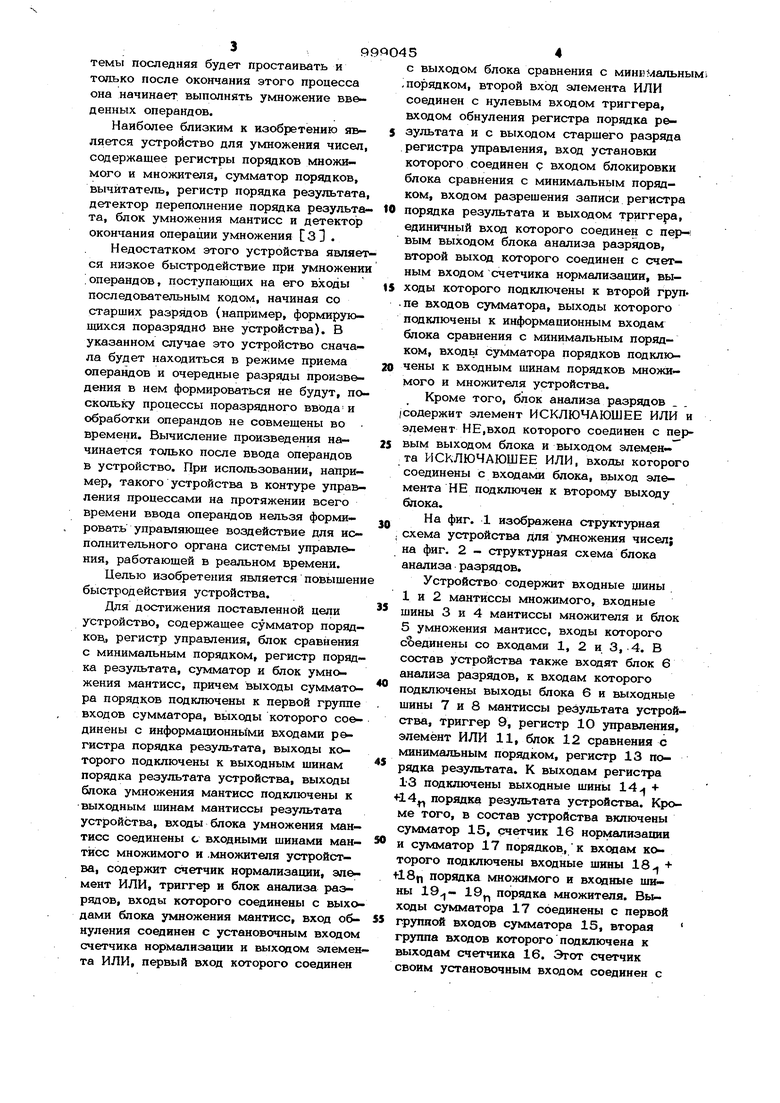

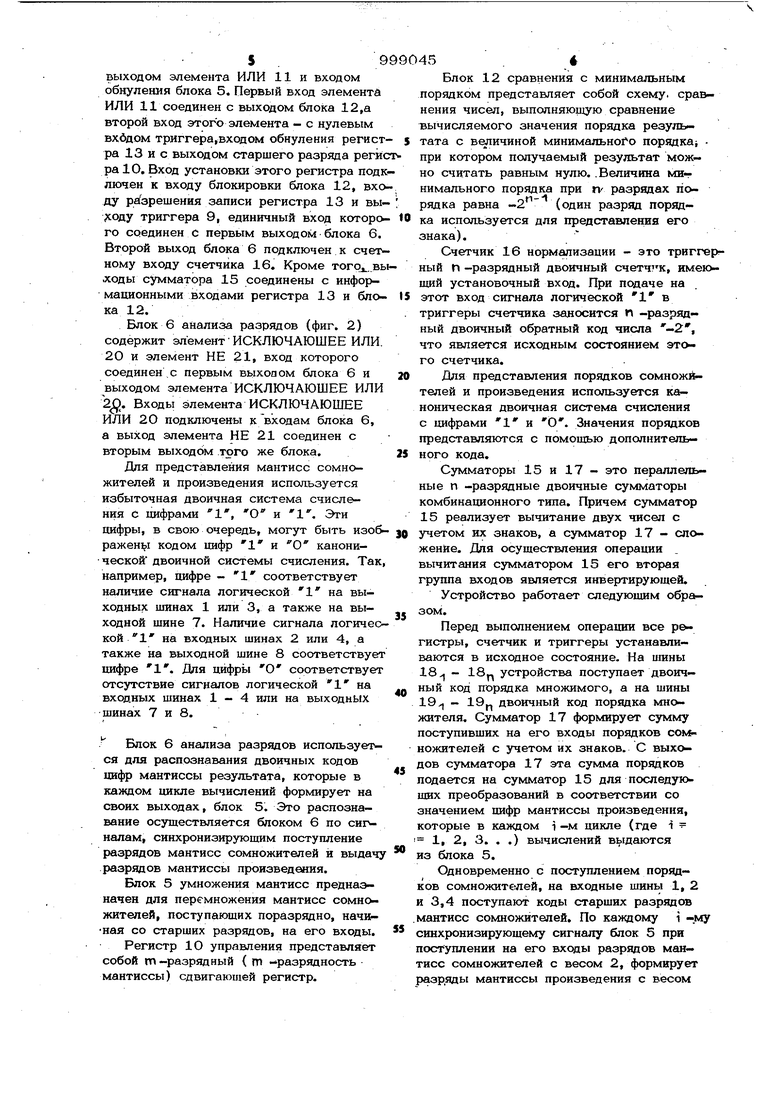

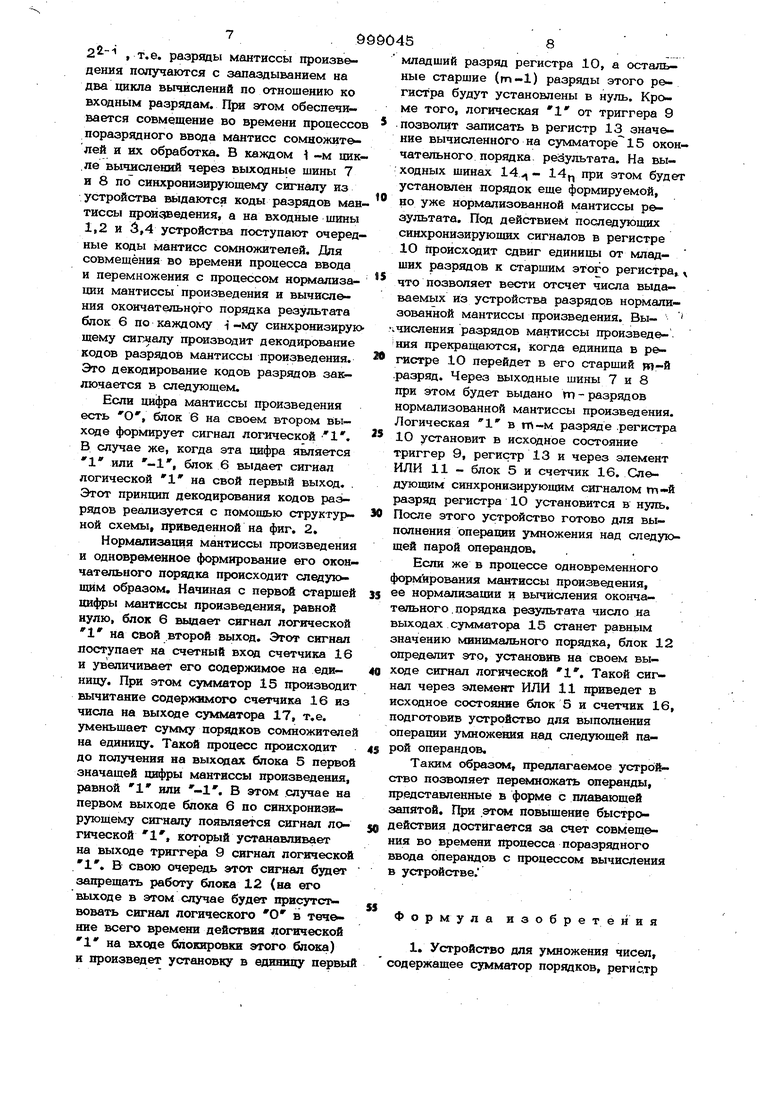

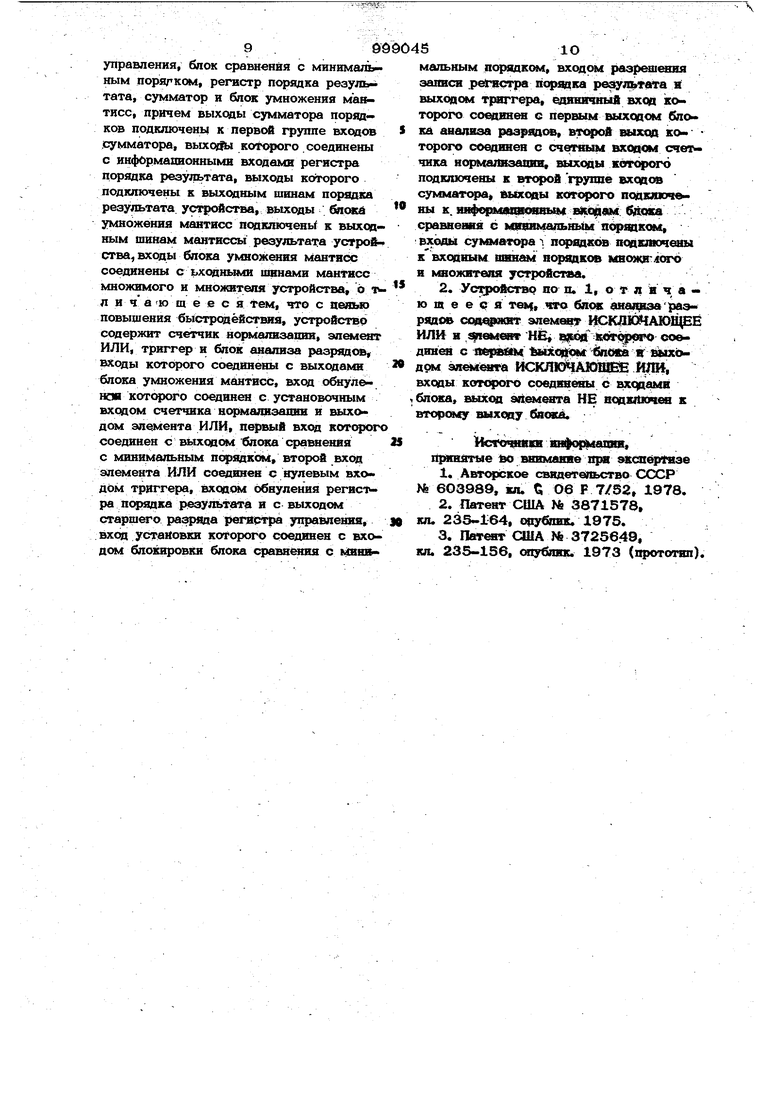

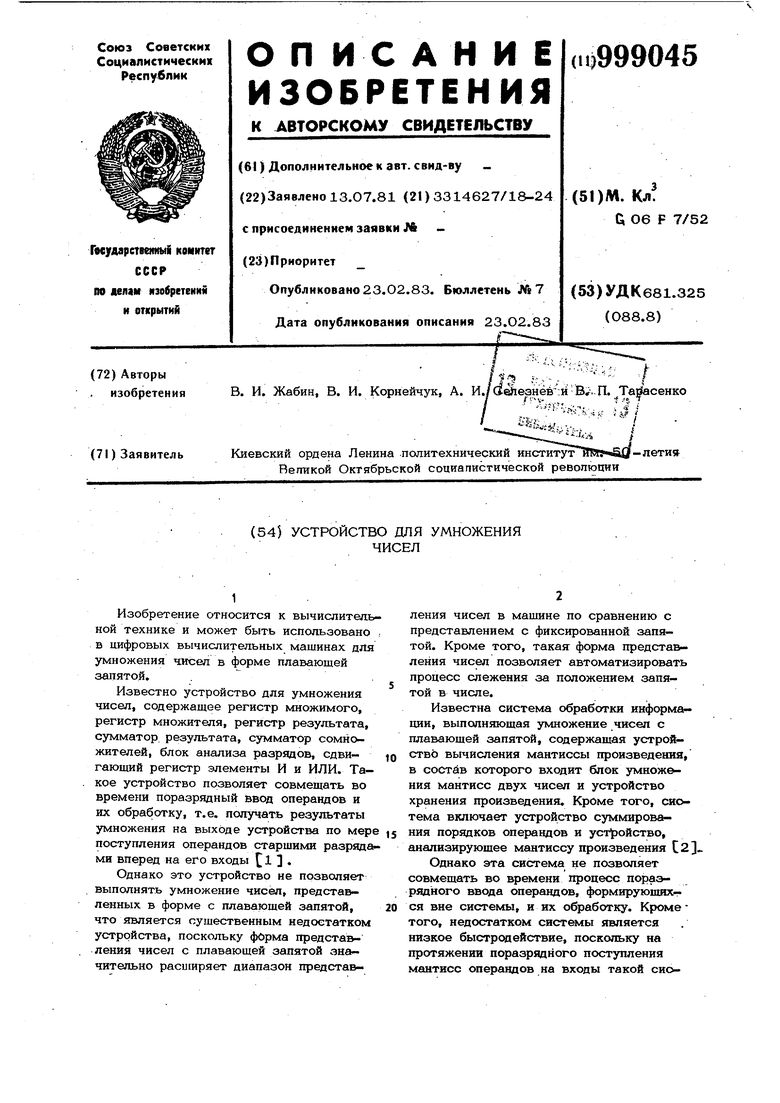

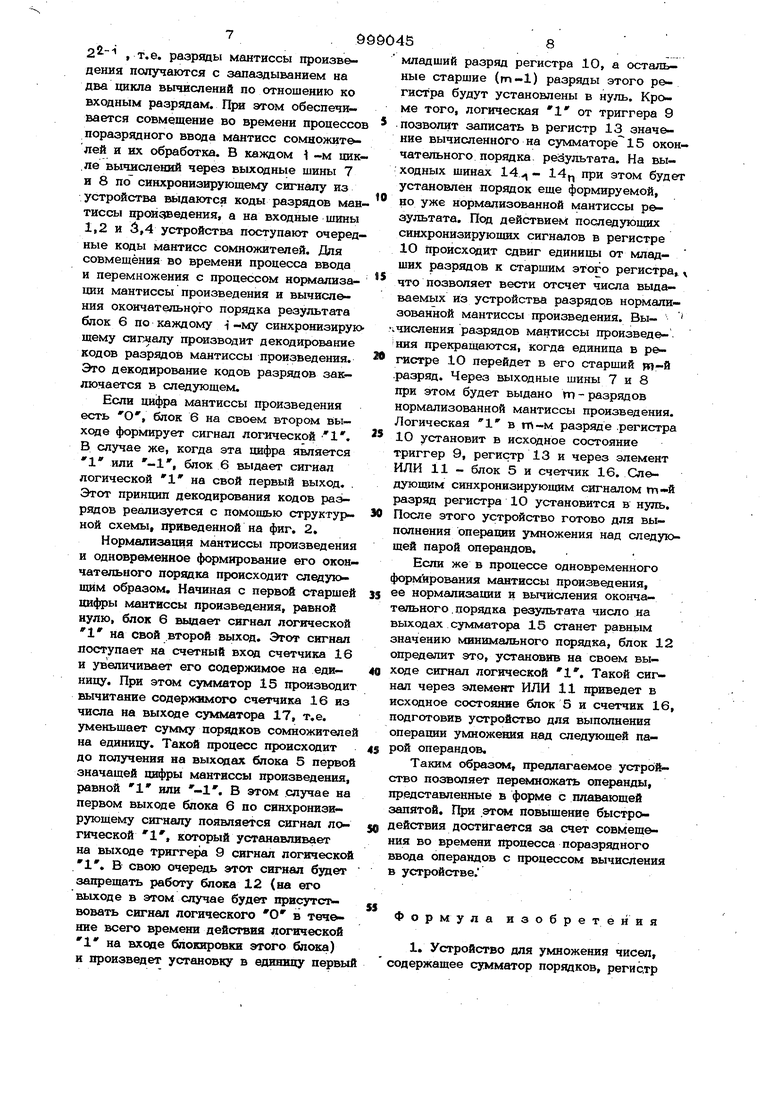

1. Изобретение относится к вычислитель ной технике и может быть использовано в цифровых вычислительных машинах для умножения чисел в форме плавающей запятой. Известно устройство для умножения чисел, содержащее регистр множимого, регистр множителя, регистр результата, сумматор результата, сумматор сомножителей, блок анализа разрадов, сдвигающий регистр элементы И и ИЛИ. Такое устройство позволяет совмещать во времени поразрядный ввод операндов и их обработку, т.е. получать результаты умножения на выходе устройства по мер поступления операндов старшими разряда ми вперед на его входы fl Однако это устройство не позволяет выполнять умножение чисел, представленных в форме с плавающей запятой, что является существенным недостатком устройства, поскольку фирма представления чисел с плавающей запятой значительно расширяет диапазон представления чисел в машине по сравнению с представлением с фиксированной запятой. Кроме того, такая форма представления чисел позволяет автоматизировать процесс слежения за положением запятой в числе. Известна система обработки информации, выполняющая умножение чисел с плавающей запятой, содержащая устройство вычисления мантиссы произведения, в состав которого входит блок умножения мантисс двух чисел и устройство хранения произведения. Кроме того, система включает устройство суммирования порядков операндов и устройство, шализирующее мантиссу произведения С 2. Однако эта система не позволяет совмещать во времени процесс поразрядного ввода операндов, формирующихся вне системы, и их обработку. Крометого, недостатком системы является низкое быстродействие, поскольку на протяжении поразрядного поступления мантисс операндов на входы такой сиотемы последняя будет простаивать и тояъко после окончания этого процесса она начинает выполнять умножение введенных операндов. Наиболее близким к изобретению является устройство для умножения чисел, содержащее регистры порадков множимого и множителя, сумматор порядков, вычитатель, регистр порядка результата, детектор переполнение порядка результата, блок умножения мантисс и детектор окончания операции умножения С 3 3 . Недостатком этого устройства являет ся низкое быстродействие при умножении . операндов, поступающих на его входы последовательным кодом, начиная со старших разрядов (например, формирующихся поразраднО вне устройства). В указанном случае это устройство сначала будет находиться в режиме приема операндов и очередные разрвды произведения в нем формироваться не будут, по скольку процессы поразрядного вводаи обработки операндов не совмещены во времени. Вычисление произведения начинается только после ввода операндов в устройство. При использовании, например, такого устройства в контуре управления процессами на протяжении всего времени ввода операндов нельзя формировать управляющее воздействие для исполнительного органа системы управления, работающей в реальном времени. Целью изобретения является повыщени быстродействия устройства. Для достижения поставленной цели устройство, содержащее сумматор порадкод, регистр управления, блок сравнения с минимальным порядком, регистр порядка результата, сумматор и блок умножения мантисс, причем выходы сумматора порядков подключены к первой группе входов сумматора, выходы которого соединены с информационными входами регистра порядка результата, выходы которого подключены к выходным щинам порядка результата устройства, выходы блока умножения мантисс подключены к выходным щинам мантиссы результата устройства, входы блока умножения мантисс соединены с входными щинами мантисс множимого и .множителя устройства, содержит счетчик нормализации, элемент ИЛИ, триггер и блок анализа разрядов, входы которого соединены с выхо дами блока умножения мантисс, вход о& нуления соединен с установочным входом счетчика нормализации и выходом элеме та ИЛИ, первый вход которого соединен 99 54 с выходом блока сравнения с минимальными порядком, второй вход элемента ИЛИ соединен с нулевым входом триггера, входом обнуления регистра порядка результата и с выходом старщего разряда регистра управления, вход установки которого соединен с входом блокировки блока сравнения с минимальным порядком, входом разрешения записи регистра порядка результата и выходом триггера, единичный вход которого соединен с пер-: вым выходом блока анализа разрядов, второй выход которого соединен с счетным входом счетчика нормализации, выходы которого подключены к второй группе входов сумматора, выходы которого подключены к информационным входам блока сравнения с минимальным порядком, входь сумматора порядков подключены к входным щинам порядков множимого и множителя устройства. Кроме того, блок анализа разрядов , /содержит элемент ИСКЛЮЧАЮШЕЕ ИЛИ и элемент НЕ,вход которого соединен с п рвым выходом блока и выходом элемента ИСР.ЛЮЧАЮШЕЕ ИЛИ, входы которого соединены с входами блока, выход элемента НЕ подключен к второму выходу блока. На фиг. 1 изображена структурная схема устройства для умножения чисел; на фиг, 2 - структурная схема блока анализа разрядов. Устройство содержит входные шины 1 и 2 мантиссы множимого, входные шины 3 и 4 мантиссы множителя и блок 5 умножения мантисс, входы которого соединены со входами 1, 2 и 3, 4. В состав устройства также входят блок 6 анализа разрядов, к входам которого подключены выходы блока 6 и выходные щины 7 и 8 мантиссы результата устройства, триггер 9, регистр 10 управления, элемент ИЛИ И, блок 12 сравнения с минимальным порядком, регистр 13 порядка результата. К выходам регистра 13 подключены выходные щины i4 + +14 порядка результата устройства. Кроме того, в состав устройства включены сумматор 15, счетчик 16 нормализации и сумматор 17 порядков, к вхощам которого подключены входные щины 18 + tldn порядка множимого и входные щины 19 nopsuKa множителя. Выходы сумматора 17 соединены с первой группой входов сумматора 15, вторая группа входов которого подключена к выходам счетчика 16. Этот счетчик своим установочным входом соединен с выходом элемента ИЛИ 11 и входом обнуления блока 5. Первый вход элемента ИЛИ 11 соединен с выходом блока 12,а второй вход этого элемента - с нулевым вхбдом триггера,входом обнуления регист ра 13 и с выходом старшего разр5вда реги ра 10. Вход установки этого регистра под лючен к входу блокировки блока 12, вхо ду рйзрешения записи регистра 13 и вы Тсоду триггера 9, единичный вход которо го соединен с первым выходом блока 6. Второй выход блока 6 подключен к счет ному входу счетчика 16. Кроме тогр..в лоды сумматора 15 соединены с информационными входами регистра 13 и бло ка 12. Блок 6 анализа разрядов (фиг. 2) содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2О и элемент НЕ 21, вход которого соединен .с первым выходом блока 6 и выходом элемента ИСКЛЮЧАЮШЕЕ ИЛИ 2. Входы элемента ИСКЛЮЧАЮШЕЕ ИЛИ 20 подключены к входам блока 6, а выход элемента НЕ 21 соединен с вторым выходом того же блока. Дпя представления мантисс сомножителей и произведения используется избыточная двоичная система счисления с пифрами , О и , Эти 1шфры, в свою очеред.ь, могут быть изо& ражен 1 кодом цифр и О канонической двоичной системы счисления. Так например, цифре - 1 соответствует наличие сигнала логической на выходных шинах 1 или 3, а также на выходной шине 7. Наличие сигнала логичес кой 1 на входных шинах 2 или 4, а также на выходной шине 8 соответствует цифре 1. Дпя цифры О соответствует отсутствие сигналов логической на 1-4 или на выходных входных шинах шинах 7 и 8. Блок 6 анализа разрядов используется для распознавания двоичных кодов цифр мантиссы результата, которые в каждом цикле вычислений формирует на своих выходах, блок 5. Это распознавание осуществляется блоком 6 по сит налам, синхронизируюшим поступление разрядов мантисс сомножителей и выдач разрядов мантиссы произведения. Блок 5 умножения мантисс предназначен для перемножения мантисс сомножителей, поступающих поразрядно, нач№ная со старших разрядов, на его входы. Регистр 1О управления представляет собой m -разрядный ( m -разрядность мантиссы) сдвигающей регистр. 9 45.4 Блок 12 сравнения с минимальным порядком представляет собой схему. сра&нения чисел, выполняющую сравнение вычисляемого значения порадка результата с в ичиной минимального порядка} при котором получаемый результат можно считать равным нулю. .Величина минимального порядка при П разрядах порядка равна -2 (один разряд порядка используется для представления его знака). Счетчик 16 нормализации - это триггёрный П -разрядный двоичный счетчтк, имеющий установочный вход. При подаче на этот вход сигнала логической в триггеры счетчика заносится П -разр5щный двоичный обратный код числа -2, что является исходным состоянием этого счетчика. Для представления порядков сомножителей и произведения используется каноническая двоичная система счисления с цифрами и О. Значения порядков представляются с помощью дополнительного кода. Сумматоры 15 и 17 - это пераллельные П -разрядные двоичные сумматоры комбинационного типа. Причем сумматор 15 реализует вычитание двух чисел с учетом их знаков, а сумматор 17 - сложение. Дпя осуществления операции вычитания сумматором 15 его вторая группа входов является инвертирующей. Устройство работает следующим . Перед выполнением операции все регистры, счетчик и триггеры устанавливаются в исходное состояние. На шины 18 - 18 устройства поступает двоичный код порядка множимого, а на шины 19 - 19 двоичный код порядка множителя. Сумматор 17 формирует сумму поступивших на его входы порядков coKfrножителей с учетом их знаков. С выходов сумматора 17 эта сумма порадков подается на сумматор 15 для последуют, щих преобразований в соответствии со значением цифр мантиссы произведения, которые в каждом i -м цикле (где i 1, 2, 3. . .) вычислений выдаются из блока 5. Одновременно с поступлением порадков сомножителей, на входные шины 1, 2 и 3,4 поступают коды старших разрядов мантисс сомножителей. По каждому i -.му синхронизирующему сигналу блок 5 при поступлении на его входы разрядов мантисс сомножителей с весом 2, формирует разр.яды мантиссы произведения с весом , т.е. раэрвд дения получаются

два цикла вычислений по отношению ко входным разрядам. Пря этом обеспечивается совмещение во времени процессов поразрядного ввода мантисс сомножителей и вх обработка. В каждом -м цик.ле вычислений через выходные шины 7 и 8 по синхронизирующему сигналу из устройства Шащаются коды разрядов мантиссы произведения, а на входные шины 1,2 и 3,4 устройства поступают очередные коды мантисс сомножителей. Для совмещения во времени процесса ввода и перемножения с процессом норн ализа ции мантиссы произведения и вычисления окончательного порядка результата блок 6 по каждому i -му синхронизирующему сигналу производит декодирование кодов разрадов мантиссы произведения. Это декодирование кодов разрядов за&лючается в следующем.

Если цифра мантиссы произведения есть О, блок 6 на своем втором выходе формирует сигнал логической . В случае же, когда эта цифра является или -1, блок 6 выдает сигнал логической на свой первый выход. . Этот принцип декодирования кодов разрядов реализуется с помощью структурной схемы, приведенной на фиг. 2.

Нормализация мантиссы произведения и одновременное формирование его окончательного порядка происходит следующим образом. Начиная с первой старшей 3S ®®

цифры мантиссы произведения, равной нулю, блок 6 выдает сигнал логической на свой второй выход. Этот сигнал поступает на счетный вход счетчика 16 и увеличивает его содержимое на единицу. При этом сумматор 15 производит вычитание содержимого счетчика 16 из числа на выхсяе сумматора 17, т.е. уменьшает сумму порядков сомножителей на единицу. Такой процесс происходит до получения на выходах блока 5 первой значащей цифры мантиссы произведения, равной или -1. В этом .случае на первом выходе блока 6 по синхронизирующему сигналу появляется сигнал логической , который устанавливает на выходе триггера 9 сигнал логической . В свою очередь этот сигнал будет запрещать работу блока 12 (на его выходе в этом случае будет присутст. вовать сигнал логического О в течение всего времени действия логической на входе блокировки этого блока) и произведет установку в единицу первы

гистра будут установлены в нуль. Кроме того, логическая 1 от триггера 9

позволит записать в регистр 13 значение вычисленного на сумматоре 15 окончательного порядка результата. На выходных шинах 14 , - 14 при этом будет установлен порядок еще формируемой,

но уже нормализованной мантиссы результата. Пси действием последующих синхронизирующих сигналов в регистре 10 происхсдит сдвиг единицы от младших разрядов к старшим этого регистра, что позволяет вести отсчет числа выдаваемых из устройства разрядов нормализованной мантиссы произведения. Вычисления разрядов мантиссы произведения прекращаются, когда единица в регистре 10 перейдет в его старший щ-й .разрад. Через выходные шины 7 и 8 при этом будет выдано m - разрядов нормализованной мантиссы произведения. Логическая I в m-м разряде регистра

10 установит в исходное состояние

триггер 9, регистр 13 и через элемент ИЛИ 11 - блок 5 и счетчик 16. Спедующим синхронизирующим Сигналом т-й разрад регистра 1О установится в нуль.

0 После этого устройство готово для выполнения операции умножения над следующей парой операндов.

Если же в процессе одновременного формирования мантиссы произведения.

тельного.порядка результата число на выходах сумматора 15 станет равнь1М значению минимального порядка, блок 12 определит это, установив на своем выходе сигнал логической I. Такой сигнал через элемент ИЛИ 11 приведет в исходное состояние блок 5 и счетчик 16, подготовив устройство для выполнения операции умножения над следующей парой операндов.

Таким образом, предлагаемое устройство позволяет перемножать операнды, представленные в форме с плавающей запятой. При .этетл повыщеняе быстро799&04S8ы мантиссы произве- младший разряд регистра 10, а остальс запаздыванием наные старшие (m-l) разрады этого ренормализации и вычисления оконча- действия достигается за счет совмещения во времени процесса поразрядного ввода операндов с процессом вычисления в устройстве. Формула изобретения 1, Устройство для умножения чисел, содержащее сумматор порадков, регис.тр управления, блок срввн«яня с минимаш ным порягком, регистр п рвдка результата, сумматор и блок умножения ма тисе, причем выходы сумматора пород ков подключены к группе входов .сумматора, выхо(|Ы KOtoporo. соединены с инфбрмашюннымн входами регистра порядка результата, выходы ксггорого подключены к выходным шинам порошка результата, устройства, выходы блокд умножения мантисс подключены к выход ным шинам мантиссы результата устрой ства, входы блока умножения мантисс соединены с ьхрпными шинами мантисс множимого и множителя устройства, о т п и ч а Ю шее с я тем, что с пеяыо повышения быстродействия, устройство содержит счетчик нормализация, элемент ИЛИ, триггер и бпок анализа разряд ж оды которюго соедШ1еш 1 с выходами блока умножения мантисс, вход ойсуленов которого соединен с установочным входом счетчика нормализации и выхо дом элемента ИЛИ, первый вход кото|юг соединен с выход(( 1$лока сравнения с минимальным порядком, вторс вход элемента ИЛИ соединен с нулевым входом триггера, входом обнуления регис-пра порздка результата и с выход 1 старшего разр5|па регйртра управления, вход установки которого соединен с вхо дсим бло&ировки блока сравн гая с «лаив мальным nofKtuKOM, входом разрешеяия записи р встра порадка результата н выходом триггера, единичный вход которого соеаювя с первым выходом блока анализа разршст, второй выхш ко- торого соединен с счетным вхопсм счетчика нормалнзаявя, выходы которого подключены к второй входов сумматора, йыхсаы которого пОДкюсиче ны к иифе|1М|вашо8вь1М . бдока сражения с ьдавсималькым пфздксм, входы сумматора ( порвщхсю подк1йоче11Ы квходным шяиам порядков мвожимсяю и кшожителя устройстам. 2. Уа ройство по п. 1, о т д и ч а « ю щ е е с я тец, «го бпрк аиалрэаразрадо элемеог ИРКДШАЮВ Ё ИЛИ и грвменФ НЕ k9r)€a4 сое динен с 1б|1й Щ Ымхофмблока ж Е дом эпеМёвта ИСКЛКЙАШОЗЕ , входы которого соедивены с вхяпамй блока, выход НВ водкАючеа к вторсму выходу 6noiEa. IKoro iffiiaE ш1ф(чА4а1вга, принятые ьо вавмаяке пря sKcneptnae 1. свидетешьство СССР № 6О3989, 1Л. с; 06 Р 7/52, 1978. 2.Патент США № 3871578, кл. 235-164, «щубяик, 1975. 3.Пат ПСША № 3725649, кл. 235-156, опубтос. 1973 (прототип).

Зо4оJJ

/Ato.

Mfon

ч -o

10

f«

сж

t s г 1

,

-Ч

f3

15

Фиг. 2