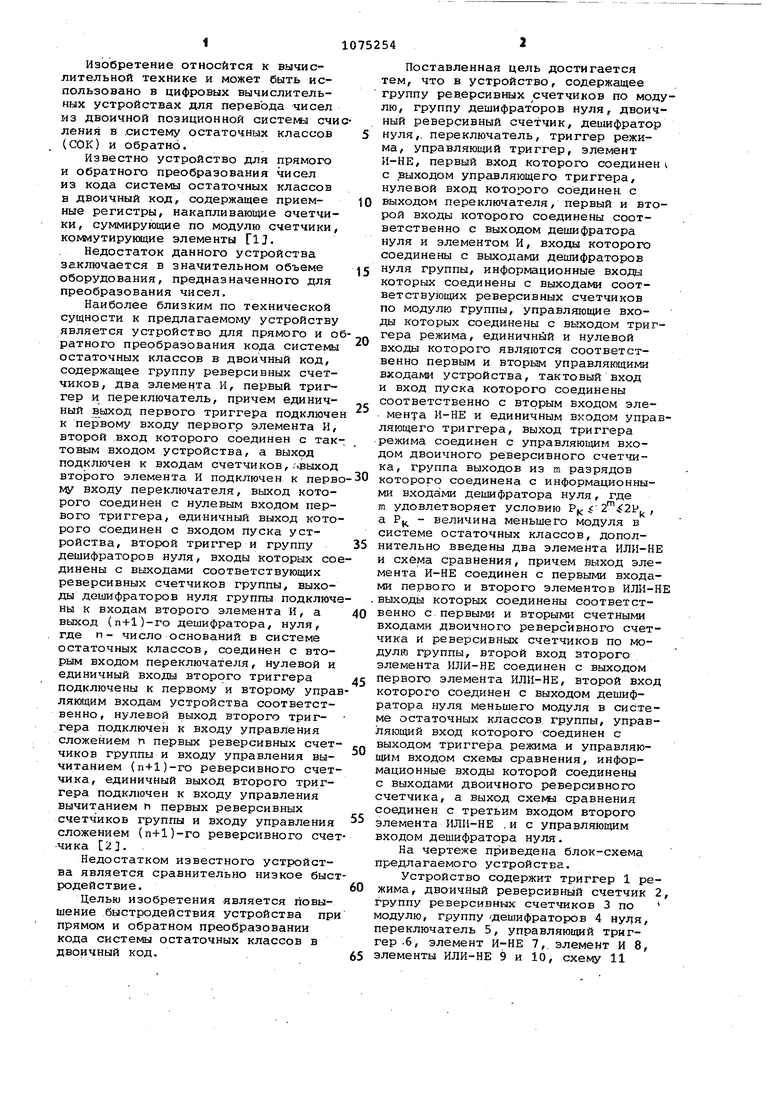

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из двоичной позиционной систели счи ления в .систему остаточных классов (СОК) и обратно. Известно устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код, содержащее приемные регистры, накапливающие очетчики, суммирующие по модулю счетчики, коммутирующие элементы TU. Недостаток данного устройства заключается в значительном объеме оборудования, предназначенного для преобразования чисел. Наиболее близким по технической сущности к предлагаемому устройству является устройство для прямого и о ратного преобразования кода системы остаточных классов в двоичный код, содержащее группу реверсивных счетчиков, два элемента И, первый, триггер и переключатель, причем единичный выход первого триггера подключе к первому входу первого элемента И, второй вход которого соединен с так товым входом устройства, а выход подключен к входам счетчиков, г выход второго элемента И подключен к перв му входу переключателя, выход которого соединен с нулевым входом первого триггера, единичный выход кото рого соединен с входом пуска устройства, второй триггер и группу дешифраторов нуля, входы которых со динены с выходами соответствующих реверсивных счетчиков группы, выходы дешифраторов нуля группы подключ ны к входам второго элемента И, а выход (п+1)-го дешифратора, нуля, где п- число оснований в системе остаточных классов, соединен с вторым входом переключателя, нулевой и единичный входы второго триггера подключены к первому и второму упра ляющим входам устройства соответственно, нулевой выход второго триггера подключен к входу управления сложением п первых реверсивных счет чиков группы и входу управления вычитанием (п+1)-го реверсивного счет чика, единичный выход второго триггера подключен к входу управления вычитанием м первых реверсивных счетчиков группы и входу управления сложением (п+1)-го реверсивного сче чика 22. Недостатком известного устройства является сравнительно низкое быс родействие. Целью изобретения является повышение быстродействия устройства пр прямом и обратном преобразовании кода системы остаточных классов в двоичный код. Поставленная цель достигается тем, что в устройство, содержащее группу рев.ерсивных счетчиков по модулю, группу дешифраторов нуля, двоичный реверсивный счетчик, дешифратор нуля,, переключатель, триггер режима, управляющий триггер, элемент Н-НЕ, первый вход которого соединен с выходом управляющего триггера, нулевой вход которого соединен с выходом переключателя, первый и второй входы которого соединены соответственно с выходом дешифратора нуля и элементом И, входы которого соединены с выходами дешифраторов нуля группы, информационные входы которых соединены с выходами соответствующих реверсивных счетчиков по модулю группы, управляющие входы которых соединены с выходом триггера режима, единичный и нулевой входы которого являются соответственно первым и вторым управляющими входами устройства, тактовый вход и вход пуска которого соединены соответственно с вторым входом эле. менуа И-НЕ и единичным входом управляющего триггера, выход триггера режима соединен с управляющим входом двоичного реверсивного счетчика, группа выходов из m разрядов которого соединена с информационными входами дешифратора нуля, где m удовлетворяет условию Р) f (2V , а Рц - величина меньшего модуля в системе остаточных классов, дополнительно введены два элемента ИЛИ-НЕ и схема сравнения, причем выход элемента И-НЕ соединен с первыми входами первого и второго элементов ИЛИ-НЕ выходы которых соединены соответственно с первыми и вторы№1 счетными входами двоичного реверсивного счетчика и реверсивных счетчиков по модулю группы, второй вход второго элемента ИЛИ-НЕ соединен с выходом первого элемента ИЛИ-НЕ, второй вход которого Соединен с выходом дешифратора нуля меньшего модуля в системе остаточных классов группы, управляющий вход которого соединен с выходом триггера режима и управляющим входом схемы сравнения, информационные входы которой соединены с выходами двоичного реверсивного счетчика, а выход схемы сравнения соединен с третьим входом второго элемента ИЛИ-НЕ .и с управляющим входом дешифратора нуля. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит триггер 1 режима, двоичный реверсивный счетчик 2, группу реверсивных счетчиков 3 по модулю, группу Дешифраторов 4 нуля, переключатель 5, управляющий триггер .6, элемент И-НЕ 7,. элемент И 8, элементы ИЛИ-НЕ 9 и 10, схему 11

сравнения, дешифратор 12 нуля, вход 13 пуска, первый и второй управляющие входы 14 и 15 устройства, тактовый вход 16.

Предлагаемое устройство работает следующим образом.

Первый управляющий вход 14, сигнал на который подается при преобразовании числа из двоичного кода J3 код СОК, подключен к единичному входу триггера 1. Сигнал, пришедший на первый управляющий вход, переключает триггер 1 в единичное состояние, и сигнал с его выхода , подготавливает двоичный реверсивный счетчик 2 к работе в режиме Вычитание, счетчики 3 - к работе в режиме Сложение, а дешифратор 4 устанавливает в нулевое состояние. Преобразуемое число в двоичном коде записано в счетчике 2, счетчики 3 обнулены. Сигнал, приходящий на вход 13 пуска, устанавливает триггер б в единичное состояние, сигналом с единичного выхода которого открывается элемент И-НЕ 7 по перёому входу, на второй вход которого поступают тактовые импульсы.

Нулевой сигнал с выхода дешифратора 4, нуля поступает на второй вход элемента ИЛИ-НЕ 9. Если содержимое счетчика 2 больше или равно величине наименьшего модуля кода СОК Pj , то единичный сигнал с выхода схемы 11 сравнения, пройдя через третий вход элемен1;а ИЛИ-НЕ 9, устанавливает на выходе элемента ИЛИ-НЕ 9 нулевой сигнал, который подается на вход элемента ИЛИ-НЕ 10. По тактовому сигналу, прошедшему через элемент И-НЕ 7, на входе элемента ИЛИ-НЕ 10 устанавливается нуевой сигнал. При этом по единичному сигналу с выхода элемента ИЛИ-НЕ 10 происходит постепенное вычитание величины Р в счетчике 2 сложение с величиной Рц в счетчиках 3. Когда содержимое счетчика 2 станет меньше величины Р, на выхое схемы 11 сравнения будет нулевой сигнал, что, в свою очередь, вызывает, при наличии тактового импульса, единичный сигнсш на выходе элеента ИЛИ-НЕ 9 и нулевой сигнал на выходе элемента ИЛИ-НЕ 10. По единичному сигналу с выхода элемента ЛИ-НЕ 9 происходит постепенное вьгаитание по единице в счетчике 2 и сложение с единицей в счетчиках 3. В момент обнуления счетчика 2 срабатывает дешифратор 12 нуля, сигнал с выхода которого, пройдя чеез переключатель 5, переводит триггер б в нулевое состояние. При этом рекращается поступление тактовых мпульсов через элементы И-НЕ 7, ЛИ-НЕ 9 и 10. В счетчиках 3 зарегистрирован код СОК, соответствующий двоичному коду, первоначально записанному в счетчике 2.

Второй управляющий вход 15 при преобразовании числа из кода СОК в двоичный код подключен к нулевому входу триггера 1, сигнал с выхода которого устанавливает схему 11 сравнения в нулевое состояние и подготавливает счетчик 2 к работе в

0 режиме Сложение, а счетчик 3 к работе в режиме Вычитание. Преобразуемое число в коде СОК записано в счетчики 3, счетчик 2 обнулен. По сигналу пуска триггер 6 ус5 танавливается в единичное состояние и сигналом с единичного выхода открывает элемент И-НЕ 7, на другой вход которого поступают тактовые импульсы. Нулевой сигнал с выхода схемы 11 сравнения поступает на третий вход элемента ИЛИ-НЕ 9. Если содержимое счетчика 3 не равно нулю, то нулевой сигнал с выхода дешифратора 4j нуля поступает на Второй вход элемента ИЛИ-НЕ 9. По тактовому сигналу, прошедшему через элемент 7, на выходе элемента ИЛИ-НЕ 9 устанавливается единичный сигнал, по которому происходит постепенное сложение с единицей в счетчике 2 и вычитание по единице в счетчиках 3. В момент обнуления счетчика 3., на вход элемента ИЛИ-НЕ 9 с выхода дешифратора 4 нуля подается единичный сигнал, а на выходе ИЛИ-НЕ 9 появляется нулевой сигнал, который поступает на вход элемента ИЛИ-НЕ 10. По тактовому сигналу, прошедшему через элемент И-НЕ 7, на выходе элемента ИЛИ-НЕ 10 устанавливается. . единичный сигнал, по которому происходит постепенное сложение содержимого счетчика 2 с величиной Р, и вычитание величины Р из счетчиков 3. В момент обнуления всех счетчиков 3 срабатывают дешифраторы 4, 4 , ..., 4|, нуля, сигналы с выходов которых, поступая на входы элемента И 8, вырабатывают на его выходе сигнал, который, пройдя через переключатель 5 на нулевой вход триггера б, переводит его в нулевое состояние и прекращает тем самым поступление тактовых импульсов на входы счетчиков 2 и 3 через элементы И-НЕ 7, ИЛИ-НЕ 9 и 10. В счетчике 2 при этом регистрируется двоичный код преобразованного числа.

Предлагаемое устройство обладает ;большим быстродействием, чем извест ное, так как в нем прямое и обратное преобразование чисел из кода СОК в двоичный код происходит за N тактовых импульсов, где N - преобразуемое число в двоичном коде, а в предлагаемом устройстве аналогичное преобразование происходит

+ 1 такне более чем а; , где Р, - наименьший модуль и

тов

е СОК, Г: целое число. коде

При ЭТИМ увеличение схэстава обо рудоваиия по сравнению с из вестным устройством неэначитель ное.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прямого и обратного преобразования числа из системы остаточных классов в позиционный код | 1985 |

|

SU1287293A1 |

| Устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код | 1983 |

|

SU1089573A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Устройство для преобразования кодов | 1981 |

|

SU968803A1 |

| Преобразователь угла поворота валаВ КОд | 1979 |

|

SU836643A1 |

| Кодирующее устройство с дельтамодуляцией и импульсно-кодовой модуляцией | 1977 |

|

SU661789A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1629886A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

3rfi

US

4к /r-/ I

I JA- I J/ |...| J/r-r I I ... I jn I

МВМЦ ЧРш тятцтящ й щтиЛ нннмамёчгвм ив1П ятЛ1тт ияЛ

л П 1 ЯП /1 ЧГ7 Г 1 I I л л /

LIJ

JJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования чисел из кода системы остаточных классов в двоичный код | 1976 |

|

SU574714A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 756401, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| щий триггер, элемент И-НЕ, первый вход которого соединен с выходом управляющего триггера, нулевой вход которого соединен с выходом переключателя, первый и второй входы кото-, рого соединены соответственно с выходом дешифратора нуля и элементом И, входы которого соединены с выходами дешифраторов нуля труп- пы, информационные входы которых соединены с выходами соответствующих реверсивных счетчиков по модулю группы, управляющие входы которых соединены с выходом триггера режима, единичный и нулевой входы которого являются соответственно пвр- вым и вторым управляющими входами устройства, тактовый вход и вход пуска которого соединены .соответственно -с вторым входом элемента И-НЕ и единичным входом управляю ;,это триггера-, выход триггера режима сое; динем с управляющим входом двоичного реверсивного счетчика, группа Выходов из m разрядов которого соединена с информационными входами дешифрато за нуля, где m удовлетворяет условию РК i (, а Р - величина меньшего модуля в системе остаточных классов, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в него введены ;два элемента ИЛИ-НЕ и схема сравнения, причем выход элемента И-НЕ сое§ динен с первыкш входами первого и BTOpoix) элементов РШИ-НЕ, выходы (Л которых соединены соответственно с первыми и вторыми счетными входами с двоичного реверсивного счетчика и реверсквньрс счетчиков по модудпо груп пы, второй вход второго элементу ИЛИ-НЕ соединен с выходом первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом дешифратора ;нуля меньшего модуля в системе оста точных классов группы, упрайлякяций вход которого соединен с выходом 01 триггера режима и управляющим вхогчэ дом схемл сравнения, информационные 01 входа которой соединены с выходами jlBQH4Horo реверсивного счетчика, а 4ii | |||

| выход схемы сравнения соединен с треч, jfbHM входом второго элемента ИЛИ-НЕ и с управляющим входом дешифратора нуля. | |||

Авторы

Даты

1984-02-23—Публикация

1982-12-29—Подача