- 1

Изобретение относится к вычислительной технике.

Известно устройство, содержащее арифметико-логический блок, блок памяти и блок управления. В этом устройстве вы- числение системы многоместных логических функций вьшолняется программным путем.

В качестве элементарных операций при этом используются либо команды п оразрядных двухместных логических операций, либо команды условных переходов. Двухместные логические операции выполняются в арифметико-логическом блоке, а модификация адреса команды при условных переходах - в блоке управления с помощью узла выбора условия перехода и счетчика команд С1} .

Однако программная реализация системы логических функций снижает производительность, усложняет программное обеспечение и увеличивает затраты яче-, ек памяти для хранения программ

Известен процессор для управлешя производственным процессом, в котором применена специальная логическая схема для выполнения логических операции над информацией, поступающей по шине

передачи данных t2 .

Недостатками его являются значительные -аппаратурные затраты, жесткость структуры операционного блока, Необхо Q димость его перестройки при изменении реализуемых функций.

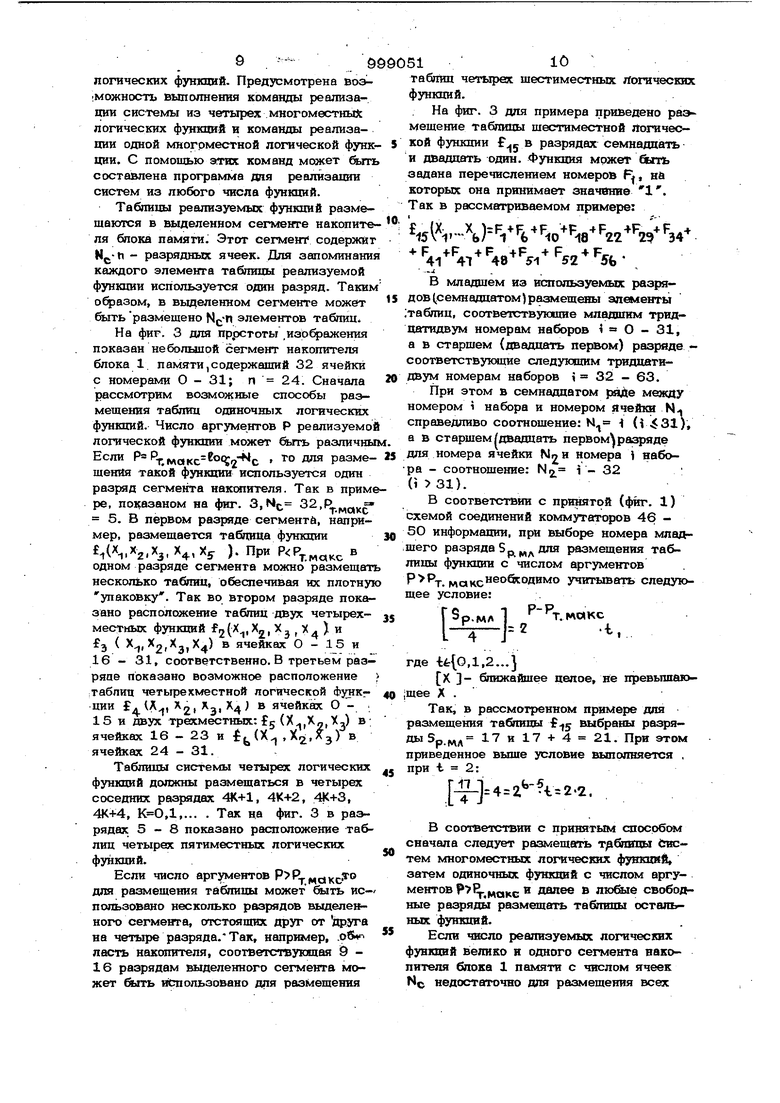

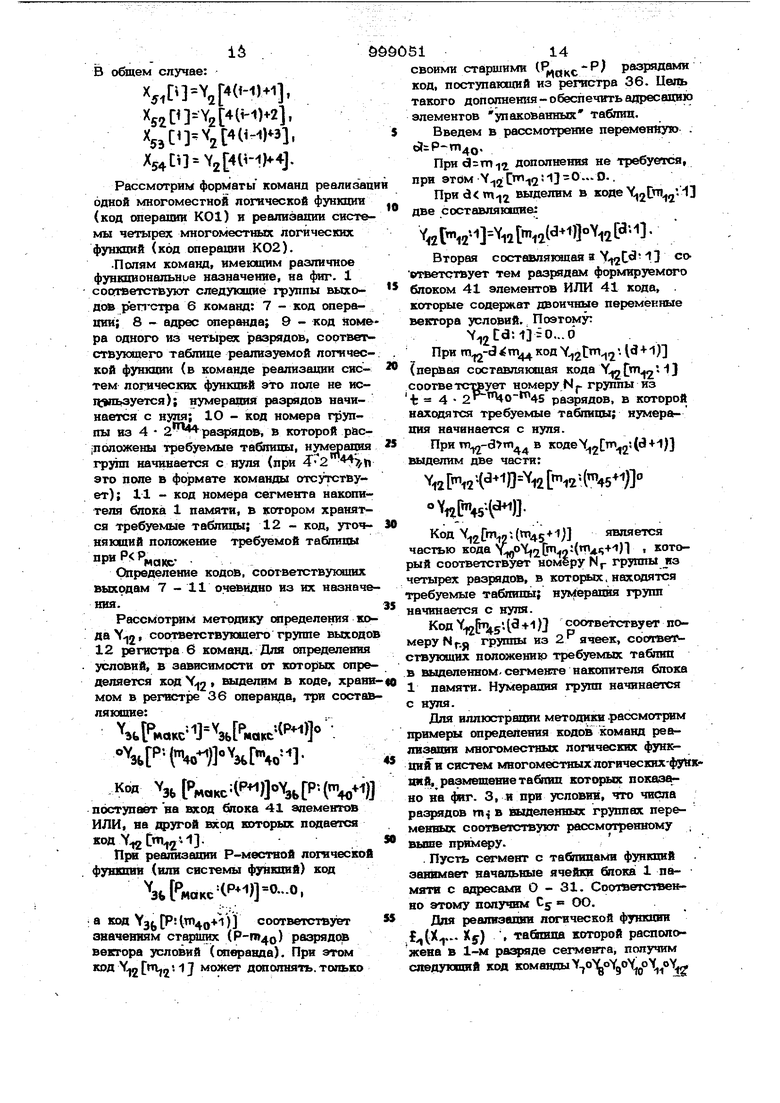

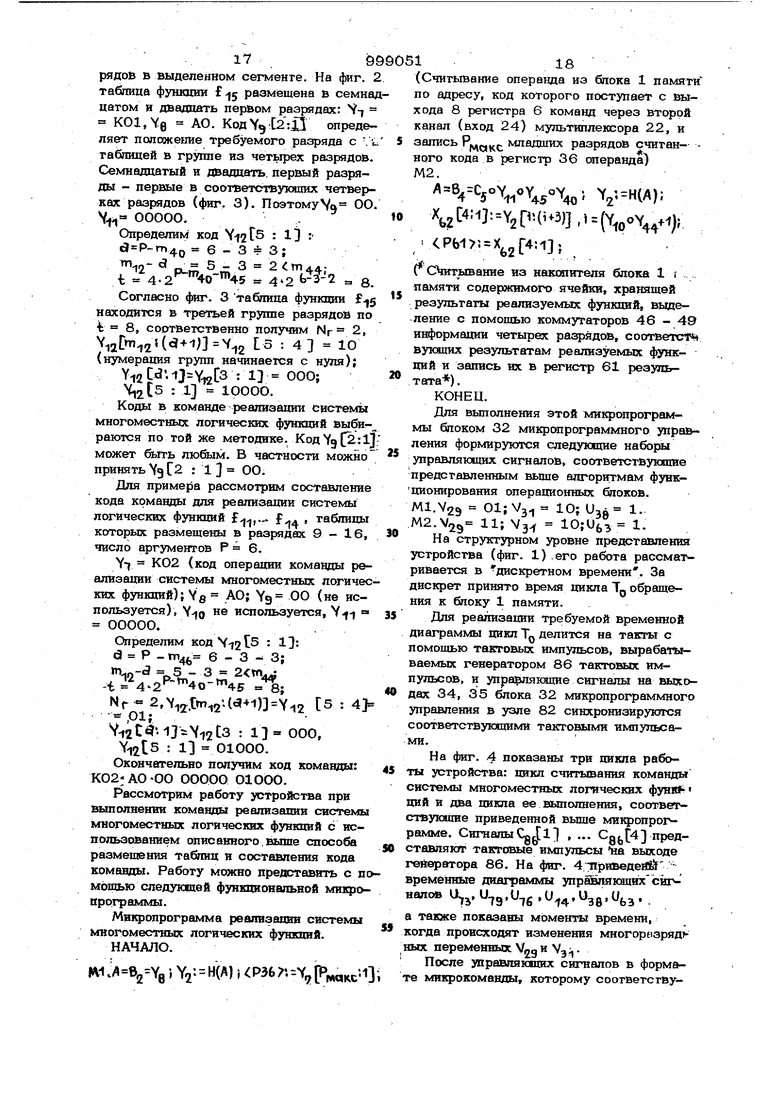

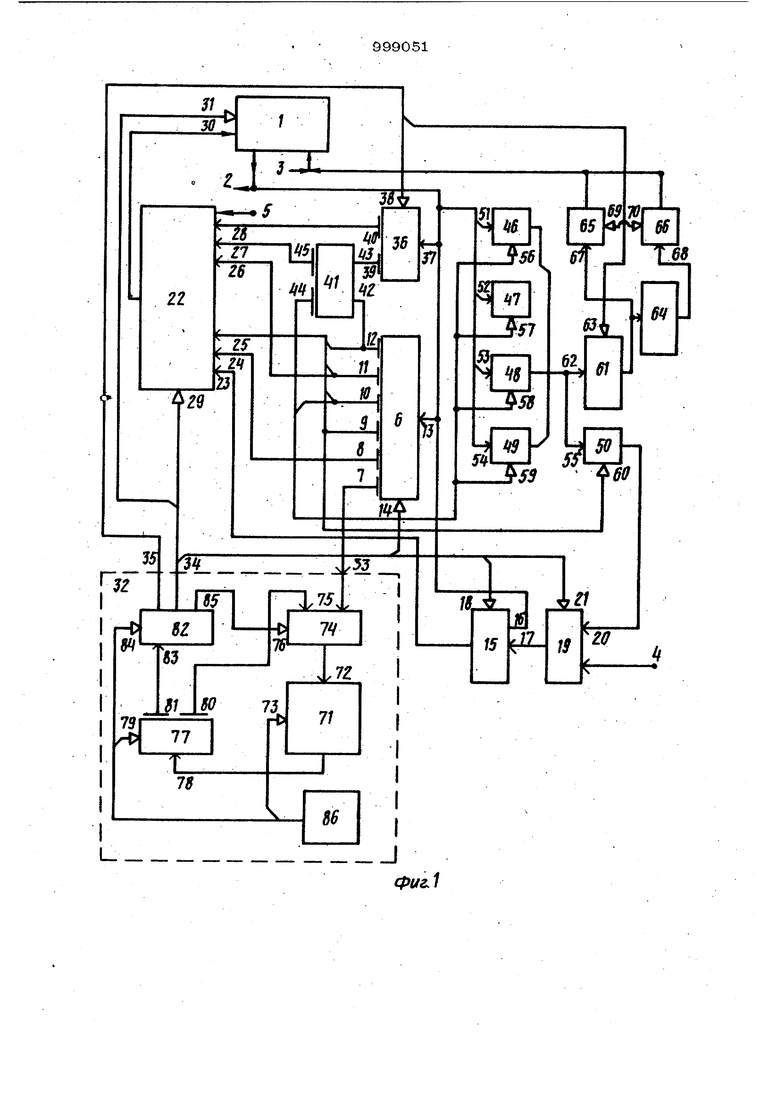

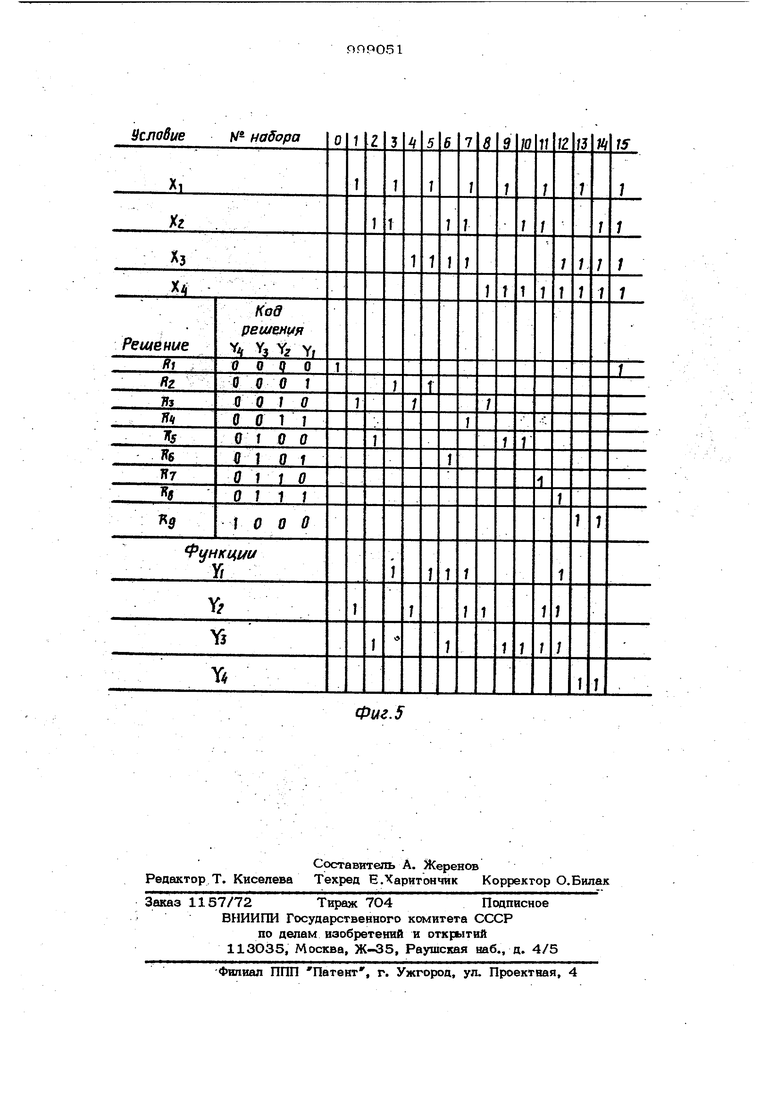

Наиболее близким по. технической сущности к изофетению является устройство, содержащее ячейки памят, регистр числа, регистры первого и второго операндов и регистр адреса, причем выход каждой ячейки памяти соединен с cooi ветствуюшими информационными входами регистра числа, регистра первого -операнда и регистра второго операнда. Данное устройство может вьшолнять функции арифметико-логического устройства с табличной реализацией поразрядных двухдлесгных И одноместных логических функций. Таблицы можно изменять путем перезаписи их в. ОЗУ Г 3 Однако это устройство не имеет средств для выполнения системы многоместных логических функций. Поэтому в ЭВМ с таким устройством хранения и преобразования для вычисления системы многоместных логических функхтей возможен только программный способ, недостатками Которого являются-сложность программ, значительные затраты памятидля их хранения, сравнительно большое время выполнения программ. . Целью изобретения является повьпиение производительности. Поставленная цель достигается тем, что в устройство, содержащее блок памяти, регистр команд, счетчик команд, коммутагор условия перехода, мульти-г плексор адресных кодов, которого соединен с адресным входом блока памяти, блок микропрограммного упрарления, вход которого соединен, с первым выходом регистра команд, информационный вход которого соединен с информационны выходом блока памяти, являющимся вько дом устройства, информационный вход бл ка памяти является первым входом устройства, первый информационный вход мультиплексора . адресных кодов подключе к выходу счетчика команд, второй информационный вход - к второму выходу регистра команд, третий информационный. вход соединен.с третьим, четвертым, . пятым и шестым вьЕходами регистра команд, информационный вход счетчика команд соединен с информационным выходом блока памяти, счетньдй вход счетчик команд подключен к выходу коммутатора условия перехода, первый информационный вход которого является вторым входом устройства, управлякнщие входы блока памяти, регистра команд, счетчика команд, коммутатора условия перехода и мультиплексора адресных кодов соединены с первым выходом блока микропрог раммного управления, введены регистр операнда, блок элементов -ИЛИ, пять коммутаторов информации, регистр результата, дешифратор и две группы переключателей, причем информационные входы регистра операнда и с первого по чет вертыи коммутаторов информации соединен с информационных выходом блока памяти, выходы первого, второго, третьегочи четве того коммутаторов информации соединены с информационными входами регистра результата к пятого коммутатора инфорации, выход которого подключен к втоом.у информационному, входу коммутатора условия перехода, выход регистра результата соединен с информационными входаи переключателей первой группы и деифратора, выход которого п-одключен к информационным входам переключателей второй группы, а выходы переключате- , лей перЬой и второй-групп, соединены с . соответствующими разрядами.информационного входа блока памяти, управляющие входы регистра операнда, регистра результата, переключателей первой и.второй групп соединены с вгорьш выходом бло-ка микропрограммного управлени;я, управл яющий вход пятого коммутатора информации соединен с, третьим выходом регистра команд, управля.кщие. входы с первого по четвертый коммутаторов ин-. формации соединены с четвертым выходом регистра команд и с первым выходом блока элементов ,ИЛИ, первые входы которых подключены к шестому выходу регистра команд, а вторые входы - к первому выходу регистра операнда, четвертый и пятый информационш 1е входы мультиплексора адресных кодов соединены соответственно с пятым, выходом .регистра Команд и вторым выходом блока . элементов ИЛИ, второй выход регистра операнда подключен к шестому информационному входу мультиплексора адресньк . кодов, седьмой информа1Шоннь1й входкото.рого соединен с третьим входом устройства. На фиг. 1 предста лена структурная схема устройства; на. фиг. 2 - пример реализации узл1а формирования управляющих сигналов; на фиг. 3 - пример размещения таблиц в вьвделенном сегменте; на фиг.. 4 - временная диаграмма работы устройства; на фиг. 5 - пример кодирования альтернативных решений. Устройство содержит блок 1 памяти, выход 2 устройства; первый -3, второй , 4 и третий 5 входы устройства; регистр 6 команд; первый 7, второй 8, третий 9, четвертый 10, пятый 11 и шестой 12 выходы регистра 6 команд, информационный 13 и управляющий 14 входы регистра 6 команд; счетчик 15 команд, информационный 16, счетный 17 и управля11С1ЩИЙ 18 входы счетчика 15 команд; коммутатор 19 условия перехода с первым .4 информационным, вторым 20 информационным и управляющим 21 входами; мультиплексор 22 адресных кодов; информашюнные входы 23- 28 мупьтиплексо. ра 22, его управляющий вход 29, адресный 30 и управляющий 31 входы блока 1 -памяги; блок 32 микропрограммнога уЛравления с входом 33, первым 34 и вторым 35 выходами; регистр 36 опера да, информационный 37 и управляклций 38 входы регистра 36, первый 39 и вто рой 40 выходы регистра 36; блок 41 элементов ИЛИ, первый 42 и второй 43 Ьходы блока ,41 элементов ИЛИ, первый |44 и второй 45 их выходы; . коммутаторы 46-50 информации, имеющие соответ ственно информационные входы 51 - 55, .управляющие входы 56-60, регистр 61 результата с информационным входом 62 и управлякнцим входом 63, дешифратор 64; группы переключателей 65 и 66 с, входами 67-7О; узел 71 памяти микропрограмм с адресным входом 72 и управляющим входом 73; регистр 74 адреса микрокоманд с входами 75 и 76, регистр 77 микрокоманд с входами 78 и 79 и выходами 80 и 81; узел 82 формирования микрокоманд с входами 78 и 79 и выходами 80 и 81; узел 82 формирования управлякяцих сигналов с входами 83, 84 и с выходом 85,генера тор 86 тактовых импульсов; элементы НЕ 87 и 88; элемент И НЕ 89, элемен ты И 9О. Блок 1 памяти, может работать в тре режимах в зависимости от кода V f2:lj на управляющем входе 31: при V 3 ОО - режим хранения инфор мации; при Vi 10 - режим чтения, при V2tn:1 -. Н(Л), , при V2 11 - режим записи, при ° тА)-. ХзСь-.1, где Н (А) - содержимое ячейки накопите ля с адресом А; Х ° вхо дах ЗО и З.Уп- код на выходе 2, п число разрядов в блоке 1 памяти. Регистр 6 команд работает в двух ре жимах: при U-}4 О - режим хранения; при Ux|4 1 - режим записи кода X .в регистр, где и. , X - сигналы на входах 14 и 13. В регистр 6 записывается п разрядный код Х.,3 2 Г 1Счетчик команд 15. работает в 3-х режимах: при ОО: хранение информации; при 10: запись СК v X,g при V-jg 11: модификация кода .адреса: CR . где ,y(,, X -1:7 коды на соответствующих входах; СК , С. содержимое счетчика 15 команд в текущий момент времени и в следующий момент времени. В счетчик 15 команд записывается И1 разрядный код , где m - число разрядов в коде адреса блока 1 памяти. Входы Х, .iJ подключены к тем разрядам выхода Yn , которые соответствуют положению адреса перехода в командах безусловного перехода, например младшим: Гт: 1 Y тп-. Коммутатор 19 условия перехода выполняет функцию, выбора одного из разрядов кода, имеющегося на его информации онных входах 4 и 2О, номер которого соответствует коду V2-,Ha управляющем входе 21: V2.ir3:l 000: V,,, при при 001: V х D.при V2-tC3 : 1 010;Х. Х при V21 3:1 111: У„ Х Х4СТ. где Сигнал на выходе коммутатора 19, поступающий на вход 17, Х2о переменная на входе 2О; ХТ7 : 13код на входе 4, предетавлякший собой осведомительные сигналы о ходе вычислительного процесса. Код X/| может содержать перенос из старшего разряда, значение младшего разряда, знак и другие соответствующие освеаомитепьныа сигналы, которые поступают из арифметико-лргичеЪкого устройства и сцвигателя (не показаны). Мультиплексор 22 адресных кодов имеет четыре информационных канала, Koropbnvi соответствуют входы 23 - 25 и группа входов 26, 27,. 28 и 5 . На управляющий вход 29 поступает код номера канала. При этом на выход (Vnn УЗО) передается код канала, номер которого соответствует коду V2g . Каждый канал и выход мультиплексора 22 имеют m разрядов соответственно числу разрядов на адресном входе 30 блока 1 памяти. В четвертом канале w разрядов разделены на четыре группы, которым соответтвуют входы 26, 27, 28 и 5. За счет этих соединений в четвертом канале мутаьгтиплексора22 реализуется следующая. ункция Гконкатенации ,.т,.,,, ° 28K6J 5t 5 °%l li °V 5 X.oKo-l . 9 где В - код на входах четвертого кана ла мультиплексора .22; X, , YJ - К.ОЦЫ на 1-м входе и j -м выходе, 1 содержащие , т-разрядов, соответственно, О - знак конкатенации. На вход 5 подается константа C..l На первый,второй и третий каналы мультиплексора 22 согласно фиг. 1 по-г ступают коды В, Х2 yCniM3; 82Cm-..1) ,,iK 1 °Vloho- гя,:1. Функции, реализуемые мультиплексором 22, можно представить в следующем виде при V2g ОО :42f В ; при 29 при V2g 10 .-ч22 3 %oX,o4,oOY при V29 11 L 22 4 5%V где Y22 - код на выходе мультиплексора 22. Регистр 36 операнда используется для записи и хранения операнда - вектора Р двоичных переменных. Его информа ционный вход 37 подключен к Р младшим разрядам выхода 2 блока 1 памяти. Регистр 36 работает в двух режимах при -зв 1 - запись кода Xg-j , при -зв О - хранение. Блок 41 элементов ИЛИ вьшолняет операцию поразрядной дизъюнкции кодов X, . ,m4.7 t/. 3q-Z. / я-j Д« - i -и разряд кода на выход блока 41. Этот код разделен на две части: ,sh45. %4 45 42 43 Каждый из коммутаторов 46- 5О информации переключает на выход один из разрядов кода Xg.Ci слЕ поступаю щего на информационный вход. Номер переключаемого разряда соответствует коду j на управляющем входе: t j + 1. Выходные сигналы Y, - коммутато ров 46 - 49 информации офазуют четир€ хразрядный код, поступающий на i8 ходы 62 регистра 61 результата и 55 коммутатора 50 информации (.При производится запись кода 2® регистр 61. Переключатели 65 и 66 имеют по 3 состояния и работают следующим образом .,.4и.и,„Р; b5LJ- b9%ll X. l6-.,X pb-. , где R - состояние большого выходного сопротивления. V(, , Vc4 - сигналы на выходах fev Л64 результата и дешифратора регистра 61 64, На выходе дешифратора 64 всегда один и только один разряд равен 1, номер которого соответствует коду, подаваемому на вход дешифратора. Использование переключателей 65 и 66 с тремя состояниями выхода позволяет объединить несколько источников сигнала на информационном входе 3 блока 1 памяти. Из узла 71 памяти микропрограмм „р сигнале U-. 1 на управляющем входе уЗ производигся считывание кода микрокоманды из ячейки с адресом, код. которого поступает на вход 72 с выхода регистра 74 адреса микрокоманд. Считанная микрокоманда поступает на нход 78 и записьюается в регистр 77 микрокоманд. Микрокоманда имеет два поля. Первое поле используется для адреса следующей микрокоманды. Ему соответству выход 80. Второе поле используется ддд кодирования управляющих сигналов. Ему соответствует выход 81. Несинхровизированные управляющие сигналы с выхода 81 поступают на вход 83 узла 82 сЬоомиоования управляющих сигналов. Этот узел содержит элементы И, каждый из которых соответствует определенному управляющему сигналу. На один вход элементов И подается несинхронизированный управляющий сигнал с входа 83, а на второй - тактовый импульс, поступающий :от генератора 86 тактовых импульсов управляющий вход 84. Синхронизация осуществляется таким образом, чтобы управляющие сигналы на выходах узла 82 соответствовали требуемой временной диаграмме работы устройства. В устройстве используется табличный способ реализации многоместньк 9 . логических функций. Предусмотрена воз можность выполнения команды реализации системы из четырех многоместных логических функций и команды реализации одной многоместной логической функции. С помошью этих команд может быть составлена программа дпя реализашга систем из любого числа функций. Таблицы реализуемых функций размешаются в выделенном сегменте накопителя блока памяти. Этот сегмент содержит Nj.-t - разрядных ячеек Для запоминания каждого элемента таблицы реализуемой функции используется один разряд. Таким образом, в выделенном сегменте может быть размешено М(П элементов таблиц. На фиг. 3 для пррстоты ,изрфажения показан небольшой сегмент накопителя блока 1 памяти,содержаший 32 ячейки с номерами 0-31; п 24. Сначала рассмотрим возможные способы размещения таблиц одиночных логических функций. Число аргументов Р реализуемой логической функции может бьпъ различны Если ,и«кг еоо:„-Мг . то для размеТ.МОКС f щения такой функции используется один разряд сегмента накопителя. Так в приме ре, показаном на фиг. 3,М 32,Р 5. В первом разряде сегмента, например. размещается таблица функции (Х„Х2,Х, Х4.,Х5- ). При .„С,КС одном разряде сегмента можноразмещать несколько таблиц, обеспечивая их плотную упаковку. Так во втором разряде покагзано расположение таблиц двух четырехместных функций 2( г fj ячейках О - 15 и 16 - 31, соответственно. В третьем разряде показано возможное расположение таблиц четырехместной логической функг ции ® ячейках О 15и двух трехместных: f5 (Хп.Х) в; ячейках 16 - 23 и (,(Х., .Xrj.Xj) в ячейках 24 - 31. Таблицы системы четырех логических функций должны размещаться в четырех соседних разрядах 4К+1, 4К4-2, 4К+3, 4К+4, ,1,... . Так на фиг. 3 в разрядах 5-8 показано расположение таблиц четырех пятиместных логических функций. Если число аргументов . о, гго для размещения таблицы может ть использовано несколько разрядов выделе ного сегмента, отстоящих друг от щзуга на четыре разряд а.Так, например, .об ласть накопителя, соответствующая 9 16разрядам выделенного сегмента может быть использовано для размещения 5110 таблиц четырех шестиместных Логических функций. На фиг. 3 для примера приведено раэ мещение таблицы шестиместной логической функции . Разрядах семнадцать и двадцать один. Функция может быть задана перечислением номеров Р, на которых она принимает значение 1. Так в рассматриваемом примере: ) (,В младшем из используемых разрядов(семнадцатом)размещены элементы табпиц, соответствующие младшим тридцатидвум номерам наборов 4 О - 31, а в старшем (двадцать первом) разряде соответствующие следующим тридцатидвум номерам наборов - 32 - 63. При этом в семнадцатом ряДе межПУ номером i набора и номером ячейки справедливо соотношение: N -I ). ® старшем (двадцать первом)разряде для иомера ячейки номера набог г г тиг.тоние.- N - 149 Р соотношение. IN 2.- i - 31). соответствии с принятой (фиг. 1) схемой соединений коммутаторов 46 ° информации, при выборе номера млал ° разряда для размещения таблицы функции с числом аргументов . ,с«кс®° °Д ° учитывать следующее условие: 1 Т. МО КС где .l,2...} X - ближайшее целое, не превьппаю wee X . Так, в рассмотренном примере для размещения таблицы выбраны разряды5р.„д 17и17 + . При этом приведенное выше условие выполняется , при t 2: .. 4 2-2. В соответствии с принятым способом сначала следует размещать т блшол Систем многоместных логических функций, затем одиночных функций с числом аргументов Р IT. макс далее в любые свободные разряды размещать таблицы остальных функций. Если число реализуемых логических функций В1елико и одного сегмента накопителя блока 1 памяти с числом ячеек NC недостаточно для размещения всех 1199 таблиц, то может быть выделено нескопько сегментов. Число сегментов накопителя, используемых для хранения табггаи, устанавливается при программировании задачи и не определяется жестко схемой устройства. Рассмотрим, как вьшолняется адресация к элементам таблиц. Адрес ячейки в блоке 1 памяти при обращении к таблицам формируется с помощью четВ(ртого канала мупьтиплексора 22 кода адреса. На вход 5 подается фиксированный код 1, являющийся адресом области накопителя, в которой могут размем щаться табшшл реализуемых функций. Код 2fe 111 11 соответствует номеру сегмента в выделенной области накопите. Таким образом, код является адресом сегмента накопителя, в котором размещены таблицы реализуемых функций. Код Хо-,оХ„,, доопределяет „ .. о адрес ячейки, в которой хранится результат реализуемых функций. Число разрядсш m2Q кода минимальному числу ,ц двоичных переменных, таблица логической функции от кото рых может быть записана в блок памяти. Если требуется реализовать логическую функцию от Р переменных , m 2 8 1 то ее следует представить как неполностью сшределенную функцию f от мин переменных: переменных (Хр ) Числа разрядов т в выделенных груп пах переменных согласпо их назначению и связям, представленным на фиг. 1, i. должны удовлетворять следующим уеловиям: ,кс-Н2 с1 , (); ). fn.-Wl am -m 45 2f 12 44 40 28 мйКс la I ()« гдеР.д..- максимальное число двоичны); переменных, логическая функция от кото 112 рых может быть реа;тзована с помощью одной кома1вды; NC - Ilcno ячеек сегмента накопителя в блоке 1 памяти, выделенного для хранения таблиц многоместных логических функций; ПЕ - максимальное число сегментов, которое может быть выделено для разме:щения таблиц реализуемых логических функций; m - число разрядов в коде адреса на входе 30 блока 1 памяти; Л - число разрядов в ячейках блока 1 памяти; индексы i у переменных т соответствуют номерам позиций на фиг. 1. Рассмотрим пример определения чисел разрядов ГП в вьщеленных группах переменных. Пусть NC 32, л 32, m 12, Иг 32,Р Используя .приведенные уравнения, получим:. 44 PMOKc- °s:z c a- °s:23 -3i , )H25f ()0; (тJg -tпJд+m)12- 2+0+S)5 40 28 Р«ако- 112 8- 3 -, ) Рассмотрим порядок подключения информационных входов 51 - 54 коммутаторов информации 46 - 49 к выходу 2 блока 1 памяти. В соответствии с принятым способом размещения таблиц систем многоместных логических функций и описанными выше связями управляющих входов 56 - 58 и выходов коммутаторов 46 - 49 информации первый разряд (младший) информационного вкода 51 (Xy-j С3 ) следует подключить к первому (младшему) разряду выхода 2 блока 1 пам1яти (YnCi) , и соответственно далее: , X54C1 Y2 4, 5, , в общем случае: 5lf 3 -H X52Cn-Y2 4(, Х5зСП- 2(-«И, Х54СП Ч2 40-1К4. Рассмотрим форматы команд реализац одной многоместной логической функции (код onepaiQiK К01) и реализации системы четырех многоместных логических функций (код (шераиии К02). Полям команД| имеющим различное функциональное назначение, на фиг. 1 сооггветствукуг следующие группы выходов реп-стра 6 команд: 7 - код операции; 8 - адрес операнда; 9 - код номе ра одного из четырех разрядов, сортветствующего таблице реализуемой логической функции (в команде реализации систем логических функанй это поле не ист ИОьзуется); нумерация разрядов начинается с нуля; 1О - код номера группы из 4 2 разрядов, в которой piacположены требуемые таблицы, нумеращш групп начинается с нуля (при fVrt это попе в формате команды отсутствует); 11 - код номера сегмента накопителя блока 1 памяти, в котором хранятся требуемые таблицы; 12 - код, уточняюший положение требуемой таблицы °РиР Р«аксОпределение кодов, соогветствукнких выходам 7 - 11 очевидно из их назначе ния. Рассмотрим методику определетшя кода 2 соответствующего группе выходо 12 регистра 6 команд. Для определения условий, в зависимости от которых опре., деляется код выделим в коде, храни мом в регистре 36 операнда, три состав ляющие: л V Го /Г. п максГ ЗьГ|«о1кс Л ) «кс((%)1Я поступает на вход блока 41 элементов ИЛИ, на ФУГОЙ вход которых подается код реализации Р-местной логической функции (или системы функций) код Л|ь макс()0...0, ;а код Уз(,Р 1тп4о+1) cooTBeTCTByiBT аваченням старших () разрядов вектора условий (операвда). При этом код Ьг J дополнять, только S114 своими старшими разрядами код, поступаюпшй из регистра 36. Цель такого дополнения-обеспечить адресацию элементов упакованных таблиц. Введем в рассмотрение перемвн1|уго . o P-ni40 При«31 т12 дополнения не требуется, при этом выделим в KoneYijN-fa две составляющие: y,2K2 12K2(3 fl°%Pl Вторая составляющая а Y()d I} соответствует тем разрядам формируемого блоком 41 элементов ИЛИ 41 кода, . которые содержат двоичные переменные вектора условий. Поэтому: 4,2Ca:i o...d При тфф код Y,,2 1 (первая составляющая кода 4„{|т . 1) соответствует номеру N группы из t 4 разрядов, в которой находятся требуемые таблицы; нумереьция начинается с нутхя. При в кодеХ 2 тя 2() выделим две части: 12К2 ( °Y«K5-H Код Ч,( является частью кода ЦоЧ|2рт 2 рый соответствует номеру N г группы ji3 четырех разрядов, в которых. находятся требуемые таблицы; нумёрапЕя групп начинается с нуля. ,5.(а+1) соответствует поMepyNf.j, группы из 2 ячеек, соответствующих положени1р требуемых таблиц в выделенномсегменте наксяттеля блока 7 памяти. Нумерация групп на шнается . Д иллюстрации методики .рассмотрим примеры определения кодов команд реализации многоместных логических функ- систем многоместных логических-фуйкций,ра иешение таблиц которых показано на фиг- 3, и при условии, что числа разрядов т.; в выделенных группах переме{шых соответствуют р(юсмотренному , выше пр1шеру. . Пусть сегмент с таблицами функций занимает начальные ячейки блока 1 памяти с адресами О - 31. Соотаетстеенно этому получим Cg- ОО. Для реализации логической функции f/,(X-|.... Ху) , таблица которой расположена в 1-м сегмента, получим следующий код команды . 15 где -| KOI (код операции команды реализации мнргоместной логической ф аии),У8 АО (адрес, операнда), 0 о отсутствует, У бОООО. Определим переменную о : () Y,,2r2Hj, Y,2C2 1J 00. Определим переменные: m -d 5-2-3 m ; 45.. соответствует номеру группы N,-H3 четырех разрядов, в которой находится таблица . Поскольку таблица размещена в первом разряд то Nr 0,V-,. 000. Таким образом; У-тгГ : 1 ООООО. В регистр 36 операнДа записывается аргумент: УЗ ОООХ5Х Х Х.2Х. Не выходах регистра 36 и блока 41 элем тов ИЛИ получим: , V4rX43VX Y3 8:4jVY,,(;5;i3 ((00000) ОООХ5Х ; 4443:- Y4 r5v3 000; ... Соответственно получим следукщий код на входе четвертого канала мульти племсора 22: B4P2:l -C,oX2(,oX2-,oX28 G5-«Y,-,oY45oY 00 ОООООХЛ Х Х.. 5 У i Таким офазом видно, что полученны код соответствует выбранному адресу с мента накопителя (ООООООО), а адрес ячейки в сегменте определяется наборо двоичных переменных вектора )( На управляющих входах 56-59 инфо мации получим: V5.:.V.,.4 Y44P: 00 На управляющем входе 6О коммутнт ра 50 информации получим: . о5-2 . Таким образом, на выходе коммутат ра 50 информации получим: Vl. S116 т.е. обеспечивается выделение разряда, соответствуклцего положению таблицы функции f. Рассмотрим код команды -jOVgoYqO otjpOYj pe ализадии функции f у (Х, X g, ), таблица которой размещена (фиг. 3) в третьем разряде ячеек 16 - 23:4- К01, 8 АО,у 10, Yfo отсутствует, ООООО. Далее, согласно изложенной выше методики получим: (3 P-m Qt:3-3 rOi. m.,,.. 3i ,,2:(,j, ) ,,,2.1. Код 2 tS : ЗЗ соответотвует номеру Np группы из четьфех разрядов, в которых находится таблица f ; согласно принятому выше расположению таблиц (фиг. 3) таблица Fg находится в третьем разряде, относящемся к первой группе с номером М(- О, поэтому У 2Г53 000; код V.2 f : 1 соответствует номеру р|„ группы из 2 2-8 ячеек, соответствующих положению таблицы функции fj; согласно фиг. 3 таблица расположена в ячейках 16 - 23, что соответствует третьей труппе ячеек по 8 с номером Нгя 2 (нзт серация с нуга) %2 окончательно поэтому получим: 00010. При выполнении команды получим: Y,J8 : 1 ООООО Хз,Х2,Х У4оГЗ Ax2Xi. (. 8 : 4:i v VV V - - 3.2Xl Н Yi2r5 : 1 (ООООО) V (00010) ОО01О; 7 l 44lC5 : 3} OOO,Y45i:2.: l ад2 : 1 10; 84 12 : ib VYi.oY4cO 4o ОООООООЮХзХгХ-. Полученный код соответствует адресt восьми ячеек 16 - 23. Выбор одной из восьми ячеек осуществляется кодом XjXnX, соответствукяцим набору переменных реализуемой функции. На управляющих входах коммутаторов информации 46 - 50 получим: : 1 ... V59C3 : 1 V o°V44 YHt3 : 1 000;Vj jjC2 : 1 №: 10. Соответственно получим: (,2C3 48 ifnl3J, что соответствует положению таблицы реализуемой функции. Рассмотрим коД команды реализации логической функции i (Х... X ), табли:;ца которой занимает несколько (два) раэтаблица функции f-jy размещена в семнад цатом и двадцать первом разрядах: Ч-| KOl.Ye АО. КодУ912:Л определяет попоже1ше требуемого разряда с , табтгацей в группе из четырех разрядов. Семнадцатый и двадцать, первый разряды - первые в соответствукишос четверках разрядов (фиг. 3). ПоэтомуVq ОО У| 00000. Определим код У-}2Г5 : 1 : 40 6 - 3 Ф 3; 12- 5.,.3 2 m4;j;, 4-2 Ь-3-2 , 8. Согласно фиг. 3 таблица функции f-j5 находится в третьей группе разрядов по t 8, соответственно получим Nr 2, Vi2tm-,2() ° О (нумерация групп начинается с нуля); Yi2 : 13 000; 4, : 1 1000О. Коды в команде реализации системы многоместных логических функций выби раются по той же методике. Код может быть любым. В частности можно принять Чд 2 : 1 ОО. Для примера рассмотрим составление кода крмандь для реализации системы логических функций ,-- f 14 таблицы которых размещены в разрядах 9-16, число аргументов Р 6. Y-} - КО2 (код операции команды реализации системы многоместных логичес ких функций); УЗ ДО; Yg ОО (не используется), Y-IO не используется, V-f-j « ООООО.. Определим код V-j2l 5 : d Р -т 5 - 3 tl 42P- 4o- 45 ; Nr « 2,Yi2.,) t5 - ,O1; Vi2C -l3-Vi2t3 : 000, Y-i2t5 : 1 01000. Окончательно получим код командах: ко2::АО-оо ооооо оюоо. Рассмотрим работу устройства при выполнении команоы реализации системы многоместных логических функций с использованием описанного, выше способа размещения таблиц н составления кода команды. Работу можно представить с цо мошью следующей функциональной микропрограммы. Микропрограмма реализации системы многоместных логических функций. НАЧАЛО. г-Wi e2-Yg ) P 4r;fPi«ciRC по адресу, код которого поступает с выхода 8 регистра 6 команд через второй канал (вход 24) мультиплексора 22, и запись PMQKC младших разрядов считан- него кода в регистр 36 операнда) М2. , ) 2f -Y2D-(H3),u(Y,oOY4,i); / C считывание из накопителя блока 1 t . памяти содержимого ячейки, хранящей результаты реализуемых функциЙ выделение с помощью коммутаторов 46 - 49 информации четырех разрядов, соответст вуюших результатам реализуемых функций и запись их в регистр 61 резуяьтата). КОНЕЦ. Для вьшолнения этой микропрограммы блоком 32 микропрограммного управления формируются следующие управляющих сигналов, соответствукпдае представленным вьше алгоритмам функционирования операционных блоков. М1,У2э 01; 31 Ю; из8 1. M2.V29 3 1На структурном уровне представления устройства (фиг. 1).его работа рассмат ривается в дискретном времени. За дискрет принято время цикла Т обращения к блоку 1 памяти. Для реализации требуемой временной диаграммы цикл Т« делится на такты с помощью тактовых импульсов, вырабатываемых генератором 86 тактовых импульсов, и управлякяцие сигналы на выходах 34, 35 блока 32 микропрограммного управления в узле 82 синхронизирутстгся соответствукишми тактовыми импульсами. На фиг. .4 показаны три цикла работы устройства: цикл считывания команды системы многоместных логических ций и два цикла ее выполнения, соответствующие приведенной выше микропрограмме. СигналыCg l , ... Cgj|f4 цредставлякгг тактовые импутшсы на выходе генератора 86. На фиг. 4.Т1риведейЙ временные диаграммы упра вляю щихсйгналов У.,, и. а также показаны моменты времени, когда происходят изменения многорезряд ных переменных V2g 31 После управпякших сигналов в формате микрокоманды, которому соответствует выход 81 регистра 77 микрокоманд (фиг. 1) срдержит несколько подполей, иЬпользуемых для кодирования разл1 чных управляющих сигналов. Между ними может быть установлено, например, следую щее соответствие: 2113} , 81 Vfl.D43 В узле 82 осуществляется синхронизация управляющих сигналов в соответст вии с вре} 4енноД1 диаграммой: VY34№ 8lW-C8«,. V,8 Y34p:2 Y8,.4., , te V®-3 V3i-Y34flO:9 Yg,lO;3.( ,,l Y,,WCg,C4) Чз- 351:21 вД127.Св, (,) )Работа блока 32 мш-ррпрограммного управления происходит следующим образом (фиг. 1 и фиг. 4). В первом такте первого инкпа происходит считывание ко да микрокоманды на узла 71 памяти ми ропрограмм по адресу, поступающему с выхода регистра 74 адреса микрокоманд В начале второго такта считьтания микр команда записывается в регистр 77 мик рокоманд. В третьем такте осуществляется считывание дчередной команды из блока 1 памяти по адресу, поступающему из счетчика 15 команд. В четвертом такте считывания кх манда записывается в регистр 6 команд, содержимое счетчика 15 команд увеличивается на едштпу код операцнв, соответствукиглй адресу первой микрокоманды требуемой мнкропр граммы, записывается по входу 33 в регистр 74 адреса микрокоманд. Работу устройства в втором и третьем циклах можно проследи1Ъ по (фиг. 4) диаграмме с исполызованием рассмотренной выше ми1фопрограммы. В этих циклах адрес следующей микрокоманды поступает в регистр 74 с выхода 8О регистра 77 микрокоманд. В третьем цикле выполняется вторая (последняя) микрокоманда рассматриваемой микропрограммы. Поэтому за ней догокна следовать микрокоманда считывания очередной команды, выполнение которой было рассмотрено в первом цикле. Рассмотрим работу устройства при выполнении команд записи результата реализации системы многоместных логических функций из регистра 61 в блок 1. памяти. Возможны два случая: решения, принимаемые на наборах двоичных переменных 1вектора условий не являются альтернативными и могут приниматься в любых сочетаниях и случай альтернативньсс решений, когда на каждом наборе может быть принято одно и только одно решение. В последнем случае с целью экономии памяти номера решений следует кодировать. Пример кодирования альтернативных решений i принимаемых на наборах двоичных переменных вектора условий X (Хц., X,, ;L,X.,), и получения функций V (Х, Х, X,))УДХ.,.. представлен на фиг. 67 В командах внвода результата из регистра 61 и записи его в блок 1 памяти адрес ячейки указавается в поле адреса первого операнда, которому соответствует выход 8 в регистре 6 команд. Работу устройства можно представить с помощью следующих микропрограмм. Микропрограмма вьгаода результата из регистра 61 решений без дешН рв-11ии. НАЧАЛО. Ml. А В2 Ув; ХэС4 : 1 J : Yfci 4:l3j HfA) : 1 (Запись в блок 1 памяти слова, 4 младших разряда которого соответствуют содержимому регист ра 61.). КОНЕЦ. При этом формируется следующий набор управляющих сигналов:: M1.V29 01; V3i« 111 Ufeg 1..Мякрсжрограмма вывода результата из регистра 61 решений с дешифрацией. НАЧАЛО. Ml.AcB,Yg; Хзрб. / H(A -XjtnH ; (запись Б блок 1 памяти слова, 16 младших разрядов которого соответствуег сигналам на выходе дешифратора 64.). КОНЕЦ. При этом формируется следующий набор управляющих сигналов: М1.29 01« 31 llJ 1Рассмотрим особенности работы устройства при вьшопнении команды условного перехода по результату реализации .многоместной логической функдии. При этом выполняется следующая микропрограмма. Микропрограмма реализатга многомес ной логической функции. НАЧАЛО. М1.,); .Ч2,, ( Считывание операнда из блока 1 памяfll по адресу, поступающему с выхода 8 регистра 6 команд, и запись Р. младразрядов считанного кода в регистр ших 36 операнда ). W (ЛЛ) V v n 2 CKf5 ;- CKi5 +4 (Считывание из блока 1 памяти содержи мого ячейки, хранящей результат реализуемой функции, выделение i -го разряда, соответстаукшего этому результату; модификация содержимого счетчика 15 ко манд при влением результата реализации многоместной логической функции.). КОНЕЦ. При выполнении микропрограммы формируются следующие наборы управляющих сигналов. Ml. V29- 01; V3 10; UJB Ij M2.V29 11; V3 lO; V21 OOO; 18 11в сравнении с использованием програм много метода для вычисления систем мног местных логических функций рассмотренно устройство позволяет экономш-ь ячейки памяти для хранения программ, упростить программирование и увеличить & ютродействие. Проведенные расчетные оценки показы вакгг, что затраты времени ориентировочно уменьшаются в 28 раз, вместо 116 команд при программном методе в описан ном устройстве требуются две команды (команда реализации системы логических 99 122 функций и команда вывода результат на каждую систему реализуемых функций экономия памяти составляет 3584 бит. Фармула изобретен.и я Устройство для выполнения команд реализации систем многоместных логических функций, содержащее блок памяти, регистр команд, счетчик, коммутатор условия перехода, мультиплекссф а/фесных кодов, выход которого соединен адресным входом бпока памяти, блок мивропрограммного управления, вкод которого соединен с первым выходом регистра команд, информационный вход которого соединен с информационным выходом ёлока памяти, являющимся выходом устройства. информационный вход бпока памяти является первым входом устройства, первый информационный вход мультшшеясора адресных кодов подключен к выходу счетчика команд, второй информационный входк второмувыходу регистра команд, третий информационный вход соединен с третьим, четвертым, пятым и щестым выходами регистра команд, информационный вход счетчика команд соединен с информационным выходом блока памяти, счеттаай вход счетчика команд подключен к выходу коммутатора условия перехода, первый информационный вход которого является вторым входом устройства, управляюпше входы бпока памяти, регистра команд, счетчика команд, коммутатора условия перехода и мультиплексора адресных кодов соединены с первым выходом бпока микропрограммного управления, отличающееся тем, что, с.цельЬ nt выщения производительности в него введены регистр операнда, блок элементе ИЛИ, пять коммутаторов информшши, регистр результата, дёпгафратор и две группы переключателей, причем информа-к ционные входы регистра операнда и с первого по четвертый коммутатсфов информации соединены с инфсфмационным выходом бпока памяти, выходы первого второго, третьего и четвертого коммутаторов информации соединены .с ) цнонными всодами регистра результата и пятого коммутатора информации, выход которого подключен к второму информационному входу коммутапгора условия перехода, выход регистра результата соединен с информационными входами переключ чателей первой группы и депшфрацрра, выкбй которого подключен к ииформацион:мым Еходам переключателей второй группы, а выходы переключателей первой и -второй групп соединены с соответствую:Шикга разрядами информационного входа блока памяти, управляюише ЕКОДЫ регист- 5 ра шеранда, регистра резутштата, переключателей первой и второй групп соедийены с вторым выходом блока микропрограмiviHoro управления, управляющий вход пятого коммутатора информации соединен с треть-0 им выходом регистра команд, управляющие входы с первого по четвертый коммутаторов информаюга соединены с четвертым выхо дом регистра команд и с первым выхо-., дом блока элементов ИЛИ, первые входы i которых подключены к шестому выходу регистру команд, а вторые входы - к первому выходу регистра операнда, четвертый и пятый информационные входы мультиплексора адресных кодов соединены соотвео 20 ственно с пятым выходом регистра команд и вторым выходом блока элеметхтов ИЛИ.вторрй выход регистра операнда подключен к шестому )орм анионному вхид мультиплексора адресных кодов, седьмой информационный вход которого соединен с третьим входом устройства.

Источники информации, принятые во внимание при экспертизе

1.Девятков В. В. Программная реализахшя управляющих алгоритмбв. - Автоматизированное проектирование дискреных управляющих устройств. М., Наука, 1980, с. ЗО-47.

2.Опубликованная заявка Франции № 2378311, кл. G, 06 F 9/06, 0,06 Р 15/46, 1978.

3.Авторское свидетельство СССР № 640300, кл. G, 06 F15/00, 1976 (прототип).

К Jf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для табличной реализации многоместных логических функций | 1982 |

|

SU1019455A1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для выполнения условного перехода | 1981 |

|

SU999053A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

65

1

-3

87

r-,R

J

Фиг. 2

№.

ФигЛ

Фиг. 5

Авторы

Даты

1983-02-23—Публикация

1981-07-31—Подача