(54) ФОРМИРСЖАТЕЛЬ АДРЕСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь адреса сканирующей системы | 1973 |

|

SU447713A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275520A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ | 1990 |

|

RU2032218C1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ЗНАКОВ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2023314C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2042202C1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2042201C1 |

1

Изобретение относится к устройствам управления, в частности, оно может быть использовано для управления сканирование луча фазированной антенной решетки и для управления сканированием луча в индика- торак радиолокационных станций.

Известен формирователь адреса сканирующего устройства, содержащий адресный с;четчик, сумматор, датчик коррекции, преобразователь, блок памяти исходных дан™ ных, блок памяти сектора сканирования и блок управления, причем первый и второй входы адресного счетчика соединены с выдом сумматора ы первым выходом блока управления соотвеч-ственно, первый и вто- IHJH входы блока памяти сектора сканиро- lifiiiifH связаны с цервым выходом блока 11амЯ И исходных Дг1НН1)1х и вторым выходом блока управл1 лия соответственно, а ihpisi.iH выход - с: первым входом блока yii|,i.4iiJu;HHH, первые входы памягИ исходник ;i.-iHHbLX и пр1образова1-1 ля соединены с третьим и четвертым пыходами блока У11|);1вл1:нин соотв(;т ;твенн(.|, а второй вход

I преобразователя - с выходом датчика коррекции.

Цель изобретения - обеспечение возможности слежения з изменениями кординат объекта с одновременным обзором всего кадра.

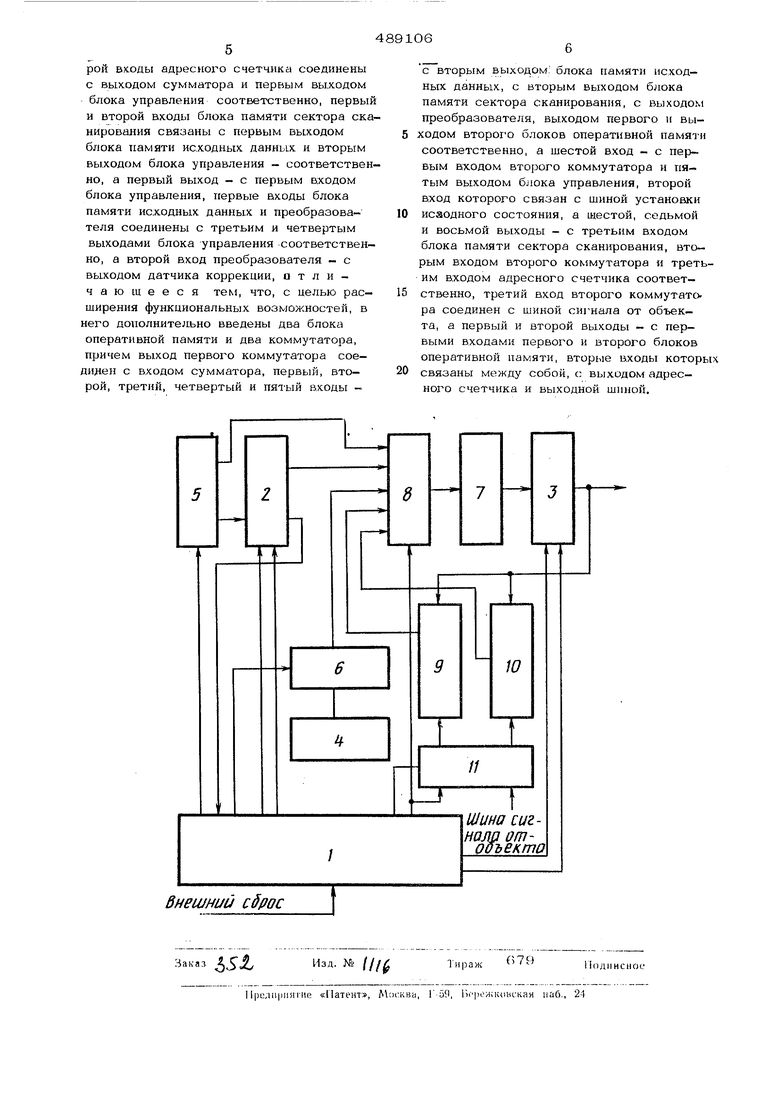

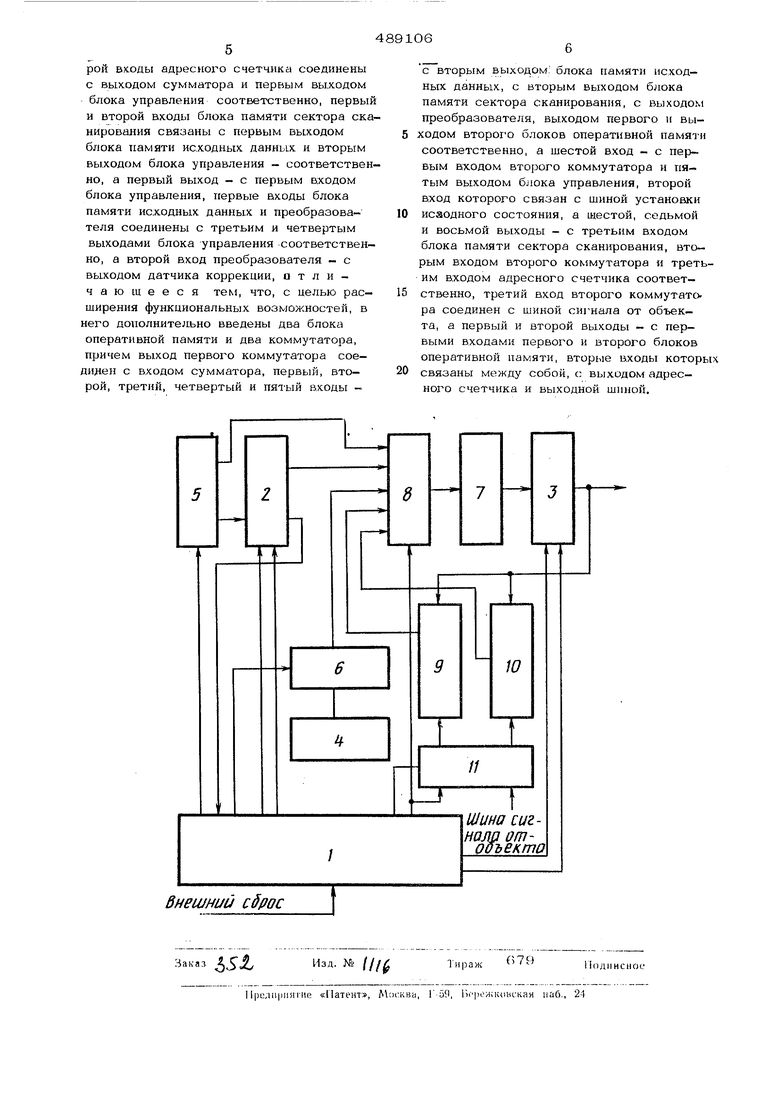

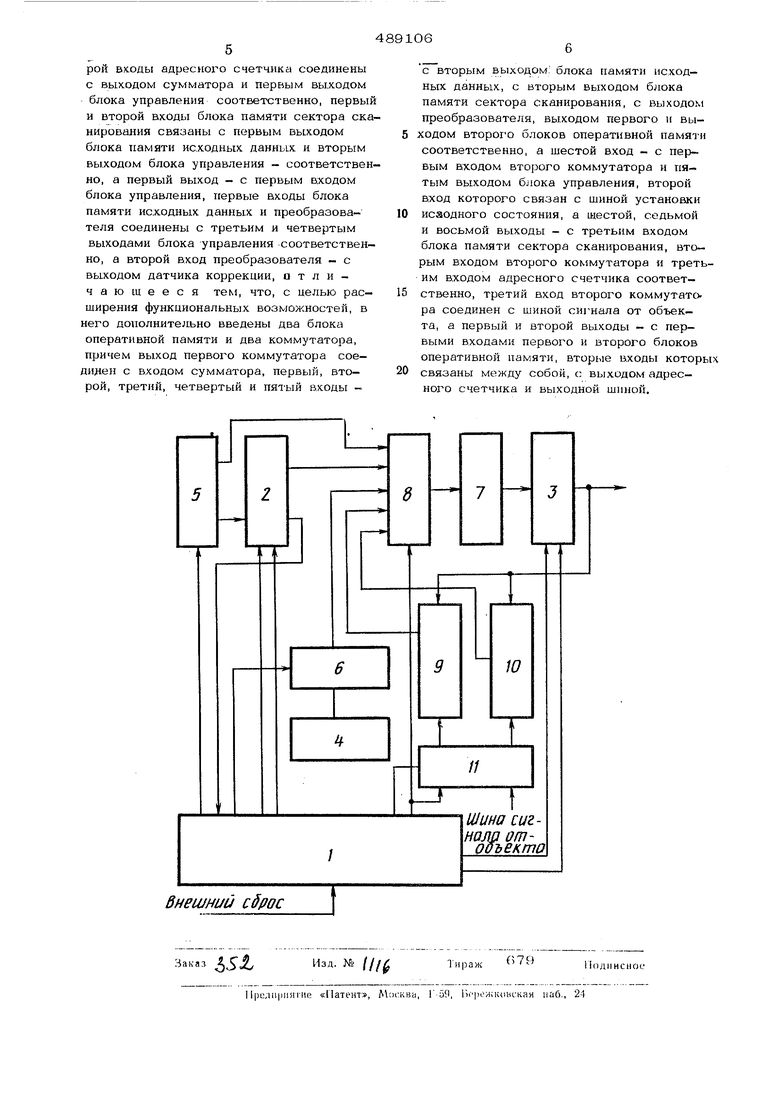

Для ее осуществления в предлагаемое устройство дополнительно введены два блока оперативной памяти и два коммутатора, причем выход первого коммутатора соединен с входом сумматора, первый, второй, третий, четвертый ij пятый входы - с вторым выходом блока памяти ИСХОДНЬЕХ данных, с вторым выходом блока памяти сектора сканирования, с выходом преобразователя, выходом первого и выходом второго блоков оперативной памяти соответственно, а шестой вход - с первым входом второго коммутатора и пятым выходом блока управления, второй вход которого связан с щиной установки исход, ного состояния, а шестой, седьмой и восьмой выходы - с третьим входом блока памяти сектора сканирования, вторым вхо дом адресного счетчика - соответственно третий вход второго коммутатора соединен с шиной сигнала от объекта, а первы и второй выходы - с первыми входами перво1 о и второго блоков оперативной па мяти, вторые входы которых связаны меж ду собой, с выходом адресного счетчика и выходной шиной. На чертеже приведена блок-схема формирователя адреса. Предлагаемый формирователь содержит блок 1 управления, блок 2 памяти сектор сканирования, адресный счетчик 3, датчик 4 коррекции, блок 5 памяти исходных дан ных, преобразователь 6, сумматор 7, пер вый коммутатор 8, первый блок 9оперативной памяти или ОЗУ нечетно1Х) кадра, второй блок 10 оперативной памяти или ОЗУ четного кадра и второй коммутатор 11. Работа формирователя адреса происходит следующим образом. При подаче сигнала внешнего сброса по шине установки исходного состояния блок управления 1 обеспечивает установку блока 2 памяти сектора сканирования, адресного счетчика 3, первого блока 9 оперативной памяти (ОЗУ нечетного кадра и второго блока 10 оперативной памяти (ОЗУ четного кадра) в исходное состояние. После этого блок управления 1 обеспечивает перезапись исходных данных из датчика 4 коррекции и блока 5 памяти исходных данных через преобразователь G блок 2 памяти сектора сканирования, коммутатор В,и сумматор 7 в адресный счетчик 3. Затем блок управления 1 обеспечивает подачу импульсов с частото f J на счетные входы адресного счетчи ка 3 и на вход,..блока 2 памяти сектора сканирования, что приводит к изменению адреса на выходе адресного счетчика 3. При этом счетный вход адресного счетчика ОЗУ нечетного кадра 9 подключен к шине сигнала от объекта через второй коммутатоо 11, а счетный вход адресно- I о счетчика ОЗУ четного кадра 10 подклюП1.П) через второй коммутатор к выходу блок управления 1. При появлении от объекта адресный счетчик ОЗУ нечетного кадра 9 устанавливается в состояние подкл11)чпя тем самым на время сущест- 11онания сигнала первый регистр ОЗУ нечетного кадра 9 к выходу адресного .счет чика 3, в котором производится запись к{.10рдинаты первого объекта. При заданно частоте повторения опроса объектов, устанавливаемой в блоке управления 1 и определяемой заданным количеством имiiyjH.coB, поступающих на счетный вход адресного счетчика 3, на выходе блока управления 1 возникает импульс. Этот мпул.ьс устанавливает адресный счетчик ОЗУ четного кадра 10 в состояние 1, что обеспечивает перезапись координаты первого.объекта из регистра ОЗУ четного кадра 10 и блока памяти исходных даннь1х 5 через первый коммутатор 8 сумматор 7 в адресный счетчик 3. При этом выходы преобразователя 6 и блока 2 памяти сектора сканирования отключены от входов J су м тора7. В преобразователе 6 и блоке 2 памяти сектора сканирования запоминается последняя координата пер- вого просмотренного участка нечетного кадра. Из блока управления 1 поступает пачка импульсов (например, состояшая из семи импульсов), следующая с частотой Л (/2 ) После прохождения послед него импульса этой пачки блок управления обеспечивает перезапись последней координаты первого просмотренного участке кадра из -преобразователя 6 и блока 2 памяти сектора сканирования через первый коммутатор 8 и сумматор 7 в адресный счетчик 3. При этом в.ходы сумматора 7 отключены от выходов ОЗУ четного кадра 10 и блока 5 памяти ис.ходных данных. 11о( ле этого блок 1 управления обеспечивает подачу импульсов с частотой А на счетные входрл адресного счетчика 3 и блока 2 памяти сектора сканирования, что позволяет осуществить просмотр второго участка не четного кадра. С появлением импульса на выходе блока 1 управления вновь происходит уточнение координаты второго объекта с записью уточненной координаты во торой регистр ОЗУ нечетного кадра 9. Tkx.v. ле этого производится просмотр третьего участка нечетного кадра и т.д. После прос:мотра всего кадра на выходе блока 2 памя ти сектора сканирования возникает имну. обеспечивающий подключение ОЗУ нечетиоги кадра в режим работы выдачи координат объектов, записанных при просмотре первого кадра, а ОЗУ четного кадра - в режим приема уточненных координат от объекта. Этот же импульс устанавливает формирователь адреса в исходное состояние, после чего цикл работы повторяется. Предмет изобретения Форм1фователь адреса, содержащий адресный счетчик, сумматор, датчик коррекции, преобразователь, блок памяти исходны; данных, блок памяти сектора сканирования и блок управления, причем первый и второй ЕХ.ОДЫ адреснох о счетчика соединены с выходом сумматора и первым выходом блока управления соответственно, первый и второй входы блока памяти сектора сканирования связаны с первым выходом блока памяти исходных данных и вторым выходом блока управления - соответственно, а первый выход - с первым входом блока управления, первые входы блока памяти исходных данных и преобразователя соединены с третьим и четвертым выходами блока управления соответственно, а второй вход преобразователя - с выходом датчика коррекции, отличающееся тем, что, с целью расширения функциональных возможностей, в

него дополнительно введены два блока оперативной памяти и два коммутатора, причем выход первого коммутатора соедидел с входом сумматора, первый, второй, третий, четвертый и пятый входы с вторым выходом блока памяти исходных данных, с вторым выходом блока памяти сектора сканирования, с выходом преобразователя, выходом первого и выходом второго блоков оперативной памяти соответственно, а шестой вход - с первым входом второго коммутатора и пятым выходом блока управления, второй вход которого связан с шиной установки исаодного состояния, а шестой, седьмой и восьмой вьпходы - с третьим входом блока памяти сектора скашфования, вторым входом второго коммутатора и третьим входом адресного счетчика соответственно, третий вход второго коммутато ра соединен с шиной сигнала от объекта, а первый и второй выходы - с первыми входами первого и второго блоков оперативной памяти, вторые входы которых связаны между собой, с; выходом адресного счетчика и выходной шиной.

7

8

Авторы

Даты

1975-10-25—Публикация

1972-10-31—Подача