Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем отображения алфавитно-цифровой и буквенно-мозаичной информации.

Цель изобретения - расширение области применения устройства за счет возможности отображения подстрочных и надстрочных индексов и буквенно-мозаичной информации и повышение его быстродействия за счет увеличения скорости обмена путем использования независимого от фаз регенерационного цикла обмена.

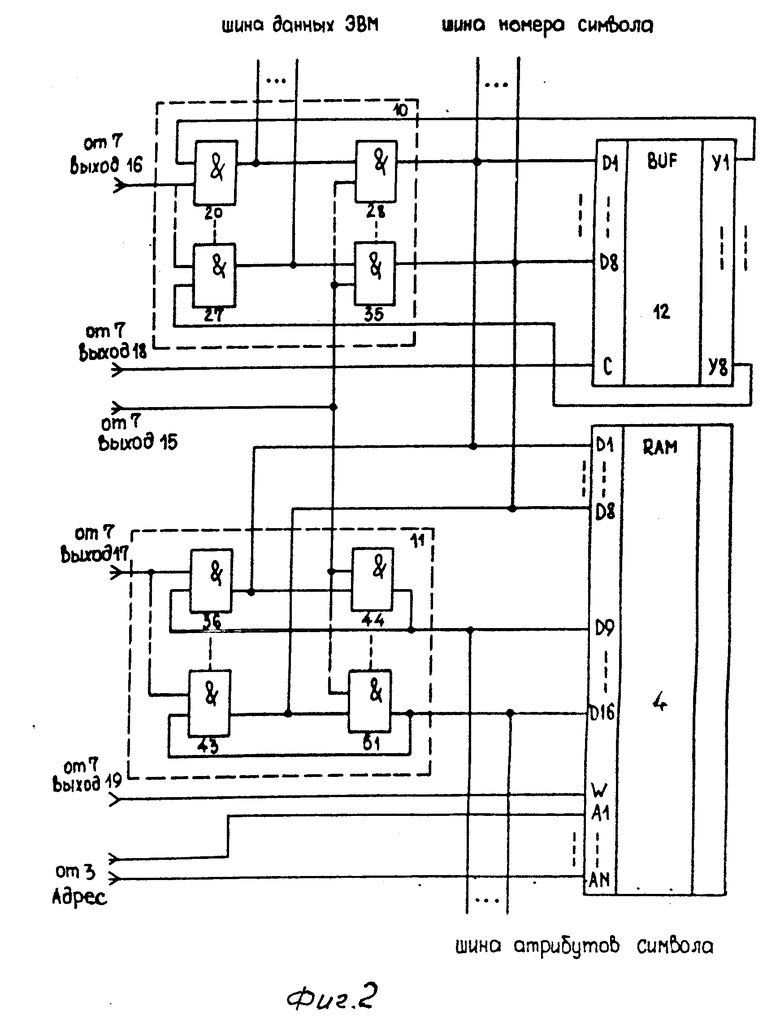

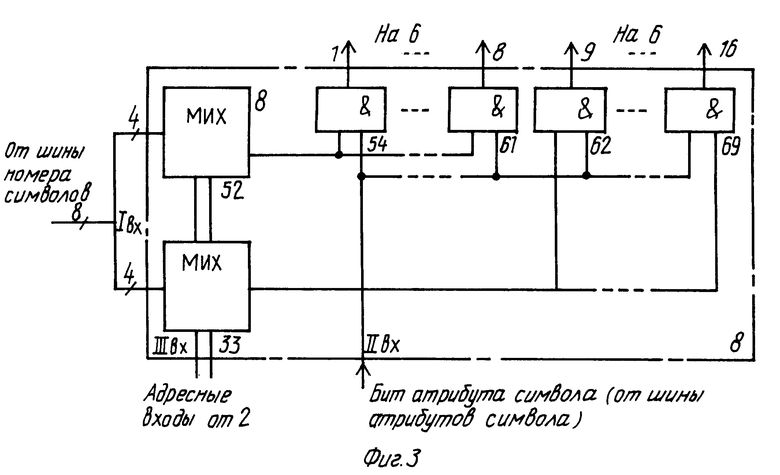

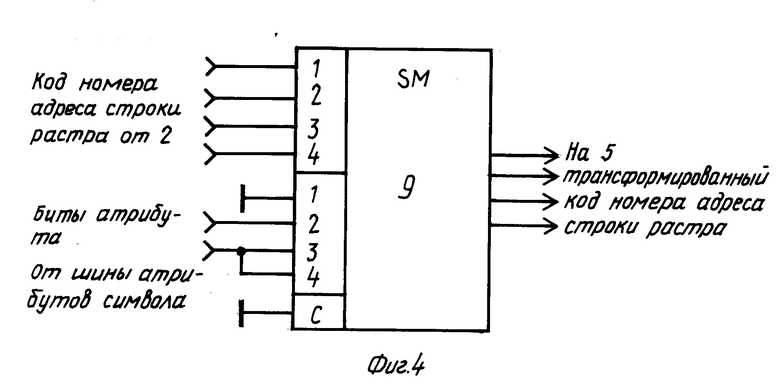

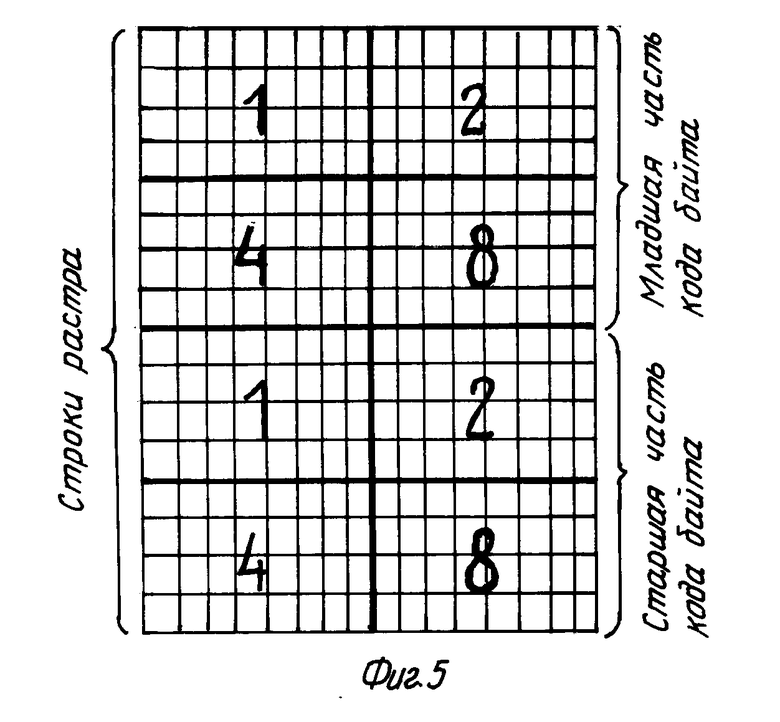

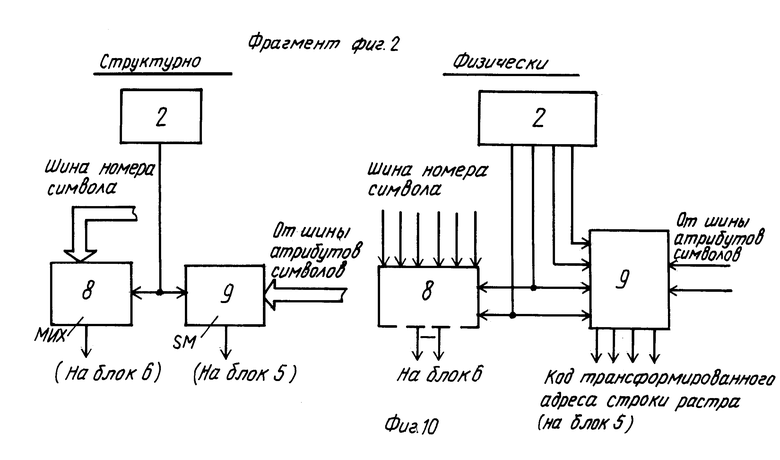

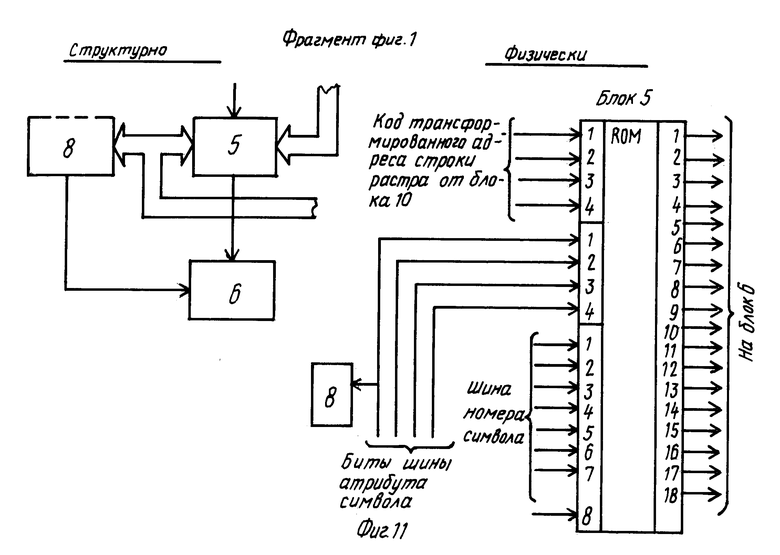

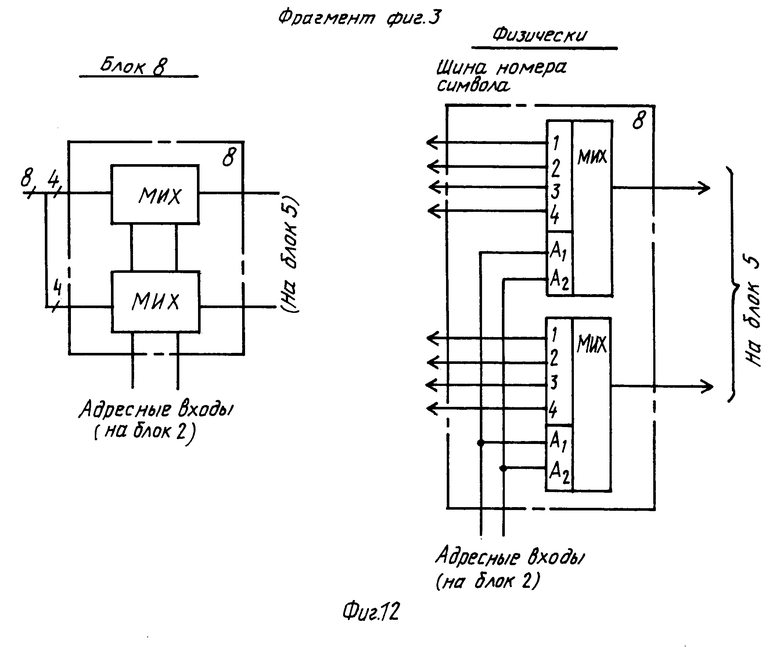

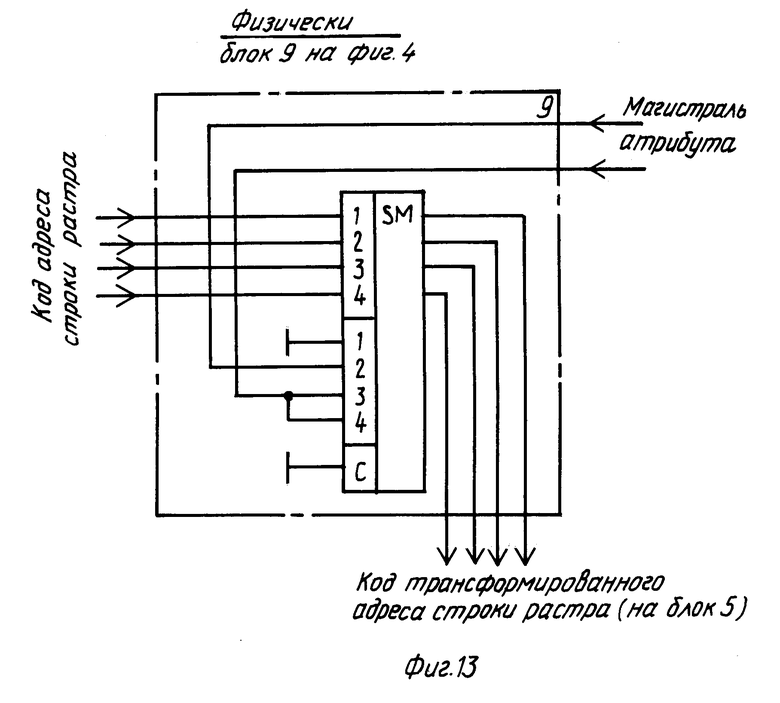

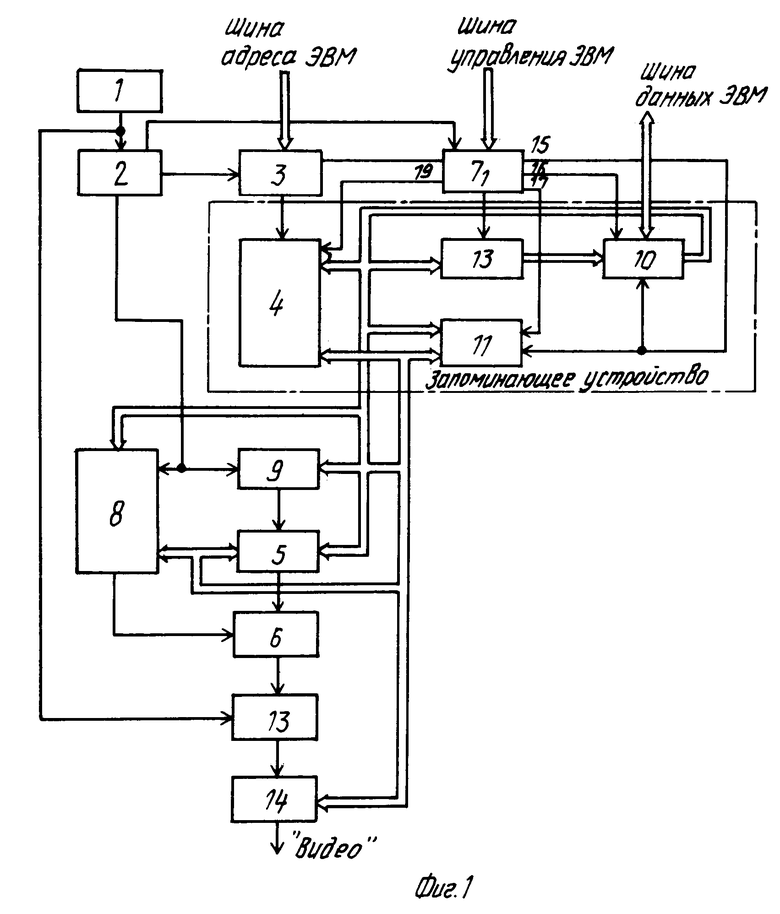

На фиг. 1 представлена структурная схема предложенного устройства; на фиг. 2 - структурная схема блока запоминающего устройства; на фиг.3 - формирователь управляющих сигналов; на фиг.4 - сумматора; на фиг.5 - пример кодирования буквенно-мозаичной информации; на фиг.6 - пример кодирования мозаичного символа; на фиг.7 - пример изображения надстрочных и подстрочных символов; на фиг.8 - блок-схема блока управления; на фиг.9 - преобразователь кодов; на фиг. 10 и 11 - фрагменты фиг.1 - структурно и физически; на фиг. 12 - фрагмент фиг.3 - структурно и физически; на фиг.13 - сумматор. На фиг. 11-13 дополнительно изображены фрагменты структурной схемы, показанной на фиг.1 с целью объяснить ее связи, которые будучи однопроводные и многопроводные (не магистральные) графически изображены одинаково, при этом каждый функциональный блок подключается к многопроводной линии только к необходимым проводам.

Устройство содержит генератор 1 синхроимпульсов, счетчик 2 адреса регенерации, коммутатор 3, блок 4 оперативной памяти, блок 5 постоянной памяти, блок 6 элементов ИЛИ, блок 7 управления, формирователь 8 управляющих сигналов, сумматор 9, первый 10 и второй 11 блоки элементов И, буфер 12, преобразователь 13 кодов, блок 14 кодирования.

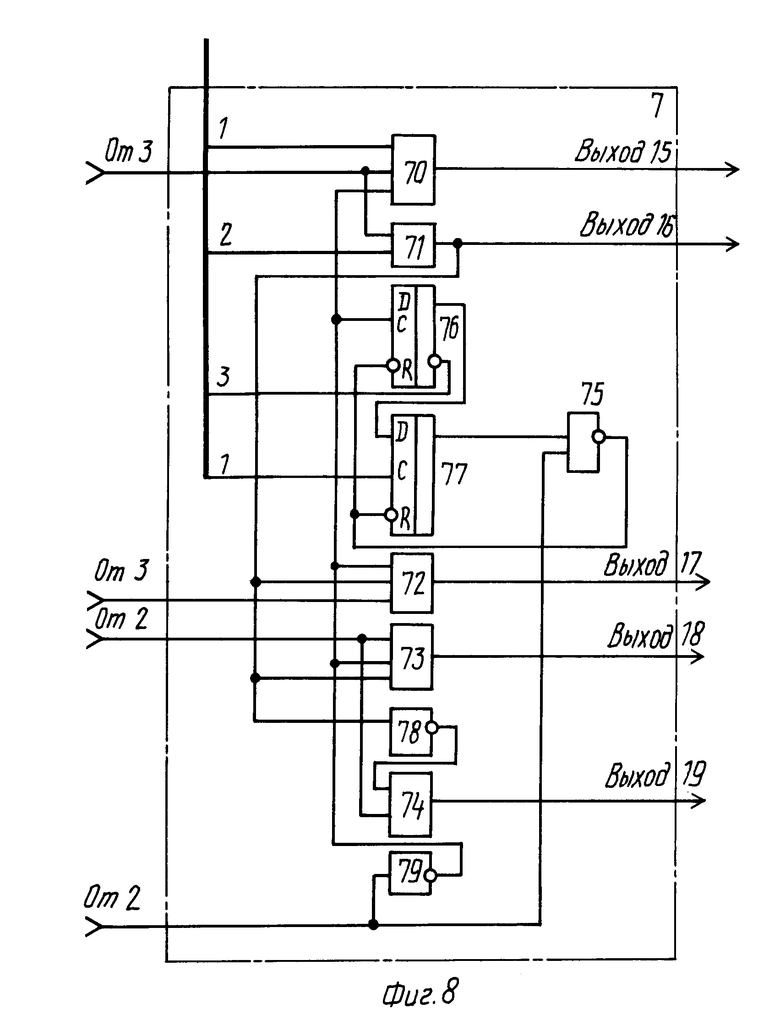

Позициями 15, 16, 17, 18 и 19 обозначены выходы блока 7 управления.

Блок 10 содержит элементы 20-35 И, а блок 11 содержит элементы 36-51 И.

Формирователь 8 управляющих сигналов содержит мультиплексоры 52 и 53, элементы 54-69 И.

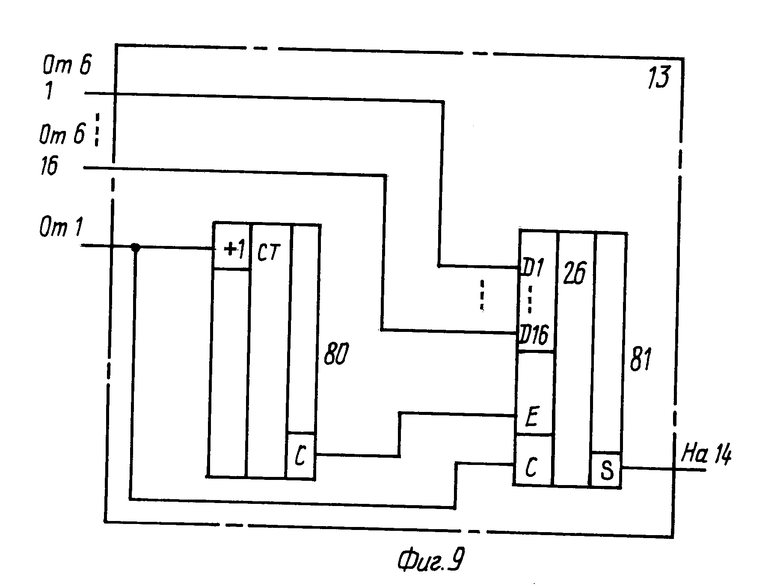

Блок 7 управления содержит элементы И 70-74, элемент 75 И-НЕ, D-триггеры 76 и 77, элементы 78 и 79 НЕ. Преобразователь 13 кодов содержит счетчик 80 и регистр 81 сдвига.

По каждому из проводов шина связи с коммутатором 3 из блока 7 управления поступают сигналы, которые коммутатором 3 используются в качестве синхроимпульсов и сигналов селекции.

Использование буфера в решении проблемы согласования записи информации из ЭВМ на оперативное запоминающее устройство (ОЗУ) предусматривает следующие режимы работы с оперативным запоминающим устройством регенерации: независимого доступа ЭВМ, последовательного доступа, прямого доступа узла регенерации к ОЗУ.

Недостатком режима независимого доступа ЭВМ является появление помех на экране дисплея в процессе редактирования информации и обмена данными, вызванных асинхронным прерыванием процесса регенерации.

Режим последовательного доступа предусматривает последовательное обращение к ОЗУ. В этом режиме ЭВМ переводится в состояние ожидания при обращении к ОЗУ, работающему с узлом регенерации. Выход из этого состояния осуществляется посредством со схем регенерации. Указанные сигналы выдаются при обращении к ОЗУ со стороны узла регенерации во время обратного хода луча ЭЛТ дисплея по строке и по кадру.

Режим прямого доступа узла регенерации к ОЗУ характеризуется тем, что ОЗУ регенерации рассматривается как ОЗУ процессора и узел регенерации организует прямой доступ к нему путем перевода микропроцессора в режим "захвата" с блокировкой его работы на период регенерации информации, что снижает производительность системы.

Предлагаемое устройство использует режим независимого доступа ЭВМ, но в отличие от вышеописанного не способствует появлению помех на экране.

Это достигается тем, что время работы разделяется на два периода: период использования ОЗУ для регенерации и период других возможных использований ОЗУ, т.е. запись информаций от ЭВМ в ОЗУ, считывание информации от ОЗУ на буфер с последующим асинхронным считыванием его ЭВМ.

В известных устройствах связи контроллера видеомонитора, имеющего оперативное запоминающее устройство (ОЗУ), с микропроцессором возможна без появления помех на экране только во время обратного хода луча ЭЛТ по строке или по кадру. Это составляет половину времени действия видеомонитора, что, задерживая выдачу сигнала "готовность", замедляет операции обмена информацией и снижает быстродействие устройства формирования знаков в целом.

В предлагаемом устройстве такого ограничения нет, так как половина времени вычерчивания растровой строки каждого знака используется для связи блока 4 (ОЗУ экрана) с микропроцессором, а другой половины времени достаточно, чтобы обеспечить регенерационный фрагмент, т.е. чтобы загрузить преобразователь 13 кода данными об растровой строке знака. Частота следования знаков при регенерации больше, чем максимальная возможна частота обмена микропроцессора.

Таким образом, моменты возможной связи микропроцессора с ОЗУ контроллера видеомонитора являются чаще, чем тактовая частота микропроцессора и задержки обмена существенно уменьшаются. В известном устройстве (прототипе) максимальная задержка соответствует длительности видимой части строки растра.

Изложенные соображения можно проиллюстрировать таким примером. Если в растровой строке знака имеется 16 точек, в одной строке изображения размещается 48 знаков, а тактовая частота равна 20 МГц, то в известном устройстве задержка составляет 50х16х48=38,4 мкс.

В случае использования предлагаемого технического решения задержка составит

50х16=0,8 мкс.

Данный пример показывает, что задержка уменьшается, а следовательно, быстродействие повышается в данном примере в 48 раз.

Таким образом, положительный эффект от использования предлагаемого технического решения в отношении повышения быстродействия очевиден.

Особенностью предлагаемого устройства является возможность осуществить независимый от регенерационного цикла обмен ОЗУ с ЭВМ, при этом схема устройства построена таким образом, что обмен с ЭВМ происходит посредством шины данных байтами, а считывание при регенерации, осуществляется по двухбайтовыми словами и тем самым обеспечивается возможность выполнить регенерацию более точных символов - с большим числом сегментов и атрибутов символов, чем позволяет ширина шины данных примененной ЭВМ. Таким образом в устройстве создается внутренняя шина данных двойной ширины в сравнении с шириной шины в ЭВМ.

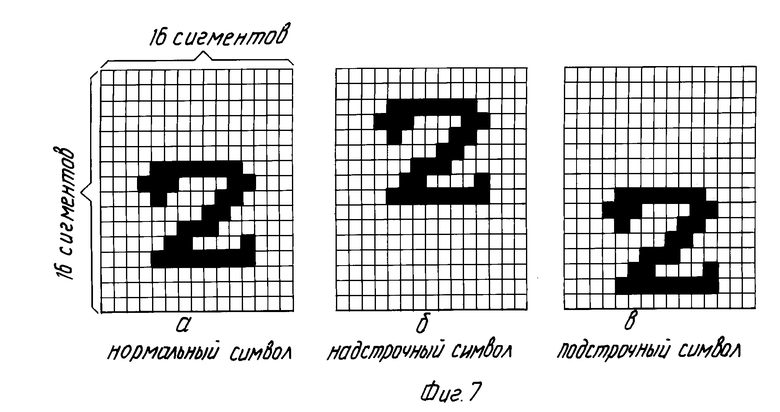

Сумматор 9 осуществляет перекодирование адреса строки растра символа с целью отображения подстрочных или надстрочных индексов. Это достигается путем присуммирования к коду номера строки растра константы "12", "2" или "0" в зависимости от атрибута символа: нормальный символ, надстрочный индекс, подстрочный индекс соответственно (см. фиг.7). В предлагаемом устройстве применен сумматор в схеме подключения операндов (фиг.4). Третий и четвертый входы операнда В объединены, первый вход заземлен. Таким образом, сумматор осуществляет формирование надстрочных индексов простым способом путем регенерации надстрочных и подстрочных индексов.

Формирователь 8 управляющих сигналов в сочетании с преобразователем 13 кода и управления от шины атрибутов символа создает возможность простыми средствами осуществлять буквенно-мозаичное отображение информации.

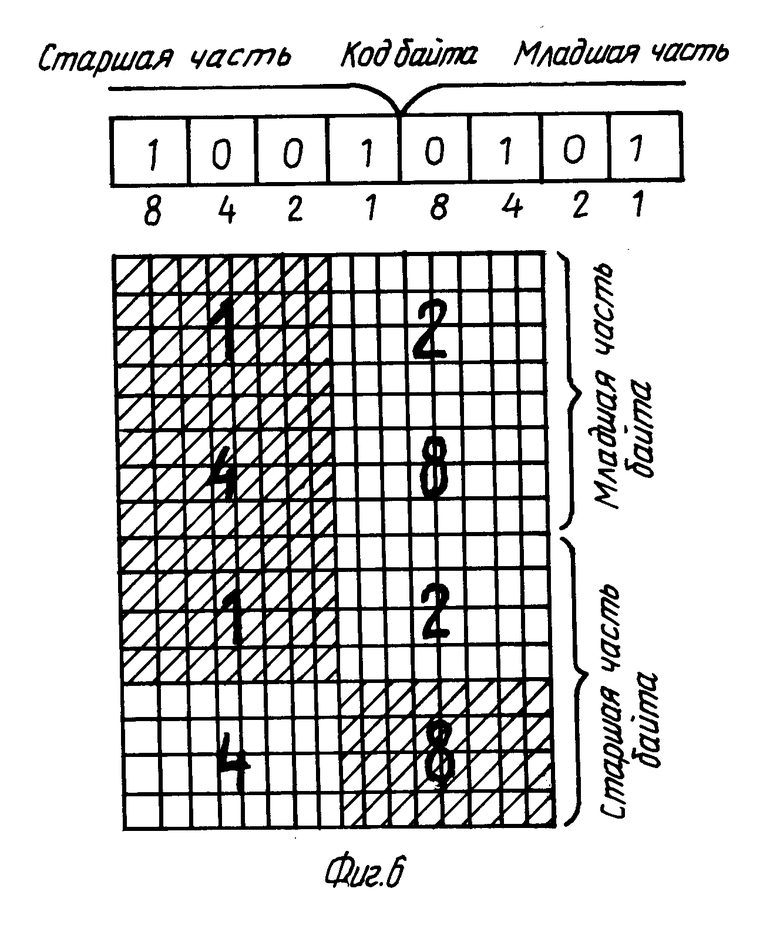

На фиг.5 изображено знакоместо, состоящее из 16х16 сегментов. Все сегменты сгруппированы в 8 секторов, каждый из которых, в случае присутствия признака буквенного кода (бит атрибута, например "8" бит): управляется соответствующим битом восьмибитного байта кода символа буквенно-мозаичным способом, как показано на фиг.6.

На фиг.7 изображено знакоместо, где а) нормальный символ, б) надстрочный символ и в) подстрочный символ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования изображения знаков на экране телевизионного индикатора | 1990 |

|

SU1827683A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1256084A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1982 |

|

SU1108486A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1984 |

|

SU1231533A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для отображения информации | 1986 |

|

SU1437852A1 |

| Устройство для сопряжения вычислительного комплекса накопителей на магнитной ленте | 1983 |

|

SU1142839A1 |

Использование: автоматика и вычислительная техника, системы отображения алфавитно-цифровой и буквенно-мозаичной информации. Сущность изобретения: устройство содержит генератор синхроимпульсов 1, счетчик адреса регенерации 2, коммутатор 3, буфер 12, блок управления 7, два блока элементов И 10, 11, блок оперативной памяти 4, сумматор 9, блок постоянной памяти 5, блок элементов ИЛИ 6, преобразователь кодов 13, блок кодирования 14. 13 ил.

УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ЗНАКОВ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА, содержащее генератор синхроимпульсов, выход которого подключен к счетному входу счетчика адреса регенерации, первый выход которого соединен с управляющим входом коммутатора, первый выход которого соединен с адресным входом блока оперативной памяти, первый выход-вход которого соединен с первым входом-выходом блока постоянной памяти и информационным входом буфера, управляющий вход которого подключен к первому выходу блока управления, второй выход которого подключен к управляющему входу блока оперативной памяти, второй выход коммутатора подключен к управляющему входу блока управления, синхровход которого соединен с вторым выходом счетчика адреса, информационный вход коммутатора соединен с шиной адреса устройства, шина управления которого соединена с информационным входом блока управления, и преобразователь кодов, отличающееся тем, что с целью расширения области применения устройства путем отображения подстрочных и надстрочных индексов и буквенно-мозаичной информации и повышения его быстродействия за счет увеличения скорости обмена путем использования независимого от фаз регенерационного цикла обмена, устройство содержит первый и второй блоки элементов И, элок элементов ИЛИ, сумматор, блок кодирования и формирователь управляющих сигналов, выход которого соединен с первым входом блока элементов ИЛИ, выход которого подключен к информационному входу преобразователя кодов, управляющий вход которого соединен с выходом генератора синхроимпульсов, а выход - с управляющим входом блока кодирования, выход которого является выходом устройства для подключения к видеовходу телевизионного индикатора, третий выход блока управления соединен с первыми управляющими входами первого и второго блоков элементов И, вторые управляющие входы которых подключены соответственно к четвертому и пятому выходам блока управления, информационный вход первого блока элементов И соединен с выходом буфера, вход-выход первого блока элементов И - с шиной данных устройства, первый выход-вход блока оперативной памяти - с входом-выходом первого блока элементов И, с первым входом-выходом второго блока элементов И, первым информационным входом-выходом формирователя управляющих сигналов и информационным входом сумматора, второй выход-вход блока оперативной памяти соединен с вторым входом-выходом второго блока элементов И, информационным входом сумматора, с вторым входом-выходом блока постоянной памяти, вторым информационным входом-выходом формирователя управляющих сигналов и информационным входом блока кодирования, третий выход счетчика адреса регенерации подключен к управляющим входам формирователя управляющих сигналов и сумматора, выход которого соединен с адресным входом блока постоянной памяти, выход которого соединен с вторым входом блока элементов ИЛИ.

| Современные методы и устройства отображения информации под ред | |||

| М.И.Кривошеева и А.Я.Брейтборта, М., Радио и связь, 1981, с.77-82. |

Авторы

Даты

1994-11-15—Публикация

1991-06-17—Подача