(54) ЦИФРОВОЙ КОРРЕЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯТОР | 1987 |

|

SU1834544A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Коррелятор | 1985 |

|

SU1309038A1 |

| КОРРЕЛЯТОР | 1972 |

|

SU424153A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Многоканальный цифровой коррелятор | 1985 |

|

SU1397938A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

| Коррелометр | 1988 |

|

SU1550532A1 |

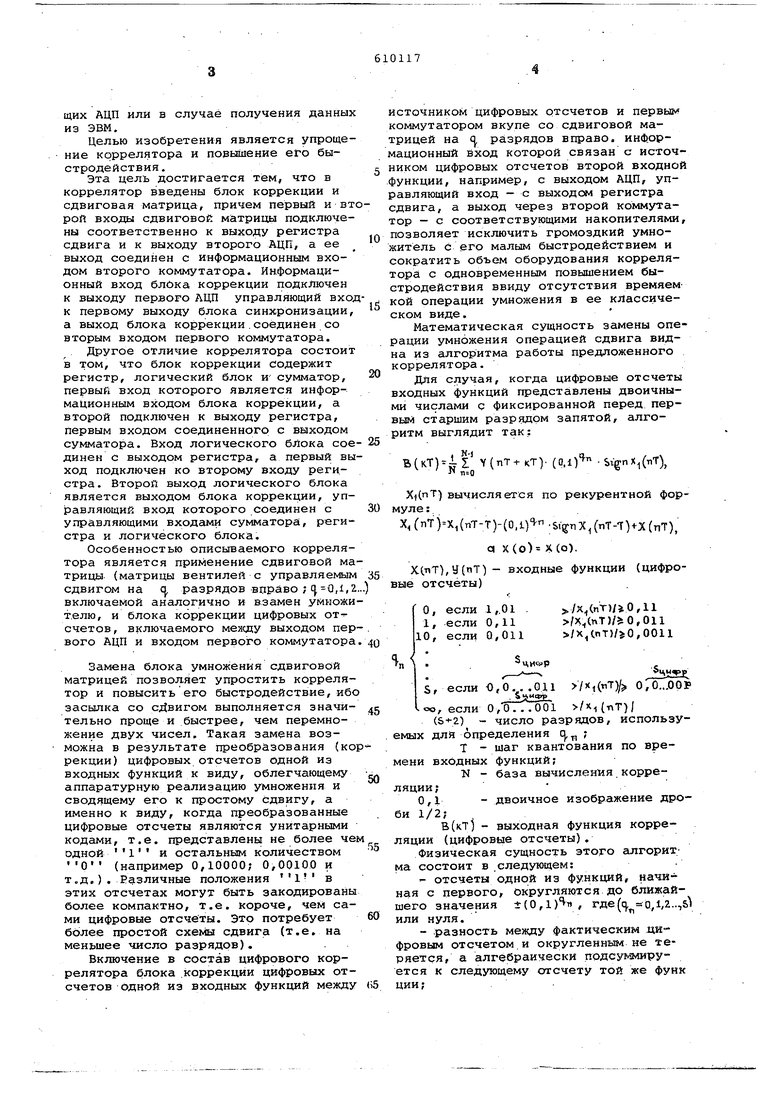

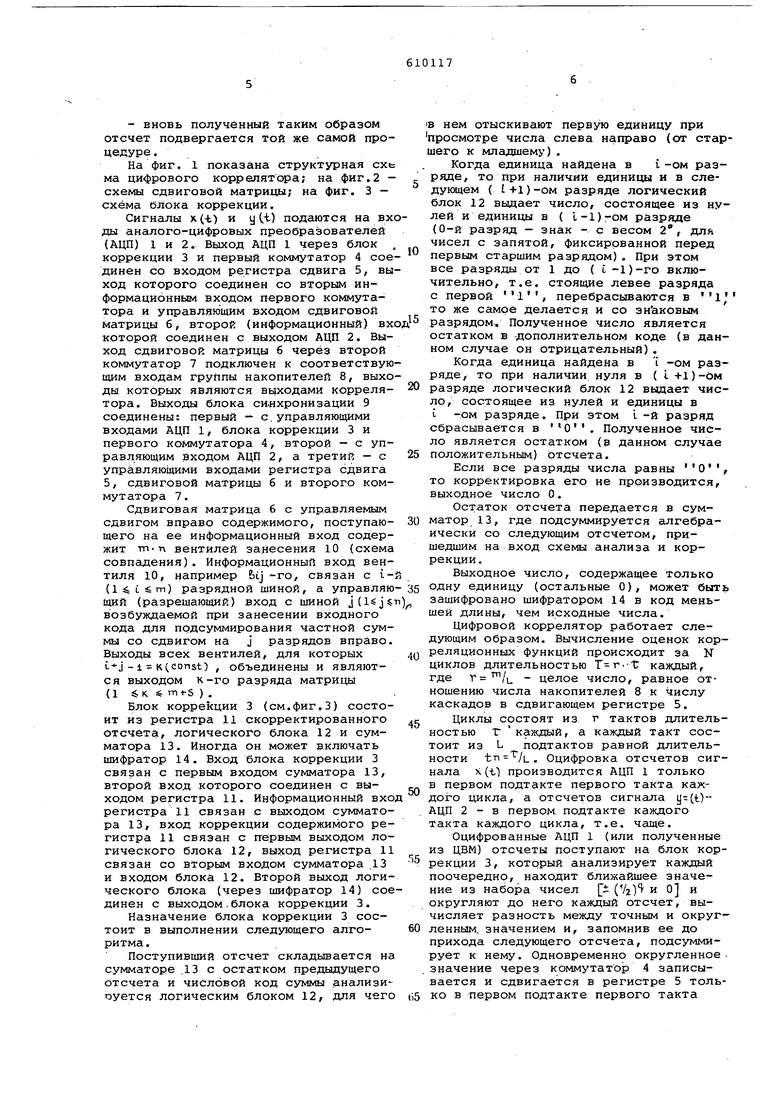

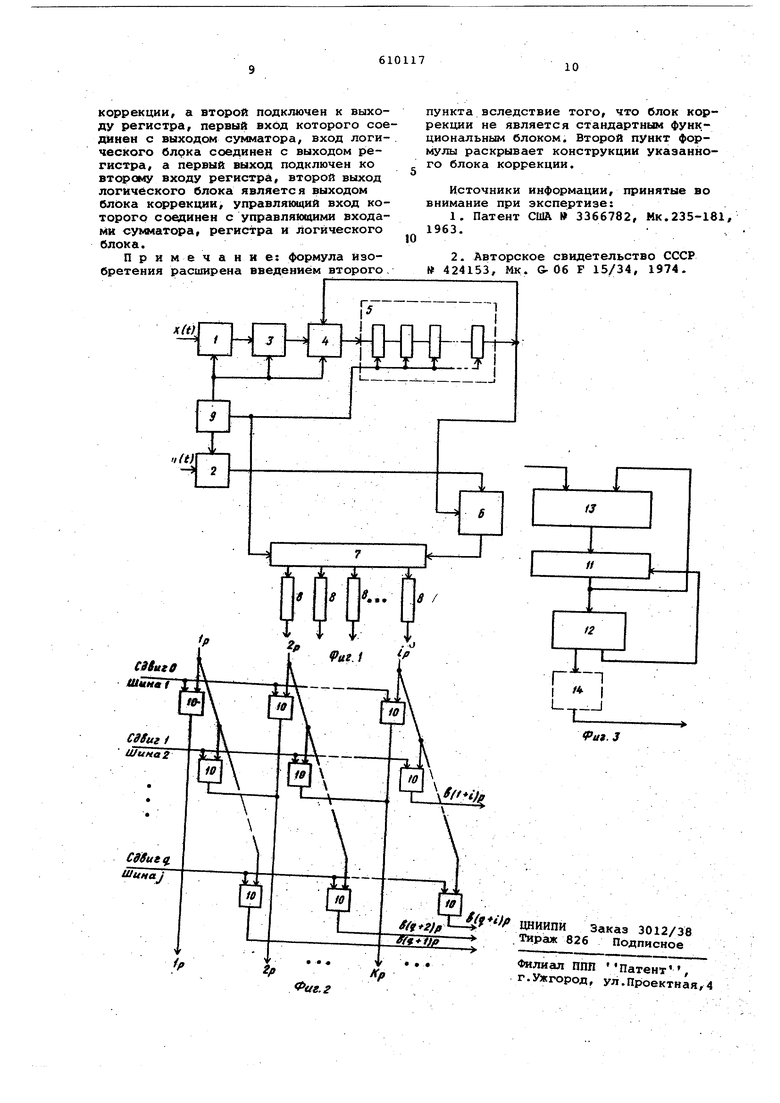

Изобретение относится к специализи рованным средствам вычислительной тех ники (как правило, работающим в двоичной системе счисления) и предназначено для нахождения оценок корреляционных функций при исследовании динамических процессов, Преимущественная область использования - цифровая обработка сигналов, особенно представленных в цифровой форме и хранящихся в оперативной памяти ЭВМ, хотя не исключена и аналоговая форма входных сигналов при обязательном использовании на входе быстродействующих аналого-цифровых преобразователей (АЦП). Известен цифровой коррелятор 1 , служащий для нахождения оценок корреляционных функций, в котором осуществляется запоминание и сдвиг определенного отрезка одной из входных функ ций, представленной многоразрядными двоичными отсчетами, на определенный интервал времени и умножение ее отсчётов fia многоразрядные двоичные отсчеты другой входной функции, поступающие в реальном масштабе времени, в той же последоватёльностй. ES таком корреляторе имеется .несколько множительных устройств, служащих для получения произведений типа у. , которые поступают в определенные ячейки памяти для подсуммирования и накопления текущих значений точек корреляционной функции. Известен цифровой коррелятор 2, содержащий первый и второй АЦП,информационные входы которых являются входами коррелятора; первый коммутатор, выход которого соединен с информационным входом регистра сдвига, выходом подключен ного к первому входу первого коммутатора второй коммутатор, выходы которого соединены со входами соответствующих накопителей, и блок синхронизации. Первый выход блока синхронизации подключен к управляющим входам первого АЦП и первого коммутатора, второй выход блока синхронизации соединен с управляющими входами регистра сдвига и второго коммутатора, а третий выход блока синхронизации подключен к управляющему входу второго АЦП. Недостаток этого коррелятора состоит в том, что он содержит .сложные и медленно действующие множительные устройства. Это усложняет цифровой коррелятор, особенно, если он многоканальный, ограничивает его быстродействие , особенно при быстродействующих АЦП ИЛИ в случае получения данны из ЭВМ. Целью изобретения является упроще ние коррелятора и позышение его быстродействия. Эта цель достигается тем, что в коррелятор введены блок коррекции и сдвиговая матрица, причем первый и в рой входы сдвиговой матрицы подключе ны соответственно к выходу регистра сдвига и к выходу второго АЦП, а ее выход соединен с информационным входом второго коммутатора. Информационный вход блика коррекции подключен к выходу первого АЦП управляющий вхо к первому выходу блока синхронизации а выход блока коррекции.соединен со вторым входом первого коммутатора. Другое отличие коррелятора состои в том, что блок коррекции содержит регистр, логический блок и сумматор, первый вход которого является информационным входом блока коррекции, а второй подключен к выходу регистра. Первым входом соединенного с выходом сумматора. Вход логического блока сое динен с выходом регистра, а первый вы ход подключен ко второму входу регистра. Второй выход логического блока является выходом блока коррекции, управляющий вход которого соединен с управляющими входами сумматора, регистра и логического блока. Особенностью описываемого коррелятора является применение сдвиговой ма трицы (матрицы вентилей с управляемым сдвигом на CJ, разрядов вправо ; cj 0,1, включаемой аналогично и взамен умножи т.елю, и блока коррекции цифровых от счетов, включаемого мелоду выходом пер вого АЦП и входом первого коммутатора Замена блока умножения сдвиговой матрицей позволяет упростить коррелятор и повысить его быстродействие, иб засылка со сДвигом выполняется значительно проще и быстрее, чем перемножение двух чисел. Такая замена возможна в результате преобразования (ко рекции) цифровых отсчетов одной из входных функций к виду, облегчающему аппаратурную реализацию умножения и сводящему его к простому сдвигу, а именно к виду, когда преобразованные цифровые отсчеты являются унитарными кодами, т.е. представлены не более че одной 1 и остальным количеством О (например 0,10000; 0,00100 и т.д.), Различные положения Ч в этих отсчетах могут быть закодированы более компактно, т.е. короче, чем сами цифровые отсчеты. Это потребует более простой схемы сдвига (т.е. на меньшее число разрядов). Включение в состав цифрового коррелятора блока .коррекции цифровых отсчетов одной из входных функций между источником цифровых отсчетов и первым коммутатором вкупе со сдвиговой матрицей на CJ, разрядов вправо, информационный вход которой связан с источником цифровых отсчетов второй входной функции, например, с выходом АЦП, управляющий вход - с выходом регистра сдвига, а выход через второй коммутатор-с соответствующими накопителями, позволяет исключить громоздкий умножитель с его малым быстродействием и сократить объем оборудования коррелятора с одновременным повышением быстродействия ввиду отсутствия времяемкой операции умножения в ее классическом виде. Математическая сущность замены операции умножения операцией сдвига видна из алгоритма работы предложенного коррелятора. Для случая, когда цифровые отсчеты входных функций представлены двоичными числами с фиксированной перед первым старшим разрядом запятой, алгоритм выглядит так: В(кТ)-11 У(). (0,1)4- SignX(TiT), Xi() вычисляется по рекурентной формуле : X(nT)Xi(nT-T)-(0,l).-gTiX(nT-T)tX(nT), а х(о) 1(о). Х(.т1Т),У(пТ) - входные функции (цифровые отсчёты) /x(nT)/iO,ll 0,если 1,.01 . /х(пТ),ОЦ 1,если 0,11 /х/пТ)/50,0011 10, если 0,011 -- - -чуццуу S, если 0,0.. .ОД1 (nT)/ 0,0...001 ...iA;i22 00, если 0,0...001 (tiT)| (S+2) - число разрядов, используемых для определения cj, ; Т - шаг квантования по времени входных функций; N - база вычисления.корреляции;0,1 - двоичное изображение дроби 1/2; В(кТ) - выходная функция корреляции (цифровые отсчеты). Физическая сущность этого алгорит; ма состоит в .следующем: отсчеты одной из Функций, начиная с первого, округляются до ближайшего значения ±(0,1)11, где(с),о,1,г..,5 или нуля. - разность между фактическим цифровым отсчетом.и округленным не теряется, а алгебраически подсуммируется к следующему отсчету той же функ ции; - вновь полученный таким образом отсчет подвергается той же самой процедуре. На фиг. 1 показана структурная cxt ма ци4 рового коррелятора; на фиг,2 - схемы сдвиговой матрицы; на фиг. 3 схема блока коррекции. Сигналы x(-t) и у (.t) подаются на вх ды аналого-цифровых преобразователей (АЦП) 1 и 2. Выход АЦП 1 через блок коррекции 3 и первый коммутатор 4 сое динен со входом регистра сдвига 5, вы ход которого соединен со вторым информационным входом первого коммутатора и управляющим входом сдвиговой матрицы б, второй (информационный) вх которой соединен с выходом АЦП 2. Выход сдвиговой матрицы б через второй коммутатор 7 подключен к соответствую щим входам группы накопителей 8, выхо ды которых являются выходами коррелятора. Выходы блока си-нхронизации 9 соединены: первый - с.управляющими входами АЦП 1, блока коррекции 3 и первого коммутатора 4, второй - с управляющим входом АЦП 2, а третий - с управляющими входами регистра сдвига 5, сдвиговой матрицы б и второго коммутатора 7. Сдвиговая матрица 6 с управляемым сдвигом вправо содержимого, поступающего на ее информационный вход содержит тп-п вентилей занесения 10 (схема совпадения). Информационный вход вентиля 10, например bij -го, связан с i(1 4 L йтп) разрядной шиной, а управляю щий (разрешающий) вход с шиной j( возбуждаемой при занесении входного кода для подсуммирования частной суммы со сдвигом на j разрядов вправо. Выходы всех вентилей, для которых - 1 KCconst) , объединены и являются выходом к-го разряда матрицы (1 к тп+-5 ) . Блок коррекции 3 (см.фиг.З) состоит из регистра 11 скорректированного отсчета, логического блока 12 и сумматора 13. Иногда он может включать шифратор 14. Вход блока коррекции 3 связан с первым входом сумматора 13, второй вход которого соединен с выходом регистра 11. Информационный вхо регистра 11 связан с выходом сумматора 13, вход коррекции содержимого регистра 11 связан с первым выходом логического блока 12, выход регистра 11 связан со вторым входом сумматора .13 и входом блока 12. Второй выход логического блока (через шифратор 14) сое динен с выходом-блока коррекции 3. Назначение блока коррекции 3 состоит в выполнении следующего алгоритма. Поступивший отсчет складывается на сумматоре .13 с остатком предыдущего отсчета и числовой код суммы .анализиоуется логическим блоком 12/ для чего В нем отыскивают первую единицу при просмотре числа слева направо (от старшего к младшему). Когда единица найдена в i-ом разряде, то при наличии единицы и в следующем ( i+l)-oM разряде логический блок 12 выдает число, состоящее из нулей и единицы в ( 1-1)-ом разряде (0-й разряд - знак - с весом 2, длл чисел с запятой, фиксированной перед первым старшим разрядом). При этом все разряды от 1 до ( i-l)-ro включительно, т.е. стоящие левее разряда с первой , перебрасываются в i то же самое делается и со знаковым разрядом. Полученное число является остатком в -дополнительном коде (в данном случае он отрицательный). Когда единица найдена в i -ом разряде, то при наличии нуля в ( I +1)-6м разряде логический блок 12 выдает число, состоящее из нулей и единицы в L -ом разряде. При зтом I -и разряд сбрасывается в О. Полученное число является остатком (в данном случае положительным) отсчета. Если все разряды числа равны О, то корректировка его не производится, выходное число О. Остаток отсчета передается в сумматор 13, где подсуммируется алгебраически со следующим отсчетом, пришедшим на вход схемы анализа и коррекции. Выходное число, содержащее только одну единицу (остальные 0), может быть зашифровано шифратором 14 в код меньшей длины, чем исходные числа. Цифровой коррелятор работает следующим образом. Вычисление оценок корреляционных функций происходит за N циклов длительностью .-т; каждый, где . - целое число, равное отношению числа накопителей 8 к числу каскадов в сдвигающем регистре 5. Циклы состоят из г тактов длительностью Т каждый, а каждый такт состоит из Ь подтактов равной длительности . Оцифровка отсчетов сигнала X (t1 производится АЦП 1 только в первом подтакте первого такта каждого цикла, а отсчетов сигнала y-(t)АЦП 2 - в первом, подтакте каждого такта каждого цикла, т.е. чаще. Оцифрованные АЦП 1 (или полученные из ЦВМ) отсчеты поступают на блок коррекции 3, который анализирует каждый поочередно, находит ближайшее значение из набора чисел i ( и 0 и округляют до него каждый отсчет, вычисляет разность между точным и округленным, значением и, запомнив ее до прихода следующего отсчета, подсуммирует к нему. Одновременно округленное . значение через ког мутатор 4 записывается и сдвигается в регистре 5 только в первом подтакте первого такта

каждого цикла. В любом другом подтакте любого такта и цикла замыкается цепь рециркуляции с выхода регистра сдвига 5 на его вход через первый коммутатора 4, и регистр сдвига 5 работает как кольцевой. Таким образом, в каждом I -ом подтакте { Е 1,2.,.,L ) j -го такта ( j 1, 2, ..., г ) 1 -го цикла (i 1,2,..., N ) с выхода регистра сдвига 5 на управляющий вход матрицы вентилей занесения подается отсчет

i(T), где пТ irr (L- е )гГ.

На другой, информационный вход сдвиговой матрицы 6 в течение всего такта j подается один и тот же отсчет Y 1г,т-г-кТ), гдe(nтtкт)f()r .

К выходу матрицы б в кахсдом t -ом подтакте j-го такта через второй коммутатор 7 подключен(Ь-1)г- j -и. накопитель 8f в котором после N циклов усреднения получается оценка корреляционной функции В(.кт), где KT(L-t)r-t-j-ljt поскольку временной сдвиг меиоду отсчетами, поступающими на разные входы матрицы б в f-ом подтакте j -го такта, будет равен (L-t)- -j-11Т.

В зависимости от типа АЦП функции блока коррекции может выполнять этот же АЦП, отличающийся от обычного выходной характеристикой. Определяемой алгоритмом получения числа „ при поступлении на вход величины х (t).

С целью сокращения емкости регистра сдвига 5 полученные на выходе схемы анализа и коррекции числа (одна единица при остальных нулях) могут быть зашифрованы более коротким кодом. В этом случае на выходе регистра сдвига должен быть дешифратор, который можно считать составной частью сдвиговой матрицы 6. Шифратор и дешифратор могут уменьшить в два раза и более емкость (в дв.битах) регистра сдвига 5.

Особенно значительные технические затруднения при создании цифровых корреляторов вызьшает реализация операции умножения. Используемые для этого блоки умножения громоздки и неоперативны. Последнее обстоятельство особенно существенно, если учесть, чго половина арифметических операций, выполняемых в цифровом корреляторе операции умножения.

Использование вместо множительного устройства менее емкой по объему оборудова:ния и имёклцей вследствие этого малое время выполнения операции сдвиговой матрицы с управляемым сдвигом на заданное число разрядов вправо позволяет значительно сократить количе ство элементов, потребное для создания коррелятора, и существенно ускорить выполн-рчие операции, что/ в свою очередь, позволяет обрабатывать высоко скоростные сигналы (в случае работы

с АЦП) или значительно сократить время обработки (для корреляторов, сочлененных с ЦВМ и (или) получающих от них цифровые отсчеты). В первом случае это позволит создать более простые по конструкции и дешевые по себестоимости корреляторы, обладающие широким частотным диапазоном входных сигналов при использовании одной и той же элементной базы (например, интегральных микросхем), что и прототипы.

Во втором случае оснащение ЦВМ, выполняющих большой объем работ по корреляционному анализу, по цифровой

фильтрации реальных физических сигналов, преобразованных в цифровую форму и записанных в памяти ЦВМ (например, сейсмических, гидроакустических, электрических) , позволяет сократить машинное время этих машин ввиду более ускоренного выполнения этих операций на цифровом корреляторе.

Формула изобретения 1. Цифровой коррелятор, содержащий

первый и второй аналого-цифровые преобразователи, информационные входы которых являются входами коррелятора, первый коммутатор, выход которого сое.динен с информационным входом регистра сдвига, выход которого подключен к первому входу первого коммутатора, второй коммутатор, выходы которого соединены со входами соответствующих накопителей, и блок синхронизации,

первый выход которого подключен к управляющим входам первого аналого-цифрового преобразователя и первого коммутатора, второй выход блока синхронизации соединен с управляющими- входами регистра сдвига и второго коммутатора, а третий выход блока синхронизации подключен к управляющему входу второго аналого-цифрового преобразователя, отличающийся

с: целью повышения быстродействия цифрового коррелятора и повышения его точности, в него введены блок коррекции и сдвиговая матрица, причем первый и второй входы сдвиговой матрицы подключены соответственно к выходу регистра сдвига и к выходу второго аналого-цифрового преобразователя, а ее выход соединен с информационным входом второго коммутатора,

информационный вход блока коррекции

подключен к выходу первого аналогоцифрового преобразователя, управляющий вход - к первому выходу блока синхронизации, а выход блока коррекции соединен со вторым входом первого коммутатора.

Авторы

Даты

1978-06-05—Публикация

1976-04-05—Подача