Изобретение относится к вычислительной технике и предназначено для использования в распределенных микро- процессорныЯ системах цифровой обработки речевых и акустических сигналов .

Цель изобретения - сокращение аппаратурных затрат.

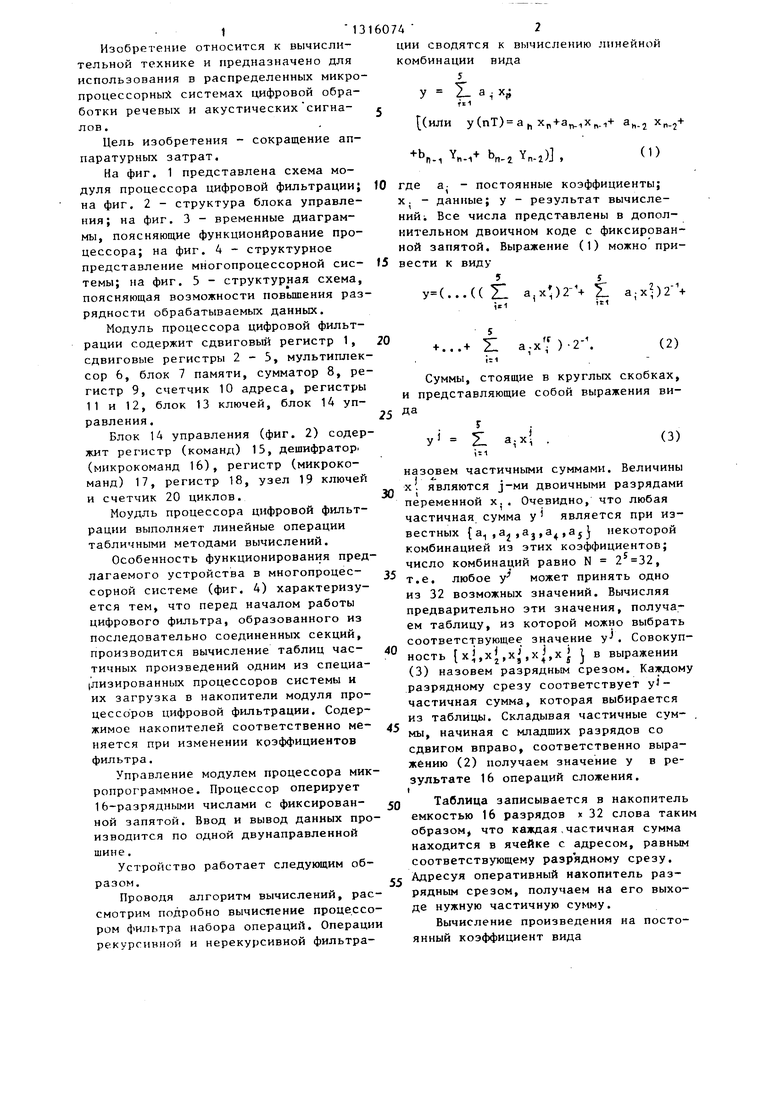

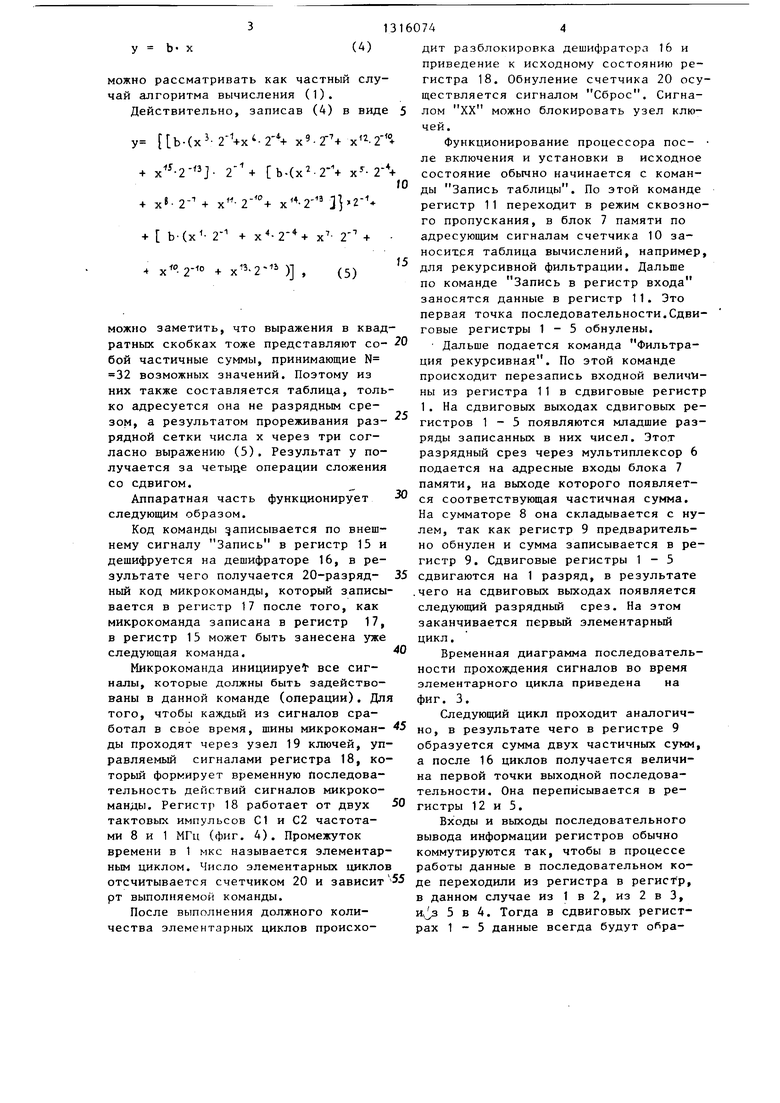

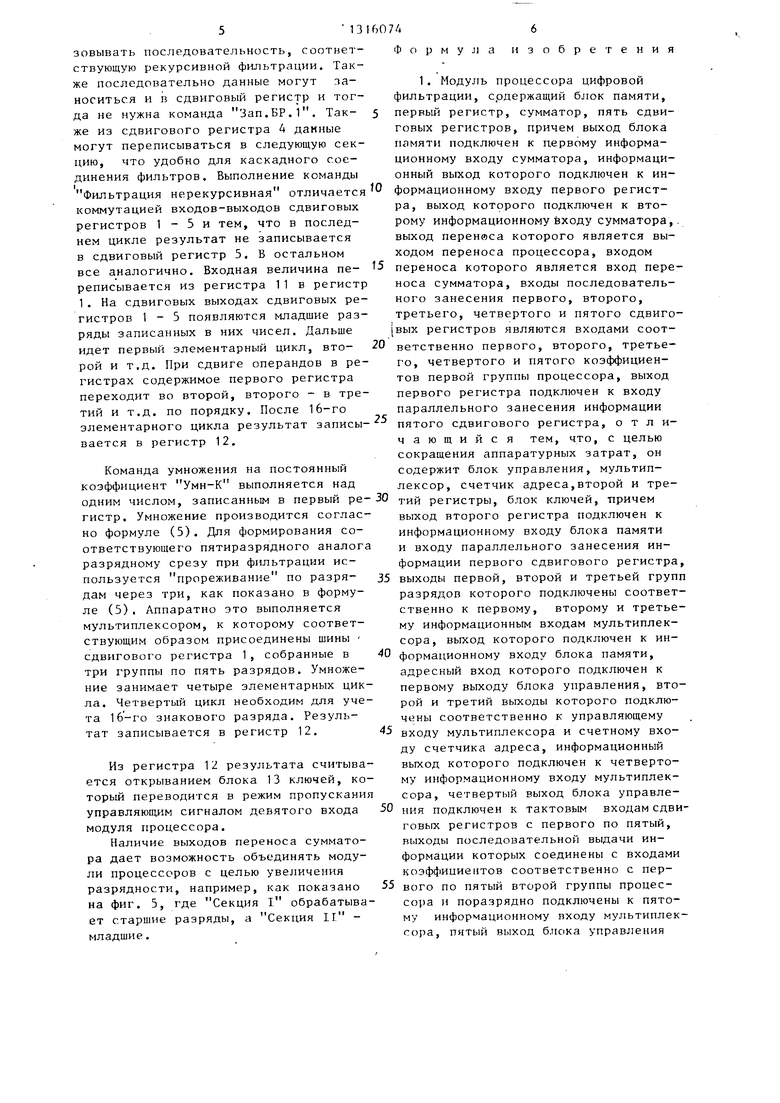

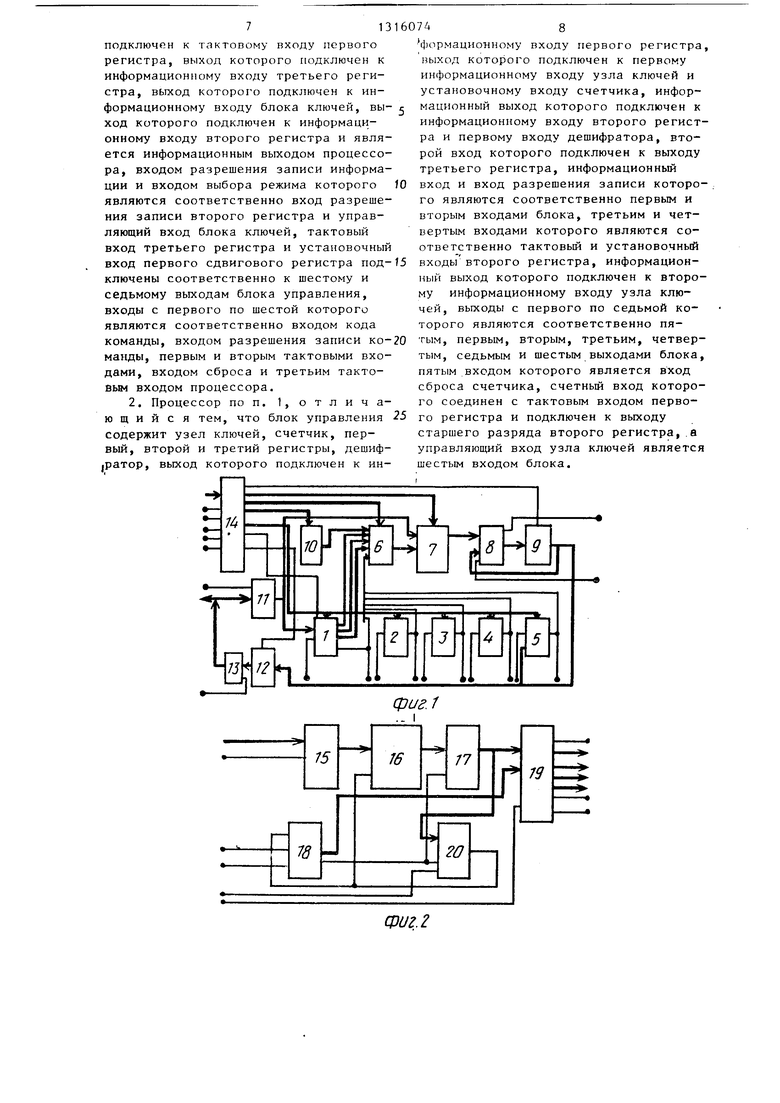

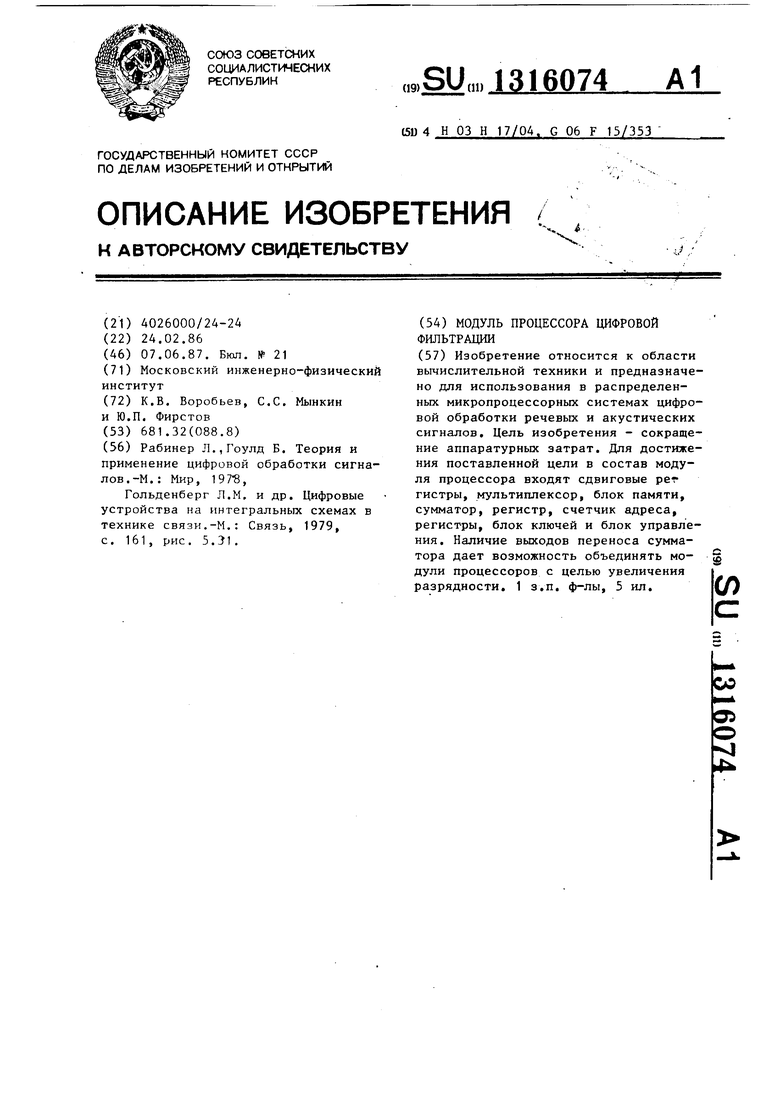

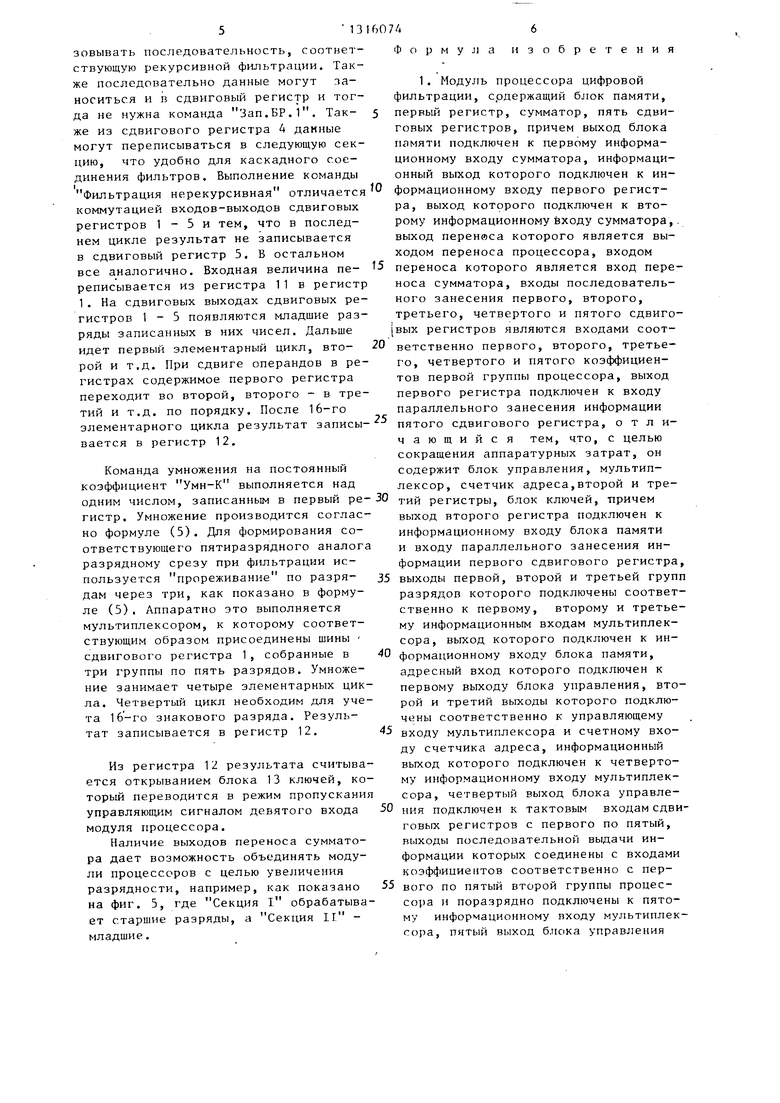

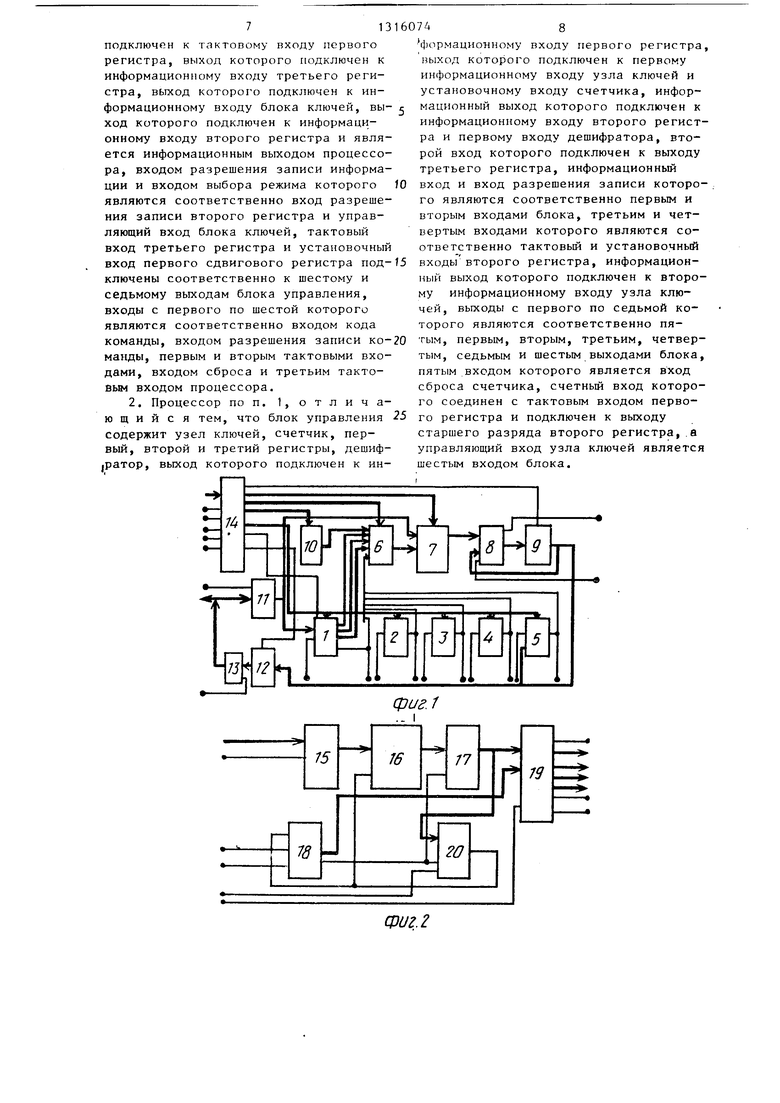

На фиг. 1 представлена схема модуля процессора цифровой фильтрации; 10 где а- - постоянные коэффициенты; на фиг. 2 - структура блока управления; на фиг. 3 - временные диаграммы, поясняющие функционирование процессора; на фиг. 4 - структурное

ции сводятся к вычислению линейной комбинации вида

5

У II а . х

T l

(или у(пТ),х,.,+ a,.,j х +Ч., Y,.,- b,., Y,.i)J, (1)

X; - данные; у - результат вычисле ний i Все числа предст-авлены в допо нительном двоичном коде с фиксиров ной запятой. Выражение (1) можно п

у(...(( Ц а,х)2-% JL a;X)2

S + ...+ 2: а.х- )-2- (

ill

Суммы, стоящие в круглых скобках и представляющие собой выражения в

представление многопроцессорной сие- 15 вести к виду темы; на фиг. 5 - структурная схема,5у

поясняющая возможности повышения разрядности обрабатываемых данных.

Модуль процессора цифровой фильтрации содержит сдвиговый регистр 1, 20 сдвиговые регистры 2-5, мультиплексор 6, блок 7 памяти, сумматор 8, регистр 9, счетчик 10 адреса, регистры

11 и 12, блок 13 ключей, блок 14 па равления.

Блок 14 управления (фиг. 2) содержит регистр (команд) 15, дешифратор, (микрокоманд 16), регистр (микрокоманд) 17, регистр 18, узел 19 ключей и счетчик 20 циклов.

Моудль процессора цифровой фильтрации выполняет линейные операции табличными методами вычислений.

Особенность функционирования предлагаемого устройства в многопроцес- ,г -- - --,

/. ,4 - т.е. любое у- может принять одно

.-inur u г чгт-ошю («tiur Л) vanavTCinu4v-j- t- f

ИЗ 32 ВОЗМОЖНЫХ значений. Вычисляя

J

Z

41

а.х

назовем частичными суммами. Величин

j - у. X. являются j-ми двоичными разряда

переменной х.. Очевидно, что любая частичная сумма у является при и вестных {а ,а2,aj,а,аJJ некоторо комбинацией из этих коэффициентов;

число комбинаций равно N

)5 32,

сорной системе (фиг. 4) характеризу ется тем, что перед началом работы цифрового фильтра, образованного из последовательно соединенных секций, производится вычисление таблиц частичных произведений одним из специа- (лизированных процессоров системы и их загрузка в накопители модуля процессоров цифровой фильтрации. Содержимое накопителей соответственно меняется при изменении коэффициентов фильтра.

Управление модулем процессора мик40

45

предварительно эти значения, получ ем таблицу, из которой можно выбра соответствующее значение yJ. Совоку ность х,х,х,х,хI I в выражении (3) назовем разрядным срезом. Каждо разрядному срезу соответствует у1- частичная сумма, которая выбирается из таблицы. Складывая частичные сум мы, начиная с младших разрядов со сдвигом вправо, соответственно выра жению (2) получаем значение у в ре зультате 16 операций сложения.

предварительно эти значения, получаем таблицу, из которой можно выбрать соответствующее значение yJ. Совокупность х,х,х,х,хI I в выражении (3) назовем разрядным срезом. Каждому разрядному срезу соответствует у1- частичная сумма, которая выбирается из таблицы. Складывая частичные сум- . мы, начиная с младших разрядов со сдвигом вправо, соответственно выражению (2) получаем значение у в результате 16 операций сложения.

ропрограммное. Процессор оперирует, 16 разрядными числами с фиксирован- Q Таблица записывается в накопитель

ной запятой. Ввод и вывод данных про-емкостью 16 разрядов х 32 слова таким

изводится по одной двунаправленнойобразом, что каждая .частичная сумма

шине.находится в ячейке с адресом, равным

Устройство работает следующим об-соответствующему разрядному срезу,

разом.55Адресуя оперативный накопитель разПроводя алгоритм вычислений, рас-рядным срезом, получаем на его выхосмотрим подробно вычисление процессо-де нужную частичную сумму, ром 4 ильтра набора операций. Операции Вычисление произведения на посторекурсивной и нерекурсивной фильтра-янный коэффициент вида

где а- - постоянные коэффициенты;

ции сводятся к вычислению линейной комбинации вида

5

У II а . х

T l

(или у(пТ),х,.,+ a,.,j х. +Ч., Y,.,- b,., Y,.i)J, (1)

где а- - постоянные коэффициенты;

X; - данные; у - результат вычислений i Все числа предст-авлены в дополнительном двоичном коде с фиксированной запятой. Выражение (1) можно приу(...(( Ц а,х)2-% JL a;X)2-V

S + ...+ 2: а.х- )-2- (2)

ill

Суммы, стоящие в круглых скобках, и представляющие собой выражения виести к виду 5у

Z

41

а.х

(3)

-- - --,

назовем частичными суммами. Величины

j - X. являются j-ми двоичными разрядами

переменной х.. Очевидно, что любая частичная сумма у является при известных {а ,а2,aj,а,аJJ некоторой комбинацией из этих коэффициентов;

число комбинаций равно N

)5 32,

предварительно эти значения, получаем таблицу, из которой можно выбрать соответствующее значение yJ. Совокупность х,х,х,х,хI I в выражении (3) назовем разрядным срезом. Каждому разрядному срезу соответствует у1- частичная сумма, которая выбирается из таблицы. Складывая частичные сум- . мы, начиная с младших разрядов со сдвигом вправо, соответственно выражению (2) получаем значение у в результате 16 операций сложения.

Таблица записывается в накопитель

у bможно рассматривать как частный случай алгоритма вычисления (1).

Действительно, записав (4) в виде 5

Ь-(х

2-Vx

с.

:5-Г + х .2

п. о-ь . 2-4 b.(x.2-V 4 хв-2- + Я 2+ Ь-( 2- +

+ X

13. 9 --ч

)

(5)

можно заметить, что выражения в квадратных скобках тоже представляют со- 20 бой частичные суммы, принимающие N 32 возможных значений. Поэтому из них также составляется таблица, только адресуется она не разрядным сре25

зом, а результатом прореживания разрядной сетки числа х через три согласно выражению (5). Результат у получается за четыде операции сложения со сдвигом.

Аппаратная часть функционирует следующим образом.

Код команды записывается по внешнему сигналу Запись в регистр 15 и дешифруется на дешифраторе 16, в ре Дальше подается команда Фильтрация рекурсивная. По этой команде происходит перезапись входной величины из регистра 11 в сдвиговые регистр 1. На сдвиговых выходах сдвиговых регистров 1 - 5 появляются младшие разряды записанных в них чисел. Этот разрядный срез через мультиплексор 6 подается на адресные входы блока 7

30

памяти, на выходе которого появляется соответствующая частичная сумма. На сумматоре 8 она складывается с нулем, так как регистр 9 предварительно обнулен и сумма записывается в регистр 9. Сдвиговые регистры 1 - 5 зультате чего получается 20-разряд- 35 сдвигаются на 1 разряд, в результате ньй код микрокоманды, который записы- .чего на сдвиговых выходах появляется

следующий разрядный срез. На этом заканчивается первый элементарный цикл.

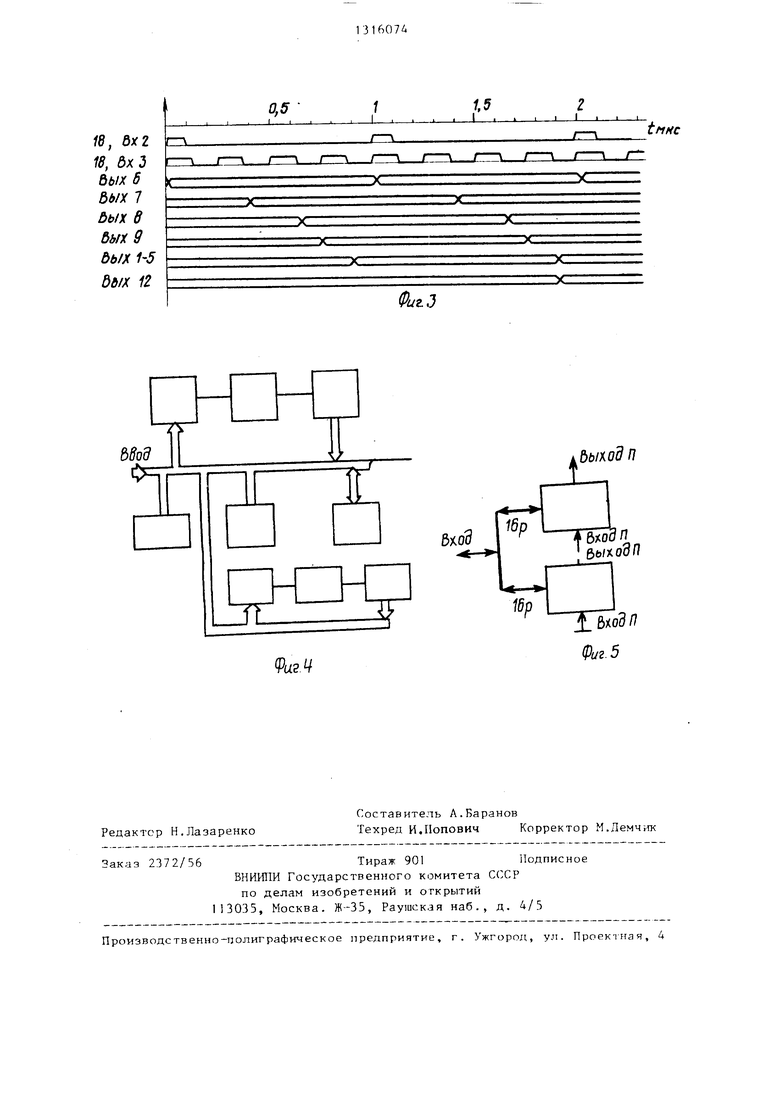

Временная диаграмма последовательности прохождения сигналов во время элементарного цикла приведена на фиг. 3.

Следующий цикл проходит аналогичвается в регистр 17 после того, как микрокоманда записана в регистр 17, в регистр 15 может быть занесена уже следующая команда.

Микрокоманда инициирует все сигналы, которые должны быть задействованы в данной команде (операции). Для того, чтобы каждый из сигналов сработал в свое время, шины микрокоман- 45 о, в результате чего в регистре 9 ды проходят через узел 19 ключей, уп- образуется сумма двух частичных сумм, равляемый сигналами регистра 18, ко- а после 16 циклов получается величи- торый формирует временную Последова- на первой точки выходной последовательность действий сигналов микрокоманды. Регистр 18 работает от двух 50 тактовых импульсов С1 и С2 частотами 8 и 1 МГц (фиг. 4). Промежуток времени в 1 мкс называется элементарным циклом. Число элементарных циклов

отсчитывается счетчиком 20 и зависит 55 де переходили из регистра в регист р, рт выполняемой команды.в данном случае из1в2, из2вЗ,

После выполнения должного коли- и, 5 в 4. Тогда в сдвиговых регист- чества элементарных циклов происхо- pax 1-5 данные всегда будут обрательности. Она переписывается в регистры 12 и 5.

Входы и выходы последовательного вывода информации регистров обычно коммутируются так, чтобы в процессе работы данные в последовательном ко

5

Ю

20

3160744

дит разблокировка дешифратора 16 и приведение к исходному состоянию регистра 18. Обнуление счетчика 20 осуществляется сигналом Сброс. Сигналом XX можно блокировать узел ключей.

Функционирование процессора пос- ле включения и установки в исходное состояние обычно начинается с команды Запись таблицы. По этой команде регистр 11 переходит в режим сквозного пропускания, в блок 7 памяти по адресующим сигналам счетчика 10 заносится таблица вычислений, например, для рекурсивной фильтрации. Дальше по команде Запись в регистр входа заносятся данные в регистр 11. Это первая точка последовательности.Сдвиговые регистры 1 - 5 обнулены.

Дальше подается команда Фильтрация рекурсивная. По этой команде происходит перезапись входной величины из регистра 11 в сдвиговые регистр 1. На сдвиговых выходах сдвиговых регистров 1 - 5 появляются младшие разряды записанных в них чисел. Этот разрядный срез через мультиплексор 6 подается на адресные входы блока 7

15

25

30

35

следующий разрядный срез. На этом заканчивается первый элементарный цикл.

Временная диаграмма последовательности прохождения сигналов во время элементарного цикла приведена на фиг. 3.

Следующий цикл проходит аналогич о, в результате чего в регистре 9 образуется сумма двух частичных сумм, а после 16 циклов получается величи- на первой точки выходной последова о, в результате чего в регистре 9 образуется сумма двух частичных сумм а после 16 циклов получается величи- на первой точки выходной последоваде переходили из регистра в регист р, в данном случае из1в2, из2вЗ,

тельности. Она переписывается в регистры 12 и 5.

Входы и выходы последовательного вывода информации регистров обычно коммутируются так, чтобы в процессе работы данные в последовательном козовывать последовательность, соответствующую рекурсивной фильтрации. Также последовательно данные могут заноситься и в сдвиговый регистр и тогда не нужна команда Зап.БР.1. Так- же из сдвигового регистра А данные могут переписываться в следующую секцию, что удобно для каскадного соединения фильтров. Выполнение команды Фильтрация нерекурсивная отличается коммутацией входов-выходов сдвиговых регистров 1 - 5 и тем, что в последнем цикле результат не записывается в сдвиговый регистр 5. В остальном все аналогично. Входная величина переписывается из регистра 11 в регистр 1. На сдвиговых выходах сдвиговых регистров 1 - 5 появляются младшие разряды записанных в них чисел. Дальше идет первый элементарный цикл, вто- рой и т.д. При сдвиге операндов в регистрах содержимое первого регистра переходит во второй, второго - в третий и т.д. по порядку. После 16-го элементарного цикла результат записы вается в регистр 12.

.,Команда умножения на постоянный коэффициент Умн-К выполняется над

одним числом, записанным в первый ре-30 ий регистры, блок ключей, причем гистр. Умножение производится соглас- выход второго регистра подключен к

1. Модуль процессора цифровой фильтрации, срдержащий блок памяти первый регистр, сумматор, пять сдв говых регистров, причем выход блок памяти подключен к первому информа ционному входу сумматора, информац онный выход которого подключен к и формационному входу первого регист ра, выход которого подключен к вто рому информационному бходу сумматора выход переняса которого является вы ходом переноса процессора, входом переноса которого является вход пер носа сумматора, входы последователь ного занесения первого, второго, третьего, четвертого и пятого сдви вых регистров являются входами соо ветственно первого, второго, треть го, четвертого и пятого коэффициен тов первой группы процессора, выход первого регистра подключен к входу параллельного занесения информации пятого сдвигового регистра, отл чающийся тем, что, с целью сокращения аппаратурных затрат, он содержит блок управления, мультиплексор, счетчик адреса,второй и тр

но формуле (5). Для формирования соответствующего пятиразрядного аналога разрядному срезу при фильтрации используется прореживание по разрядам через три, как показано в формуле (5). Аппаратно это выполняется мультиплексором, к которому соответствующим образом присоединены шины - сдвигового регистра 1, собранные в три группы по пять разрядов. Умножение занимает четыре элементарных цикла. Четвертый цикл необходим для учета 16-го знакового разряда. Результат записывается в регистр 12.

Из регистра 12 результата считывается открыванием блока 13 ключей, который переводится в режим пропускания управляющим сигналом девятого входа модуля процессора.

Наличие выходов переноса сумматора дает возможность объединять модули процессоров с целью увеличения разрядности, например, как показано на фиг. 5, где Секция 1 обрабатывает старшие разряды, а Секция II - младщие.

информационному входу блока памяти и входу параллельного занесения ин формации первого сдвигового регист

35 выходы первой, второй и третьей гр разрядов которого подключены соотв ственно к первому, второму и трет му информационным входам мультипле сора, выход которого подключен к и

формационному входу блока памяти, адресный вход которого подключен к первому выходу блока управления, вт рой и третий выходы которого подклю чены соответственно к управляющему входу мультиплексора и счетному вхо ду счетчика адреса, информационный выход которого подключен к четверто му информационному входу мультиплек сора, четвертый выход блока управле ния подключен к тактовым входам сд говых регистров с первого по пятый выходы последовательной выдачи информации которых соединены с входам коэффициентов соответственно с первого по пятый второй группы процес сора и поразрядно подключены к пято му информационному пходу мультипле сора, пятый выход блока управления

45

50

55

520

6074

Формула

изобретения

520t5

25

30 ий регистры, блок ключей, причем выход второго регистра подключен к

1. Модуль процессора цифровой фильтрации, срдержащий блок памяти, первый регистр, сумматор, пять сдвиговых регистров, причем выход блока памяти подключен к первому информационному входу сумматора, информационный выход которого подключен к информационному входу первого регистра, выход которого подключен к второму информационному бходу сумматора,, выход переняса которого является выходом переноса процессора, входом переноса которого является вход переноса сумматора, входы последовательного занесения первого, второго, третьего, четвертого и пятого сдвиго- вых регистров являются входами соответственно первого, второго, третьего, четвертого и пятого коэффициентов первой группы процессора, выход первого регистра подключен к входу параллельного занесения информации пятого сдвигового регистра, отличающийся тем, что, с целью сокращения аппаратурных затрат, он содержит блок управления, мультиплексор, счетчик адреса,второй и треинформационному входу блока памяти и входу параллельного занесения информации первого сдвигового регистра,

5 выходы первой, второй и третьей групп разрядов которого подключены соответственно к первому, второму и третьему информационным входам мультиплексора, выход которого подключен к ин0 формационному входу блока памяти, адресный вход которого подключен к первому выходу блока управления, второй и третий выходы которого подключены соответственно к управляющему входу мультиплексора и счетному входу счетчика адреса, информационный выход которого подключен к четвертому информационному входу мультиплексора, четвертый выход блока управления подключен к тактовым входам сдвиговых регистров с первого по пятый, выходы последовательной выдачи информации которых соединены с входами коэффициентов соответственно с первого по пятый второй группы процессора и поразрядно подключены к пятому информационному пходу мультиплексора, пятый выход блока управления

5

0

5

713

подключен к тактовому входу первого регистра, выход которого подключен к информационпому входу третьего регистра, вьгход которого подключен к информационному входу блока ключей, выход которого подключен к информационному входу второго регистра и является информационным выходом процессора, входом разрешения записи информации и входом выбора режима которого являются соответственно вход разрешения записи второго регистра и управляющий вход блока ключей, тактовый вход третьего регистра и установочный вход первого сдвигового регистра подключены соответственно к шестому и седьмому выходам блока управления, входы с первого по шестой которого являются соответственно входом кода команды, входом разрешения записи команды, первым и вторым тактовыми входами, входом сброса и третьим такто- Bbw входом процессора.

2. Процессор по п. 1, отличающийся тем, что блок управления содержит узел ключей, счетчик, пер- вьй, второй и третий регистры, дешиф- jparop, вьгход которого подключен к ин748

формационному входу первого регистра, выход которого подключен к первому информационному входу узла ключей и установочному входу счетчика, инфор- мационный выход которого подключен к информационному входу второго регистра и первому входу дешифратора, второй вход которого подключен к выходу третьего регистра, информационный

вход и вход разрешения записи которого являются соответственно первым и вторым входами блока, третьим и четвертым входами которого являются соответственно тактовый и установочный

входы второго регистра, информационный выход которого подключен к второму информационному входу узла ключей, выходы с первого по седьмой которого являются соответственно пятым, первым, вторым, третьим, четвертым, седьмым и шестым выходами блока, пятым входом которого является вход сброса счетчика, счетный вход которого соединен с тактовым входом первого регистра и подключен к выходу

старшего разряда второго регистра,.а управляющий вход узла ключей является шестым входом блока.

.

Редактор Н.Лазаренко

Заказ 2372/56

Тираж 901Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 13035, Москва. Ш-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель А.Баранов

Техред И.ПоповичКорректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| ДИСПЛЕЙ | 1990 |

|

RU2015536C1 |

| Цифровой фильтр | 1985 |

|

SU1302296A1 |

Изобретение относится к области вычислительной техники и предназначено для использования в распределенных микропроцессорных системах цифровой обработки речевых и акустических сигналов. Цель изобретения - сокращение аппаратурных затрат. Для достижения поставленной цели в состав модуля процессора входят сдвиговые per гистры, мультиплексор, блок памяти, сумматор, регистр, счетчик адреса, регистры, блок ключей и блок управления. Наличие выходов переноса сумматора дает возможность объединять модули процессоров с целью увеличения разрядности. 1 з.п. ф-лы, 5 ил. (Л со о: vl

| Рабинер Л.,Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| -М.: Мир, 1978, Гольденберг Л.М | |||

| и др | |||

| Цифровые устройства на интегральных схемах в технике связи.-М.: Связь, 1979, с | |||

| Вага для выталкивания костылей из шпал | 1920 |

|

SU161A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-06-07—Публикация

1986-02-24—Подача