(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном звукозаписи | 1985 |

|

SU1260969A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Параллельно-последовательный сдвигающий регистр | 1973 |

|

SU480115A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ СДВИГАЮЩИЙРЕГИСТР | 1972 |

|

SU337825A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМИ ДВИГАТЕЛЯМИ | 1972 |

|

SU330433A1 |

1

Изобретение относится к области вычислительной техники и может быть исиользовано в устройствах намяти для хранения значений подынтегральной функции параллельиых цифровых интегрирующих машин, сопряженных с ЦВМ общего назначения.

Известны устройства, содержащие основные регистры, выполненные на триггерах, соединенных последовательно через вентили записи, собирательпые схемы, дешифратор адреса и вспомогательный регистр; нричем входы вентилей записи четных разрядов основных регистров соединены с первой шиной тактовых импульсов, а входы вентилей записи нечетных разрядов - со второй шиной тактовых импульсов.

Недостатком известных устройств являются значительные затраты времени при обмене числовыми данными цифровой интегрирующей машины, иснользующей известную намять, с ЦВМ, так как ввод (вывод) начальных значений подынтегральной функции в основные регистры осуществляется носледовательным кодом.

Целью изобретения является повышение быстродействия ЗУ.

Поставленная цель достигается за счет того, что предложенное устройство содержит дополнительные вентили записи нуля и единицы и вентили считывания единицы для каждого нечетного триггера основных регистров. Нулевой выход каждого триггера вспомогательного регистра соединен с одним из входов дополнительного вентиля записи нуля соответствующего нечетного триггера основного регистра, а единичный - с одним из входов дополнительного вентиля записи единицы соответствующего нечетного триггера каждого основного регистра. Другие входы

донолнительных вентилей записи нуля и единицы и одии из входов вентиля считывания каждого нечетного триггера основного регистра подключены к соответствующему выходу дешифратора адреса. Другие входы вентилей

считывания соединены с единичным выходом нечетного триггера основного регистра, а выходы вентилей считывания каждого соответствующего нечетного триггера основиых регистров подключены через собирательную схему

к единичному входу соответствующего триггера вспомогательного регистра. Выходы дополнительных вентилей записи нуля и едииицы подключеиы соответственно к нулевому и единичному входам нечетных триггеров основных

регистров.

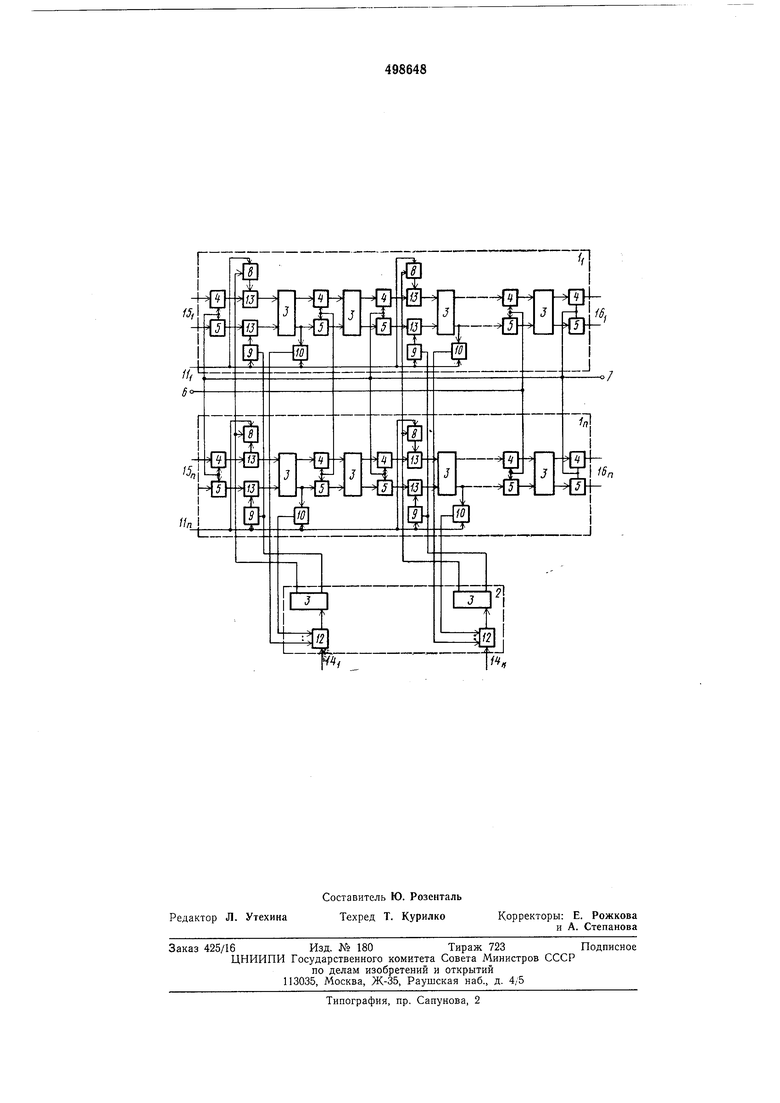

Схема ЗУ представлена на чертеже. ЗУ состоит из основных регистров li-1« и вспомогательного регистра 2.

Основные регистры выполнены на триггеpax 3, соединенных последовательно через

вентили записи нуля 4 и единицы 5. Другие входы вентилей записи четных разрядов основных регистров соединены с первой шиной 6 тактовых импульсов, а другие входы вентилей записи нечетных разрядов - со второй шиной 7 тактовых импульсов.

Нулевой выход каждого триггера 3 регистра 2 соединен с одним из входов дополнительного вентиля записи нуля 8 соответствуюш,его нечетного триггера каждого основного регистра, а единичный выход каждого триггера регистра 2 - с одним из входов вентиля записи единицы 9 соответствуюпдего нечетного триггера каждого регистра 1. Другие входы вентилей записи нуля и единицы 8 и 9 и один из входов вентиля считывания 10 каждого нечетного триггера регистра 1 соответственно подключены к одному из выходов 111 - Дбшифратора адреса. Другие входы вентилей считывания 10 соответственно соединены с единичными выходами нечетных триггеров регистров 1, а выходы вентилей считывания 10 каждого н-ечетного триггера этих регистров подключены через собирательную схему 12 к единичному входу соответствуюш,его триггера регистра 2. Выходы вентилей записи нуля 4 и 8 и вентилей единицы 5 и 9 подключены через собирательные схемы 13 соответственно к нулевым и единичным входам триггеров регистров 1. Входы 14i-14й используются для занесения числа из ЦВМ, а входы 15i-15п - для подключения соответствующих выходов интеграторов цифровой интегрирующей машины. Кроме того, каждый выход 16i-16и соединен со входом соответствующего интегратора. Для вывода результатов рещения интеграторов в память ЦВМ используются единичные выходы триггеров регистра 2 (на чертеже не показаны).

Предложенное ЗУ работает в двух режимах: в режиме решения цифровой интегрирующей мащины (ЦИМ) и в режиме обмена информацией ЦИМ с ЦВМ или внешними устройствами.

В первом режиме основные регистры используются в качестве параллельно-последовательной памяти цифровой интегрирующей мащины, т. е. в каждом основном регистре соответствующего интегратора информация циркулирует последовательно, а во всех интеграторах информация обрабатывается одновременно (параллельно).

С помощью первой и второй серий тактовых импульсов, поступающих соответственно, на щины 6 и 7, осуществляется сдвиг информации в регистрах, т. е. выполняется ее циркуляция в каждом интеграторе ЦИМ. Причем в двухтактных основных сдвигающих регистрах промежуточное хранение информации осуществляется в четных триггерах, а нечетные триггеры являются основными.

Во втором режиме записываемое число из ЦВМ ио входам HI-14/j заносится во вспомогательный регистр. Разрешение на запись числа в основной регистр выполняет дешифратор адреса сигналом на одной из выходных шин . Аналогично выполняется считывание числа из определенного основного регистра во вспомогательный регистр, из которого затем число передается в память ЦВМ или

во внешнее устройство.

Предмет изобретения

Запоминающее устройство, содержащее основные регистры, выполненные на триггерах, соединенных последовательно через вентили записи, собирательные схемы, дешифратор адреса и вспомогательный регистр, причем входы вентилей записи четных разрядов основных регистров соединены с первой шиной тактовых импульсов, а входы вентилей записи нечетных разрядов - со второй щиной тактовых имп)льсов, отличающееся тем, что, с целью повыщения быстродействия устройства,

оно содержит дополнительные вентили записи нуля и единицы и вентили считывания единицы для каждого нечетного триггера основных регистров; причем нулевой выход каждого триггера вспомогательного регистра соединен

с одним из входов дополнительного вентиля записи нуля соответствующего нечетного триггера каждого основного регистра, а единичный - с одним из входов дополнительного вентиля записи единицы соответствующего

нечетного триггера каждого основного регистра; другие входы дополнительных вентилей записи нуля и единицы и один из входов вентиля считывания каждого нечетного триггера основного регистра подключен к соответствующему выходу дешифратора адреса; другие входы вентилей считывания соединены с единичным выходом каждого нечетного триггера основного регистра, а выходы вентилей считывания каждого соответствующего нечетного

триггера основных регистров подключены через собирательную схему .к единичному входу соответствующего триггера всиомогательного регистра; выходы дополнительных вентилей записи нуля и единицы подключены соответственно к нулевому и единичному входам нечетных триггеров основных регистров.

Авторы

Даты

1976-01-05—Публикация

1974-04-19—Подача