Известны комбинированные цифровые вычислительные машины, содержащие оперативное запоминающее устройство, постоянное запоминающее устройство, арифметическое устройство, включающее сумматоры, накопительные регистры, регистры частного - множителя, вентили выборки приращений, схему выделения масштаба, вентили передачи прямого и дополнительного кода подынтегральной функции, устройство управления, включающее вентили передачи и устройство ввода - вывода.

Предлагаемая машина отличается тем, что содержит четыре идентичных вычислительных канала, выходы регистра частного - множителя и накопительного регистра которых соединены через вентили выборки с первыми входами сумматоров и через вентили выборки приращений независимой переменной - со схемой умножения, а также через вентили выборки приращений подынтегральной функции, регистр и пять схем задержки - с первым входом сумматора формирования суммы приращений, выход которого через промежуточный регистр связан со вторым входом этого сумматора. Выход промежуточного регистра соединен с регистром сдвига, выход которого подключен через схему задержки к первому входу сумматора первого канала и через вентили прямого и дополнительного кода - ко второму входу сумматора второго канала. Выход сумматора первого канала подсоединен к первому входу сумматора второго канала, а выход сумматора второго канала - к схеме умножения. Выходы схемы умножения связаны с первым и вторым входом сумматора третьего канала, выход которого подключен к первому входу сумматора четвертого канала, а выход сумматора четвертого канала через вентили прямого и дополнительного кода соединен с регистром хранения приращений интеграла.

Это позволяет повысить быстродействие.

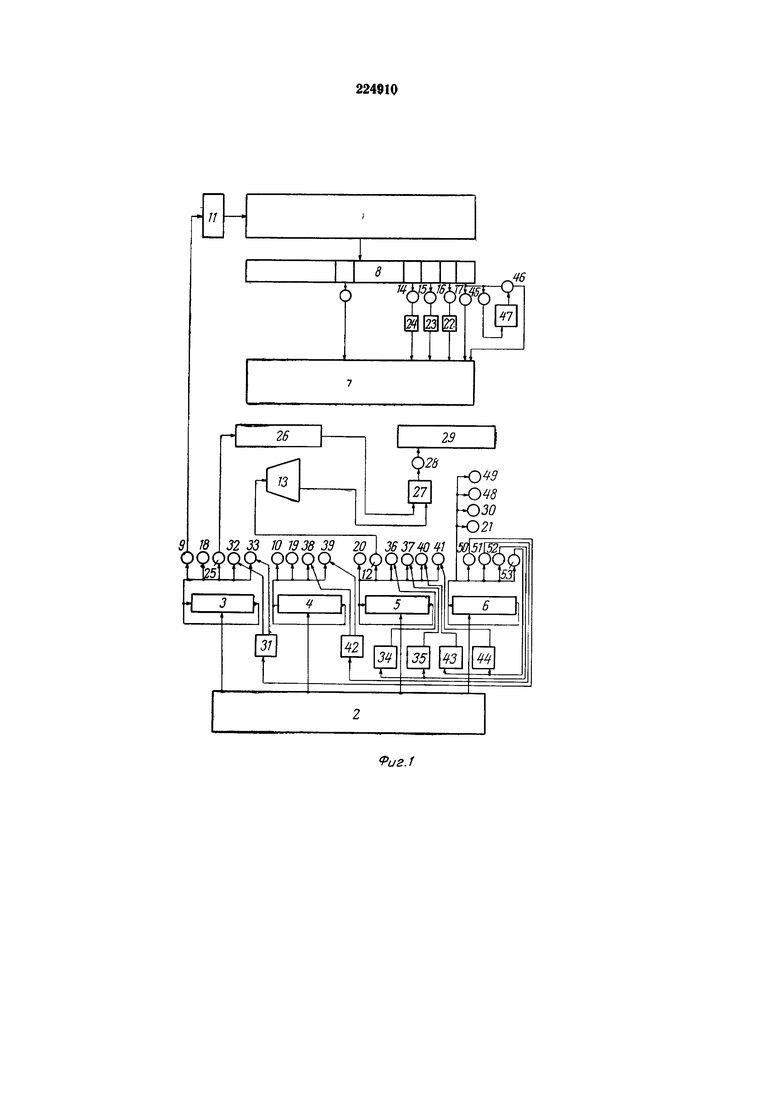

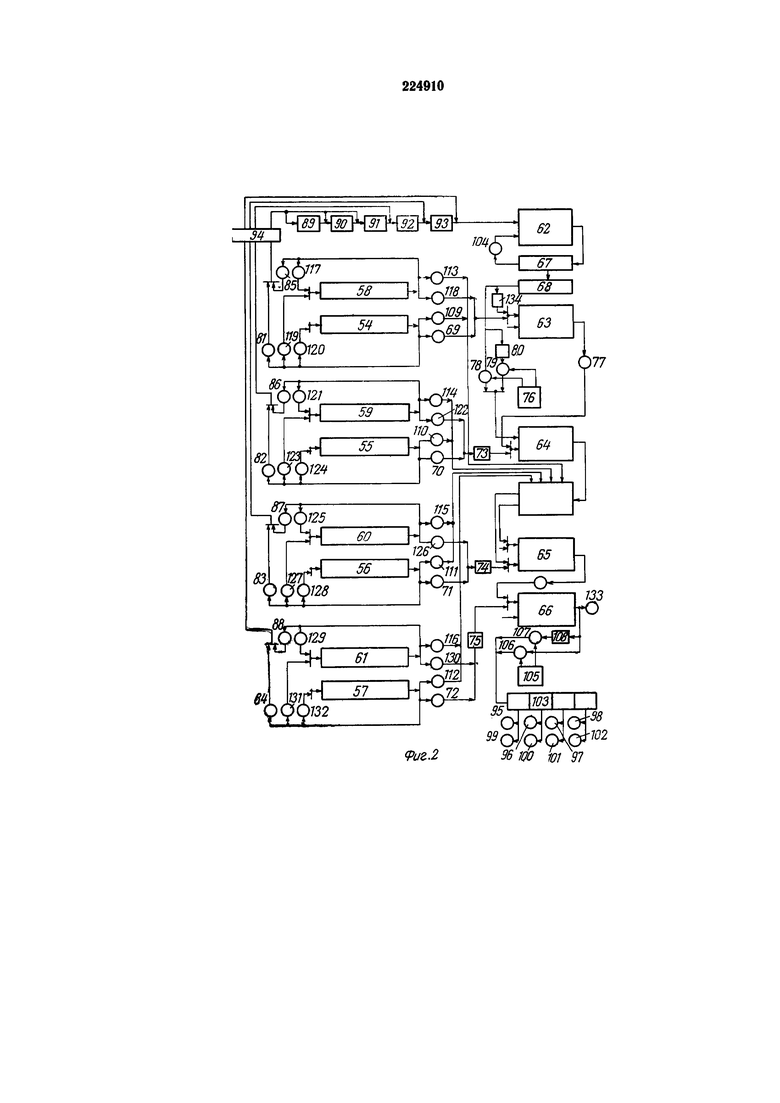

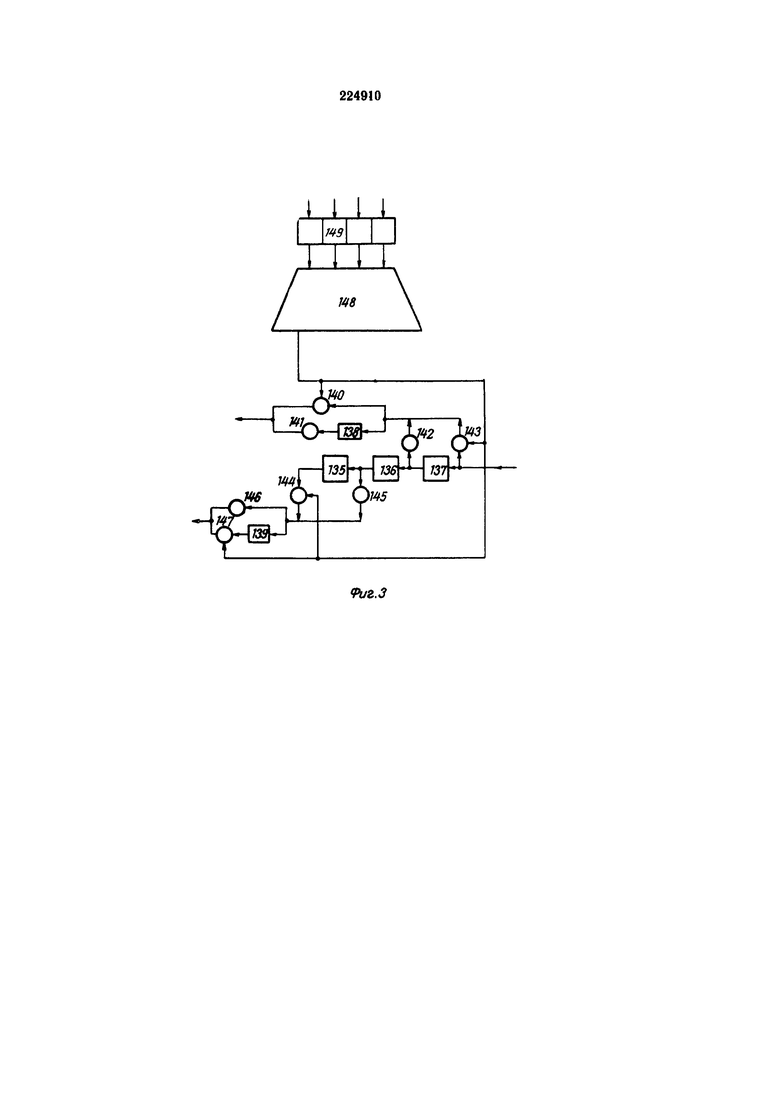

На фиг. 1 представлена блок-схема машины; на фиг. 2 - развернутая блок-схема вычислительного устройства; на фиг. 3 - схема умножения.

В состав машины входят оперативное запоминающее устройство 1, постоянное запоминающее устройство 2, регистры 3-6, вычислительное устройство 7, регистр 8, вентили 9 и 10, дешифратор 11, вентиль 12, дешифратор кода операции 13, вентили 14-21, схемы задержки 22-24, вентиль 25, счетчик номера команд 26, триггер 27 признака интегрирования, вентиль 28, схема управления операциями 29, вентиль 30, триггер 31, вентили 32 и 33 программ соединения интеграторов, триггеры 34 и 35, вентили 36-41 программ соединения интеграторов, триггеры 42-44, вентили 45 и 46, триггер 47, вентили 48-53, накопительные регистры 54-57, регистры частного-множителя 58-61, одноразрядные сумматоры 62-66, промежуточный регистр 67, сдвигающий регистр 68, вентили 69-72, схемы задержки 73-75, триггер 76 метода интегрирования, вентили 77-79, схема «НЕ» 80, вентили 81-88 выборки приращений на вход зависимой переменной, схема задержки 89-93, промежуточный регистр 94, вентили 95-102 записи нового приращения, регистр 103 хранения, вентиль 104, триггер 105 перемены знака, вентили 106 и 107, схема «НЕ» 108, вентили 109-116 выборки приращений независимой переменной, вентили 117-133, схема «НЕ» 134, схемы задержки 135-137, схемы «НЕ» 138 и 139, вентили 140-147, дешифратор 148 умножения и регистр 149.

Четырехканальная цифровая машина универсального типа с переключением на режим инкрементной машины включает оперативное запоминающее устройство 1 для хранения чисел, необходимых при работе в режиме машины универсального типа, а также значений подынтегральной функции Y, остатка S и приращений, требующих длительного хранения.

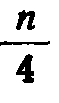

В ячейках устройства 1 принято следующее распределение разрядов: числа машины универсального типа хранятся общепринятым способом (число записывается в одну ячейку памяти, разряды расположены в порядке возрастания); подынтегральная функция Y одного интегратора занимает правую половину двух смежных ячеек, а остаток S - левую половину тех же ячеек; одна ячейка хранит приращения  интеграторов, где n - количество разрядов в машине. Приращение вместе со знаком занимает четыре разряда, т.е. максимальное положительное приращение равно 0,111, а максимальное отрицательное приращение равно 1,000 (все числа записываются в дополнительном коде). Распределение разрядов в ячейке, хранящей приращения, следующее: разряды 1÷4 хранят приращения одного интегратора, разряды 5÷8 приращение второго интегратора и т.д.

интеграторов, где n - количество разрядов в машине. Приращение вместе со знаком занимает четыре разряда, т.е. максимальное положительное приращение равно 0,111, а максимальное отрицательное приращение равно 1,000 (все числа записываются в дополнительном коде). Распределение разрядов в ячейке, хранящей приращения, следующее: разряды 1÷4 хранят приращения одного интегратора, разряды 5÷8 приращение второго интегратора и т.д.

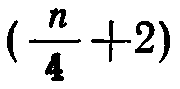

Постоянное запоминающее устройство 2 служит для хранения команд, констант и программ соединения интеграторов инкрементной машины. Число, считанное из устройства 2, поступает на четыре регистра 3-6, каждый из которых содержит по  разряда.

разряда.

Если из устройства 2 считывается команда, то в регистры 3 и 4 записывается адрес числа, а в регистры 5 и 6 - код операции и признаки модификации. Константы записываются в ячейки таким образом, что при считывании в регистр 3 записываются 1, 5, 9, …, (n-3) разрядов константы, в регистр 4 - разряды 2, 6, 10, …, (n-2), в регистр 5 - разряды 3, 7, 11, …, (n-1) и в регистре 6 - разряды 4, 8, 12, …, n.

Принято, что на вход зависимой переменной каждого интегратора может поступать до четырех приращений. При этом для каждого интегратора требуется хранить шесть программ: четыре программы выборки приращений на вход ΔY-aY1-aY4, программу выборки приращений на вход ΔX-aX и программу aS записи нового приращения. Программы выборки и записи приращений хранятся в двух ячейках устройства 2. При считывании одной из этих ячеек на регистр 3 записывается программа αY1, на регистр 4 - программа αY2, на регистр 5 - программа aS и на регистр 6 записывается код признаков.

Три первые разряда кода, записанного на регистре 6, указывают, на какие регистры вычислительного устройства 7 должны быть поданы программы aY1, aY2, aS. Четвертый разряд кода является признаком метода интегрирования. Интегрирование в зависимости от места данного интегратора в общей схеме набора может производиться по интерполяционной или экстрополяционной формуле трапеций. В случае n>16 остальные разряды регистра 6 не используются. При считывании второй ячейки, хранящей программы соединения интеграторов, на регистры 3-5 записываются соответственно программы aY3, aY4, аХ. На регистр 6 устанавливаются признаки, три из которых имеют такие же функции, как и в предыдущем случае, четвертый говорит о том, нужно ли изменять знак приращения на выходе данного интегратора.

Вычислительное устройство 7 состоит из четырех накопительных регистров 54-57 по  разряда в каждом, четырех регистров частного - множителя 58-61 также по

разряда в каждом, четырех регистров частного - множителя 58-61 также по  разряда в каждом, пяти сумматоров 62-66 и двух шестиразрядных регистров: регистр 67 и сдвигающий регистр 68. Эти регистры служат для промежуточного хранения.

разряда в каждом, пяти сумматоров 62-66 и двух шестиразрядных регистров: регистр 67 и сдвигающий регистр 68. Эти регистры служат для промежуточного хранения.

При работе в режиме машины универсального типа регистры 54-57 служат для хранения промежуточных результатов, причем в регистре 54 хранятся 1, 5, 9, …, (n-3) разряды числа, в регистре 55 - разряды 2, 6, 10, …, (n-2), в регистре 56 - разряды 3, 7, 11, …, (n-1) ив регистре 57 - разряды 4, 8, 12, …, n.

В режиме инкрементной машины эти регистры хранят приращения  интеграторов. В регистре 54 записываются знаковые разряды всех приращений, в регистр 55 - старшие разряды приращений, в регистр 56 - вторые значащие разряды и в регистр 57 - младшие разряды.

интеграторов. В регистре 54 записываются знаковые разряды всех приращений, в регистр 55 - старшие разряды приращений, в регистр 56 - вторые значащие разряды и в регистр 57 - младшие разряды.

В режиме машины универсального типа регистры 58-61 хранят частное при делении и множитель при умножении, причем распределение разрядов в них так же, как и в накопительных регистрах. Функции регистров частного-множителя в режиме инкрементной машины аналогичны функции накопительных регистров.

При работе в режиме машины универсального типа сумматоры 63-66 служат для сложения двух чисел, одно из которых поступает из накопительных регистров, второе - из регистра 8 (сумматор 62 не используется).

В режиме инкрементной машины сумматор 62 служит для образования величины ΣΔY. На выходе сумматора 63 получается новое значение Y.

Yj+1=Yj+ΣΔY, где j номер итерации.

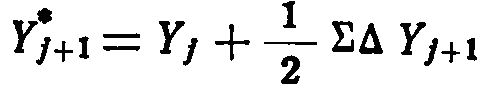

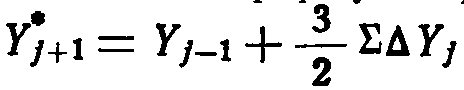

Сумматор 64 служит для образования  при интегрировании по интерполяционной формуле трапеций и величины

при интегрировании по интерполяционной формуле трапеций и величины  при интегрировании по экстраполяционной формуле траций.

при интегрировании по экстраполяционной формуле траций.

С помощью сумматора 65 образуется величина Y* ΔХ, а сумматор 66 служит для сложения предыдущего остатка S с величиной Y* ΔX.

Рассмотрим работу в режиме машины универсального типа.

Из устройства 2 считывается текущая команда. Адрес числа через вентили 9 и 10 передается на дешифратор 11, а код операции с помощью вентиля 12 поступает на дешифратор кода операции 13. Число на регистре 8 сдвигается каждый такт на четыре разряда вправо, благодаря чему в вычислительное устройство 7 число, считанное из устройства 2, поступает по четырем каналам за  такта (работают вентили 14-17).

такта (работают вентили 14-17).

Если выполняется операция над постоянным числом, то оно считывается не из регистра 8, а из регистров 3-6 через вентили 18-21. Второе число поступает из накопительных регистров 54-57 (работают вентили 69-72). Переносы с выхода сумматоров 63-66 поступают соответственно на вход сумматоров 64-66, 63. Для синхронизации кодов, поступающих из накопительных регистров 54-57 и из регистра 8, с поступлением переноса введены схемы задержки 22-24 и 73-75. Время задержки на схемах 73 и 22 равно tn, на схемах 74 и 23-2tn и на схемах 75 и 24-3tn, где tn - время образования переноса в сумматоре.

Для нормальной работы необходимо, чтобы

4tn≤t,

где t - период тактовых импульсов. Это условие обычно выполняется. Результат операции либо сохраняется в накопительных регистрах, либо поступает в устройство 1. Все короткие операции в режиме машины универсального типа выполняются за один период, равный  такта.

такта.

При переключении на режим инкрементной машины первые три периода являются подготовительными. В течение двух периодов содержимое обеих линеек устройства 1, хранящих приращения, полученные в предыдущей операции, переписываются в накопительные регистры и регистры частного-множителя. В третьем периоде из устройства 2 через вентиль 25 на счетчик номера команд 26 устанавливается код, соответствующий числу интеграторов, необходимых для решения данной задачи Одновременно устанавливается в единицу триггер 27, который находится в этом состоянии в течение всего времени работы в режиме инкрементной машины. Вентиль 28 управляется единичным выходом триггера 27 и тактовым импульсом. Выходной сигнал этого вентиля, поступающий на схему управления операциями 29, является признаком работы в режиме инкрементной машины.

Для выполнения одного интегрирования в режиме последовательной инкрементной машины нобходимо время,

tU=(n+к+2)t=(n+6)t,

где к - количество разрядов в коде приращений. Однако, с целью упрощения схемы принято, что время работы одного интегратора равно четырем периодам машины универсального типа, т.е. tU=(n+8) тактов.

Работу в режиме инкрементной машины рассмотрим на примере i-интегратора.

Для увеличения быстродействия приращения ΔY и ΔХ на вход i-интегратора выбираются, начиная с четвертого периода работы (i-2)-интегратора, а приращения ΔS записываются во время работы (i+1)-интегратора.

В начале четвертого периода работы (i-2)-интегратора в регистры 3-5 устанавливаются программы aY1, aY2 i-интегратора и программа aS(i-2) интегратора. На регистр 6 записывается код признаков. Два первых разряда этого кода указывают из каких регистров вычислительного устройства (накопительных или регистров частного-множителя) должны выбираться приращения ΔY1 и ΔY2 на вход i-интегратора. Третий разряд указывает, в какой регистр должно записываться приращение, выработанное (i-2)-интегратором, и четвертый разряд является признаком метода интегрирования, применяемого в (i-1)-интеграторе. Если в четвертом разряде записана «1», то триггер 76 устанавливается в «единицу» сигналом с выхода вентиля 30. При этом к величине Y(i-2)j+1=Y(i-2)j+ΣΔY, поступающей с выхода сумматора 63 через вентиль 77, добавляется величина  (работает вентиль 78), т.е. реализуется экстраполяционяая формула трапеции. В противном случае величина

(работает вентиль 78), т.е. реализуется экстраполяционяая формула трапеции. В противном случае величина  подается на вычитание (работают вентиль 79 и схема «НЕ» 80), т.е. интегрирование выполняется интерполяционным методом. Если в первом разряде кода на регистре 6 записан ноль (триггер 31 находится в состоянии «0»), то программа αY1 через вентиль 32 передается на вентили 81-84 выборки приращений из накопительных регистров 54-57. При коде «1» состояние триггера 31 изменяется на обратное, и программа aY1 через вентиль 33 передается на вентили выборки приращений из регистров частного-множителя. Приращение ΔY1 преобразуется в последовательный код с помощью схем задержек 89-93. Так как на вход интегратора может поступать до четырех приращений, то величина ΣΔY занимает шесть разрядов. Для этого код знака приращения ΔY1 поступает на три последовательно включенные схемы задержки 89-91, две из которых (схемы задержки 90 и 91) служат для наращивания знака приращений. С выхода сумматора 62 приращение ΔY1 поступает для промежуточного запоминания на шестиразрядный последовательный регистр 67. Регистр 94 служит для синхронной подачи приращений на вход сумматора 62, так как приращения из регистров вычислительного устройства выбираются по любому такту. Приращение, выбранное в любом такте е периода из регистра 94, выдается в первом такте (е+1)_периода. Если в третьем разряде регистра 6 записан ноль, то триггер 34 устанавливается в единицу, а триггер 35 остается в нуле, и программа через вентиль 36 поступает на вход вентилей 95-98. Приращение ΔS (i-2)-интегратора из регистра 103 записывается в накопительные регистры 54-57. При коде «0» состояние триггеров 34 и 35 изменяется, программа через вентиль 37 передается на вентили 99-102, и приращение ΔS записывается в регистры частного - множителя 58-61.

подается на вычитание (работают вентиль 79 и схема «НЕ» 80), т.е. интегрирование выполняется интерполяционным методом. Если в первом разряде кода на регистре 6 записан ноль (триггер 31 находится в состоянии «0»), то программа αY1 через вентиль 32 передается на вентили 81-84 выборки приращений из накопительных регистров 54-57. При коде «1» состояние триггера 31 изменяется на обратное, и программа aY1 через вентиль 33 передается на вентили выборки приращений из регистров частного-множителя. Приращение ΔY1 преобразуется в последовательный код с помощью схем задержек 89-93. Так как на вход интегратора может поступать до четырех приращений, то величина ΣΔY занимает шесть разрядов. Для этого код знака приращения ΔY1 поступает на три последовательно включенные схемы задержки 89-91, две из которых (схемы задержки 90 и 91) служат для наращивания знака приращений. С выхода сумматора 62 приращение ΔY1 поступает для промежуточного запоминания на шестиразрядный последовательный регистр 67. Регистр 94 служит для синхронной подачи приращений на вход сумматора 62, так как приращения из регистров вычислительного устройства выбираются по любому такту. Приращение, выбранное в любом такте е периода из регистра 94, выдается в первом такте (е+1)_периода. Если в третьем разряде регистра 6 записан ноль, то триггер 34 устанавливается в единицу, а триггер 35 остается в нуле, и программа через вентиль 36 поступает на вход вентилей 95-98. Приращение ΔS (i-2)-интегратора из регистра 103 записывается в накопительные регистры 54-57. При коде «0» состояние триггеров 34 и 35 изменяется, программа через вентиль 37 передается на вентили 99-102, и приращение ΔS записывается в регистры частного - множителя 58-61.

В начале первого периода работы (i-1)-интегратора на вентили 38 и 39 поступает программа aY2. Если во втором разряде регистра 6 записан ноль, то состояние триггера 42 не изменяется, и программа аУ2 через вентиль 38 передается на вентили 81-84 выборки приращений из накопительных регистров. При коде «единица» во втором разряде триггер 42 устанавливается в единицу, и программа аУ2 через вентиль 39 поступает на вентили 85- 88 выборки приращений из регистров частного-множителя. Приращение ΔY2 преобразуется на схемах задержек 89-93 в последовательный код и суммируется с величиной приращения ΔY1, которая поступает на сумматор 62 из регистра 67 через вентиль 104. Величина ΔY1+ΔY2 с выхода сумматора записывается в регистр 67. Во втором периоде работы (i-1)-интегратора на регистры 3-6 устанавливаются соответственно программы aY3, aY4, аХ и код признаков. Выборка приращений ΔY3 и ΔY4 осуществляется аналогично выборке приращений ΔY1 и ΔY2, причем приращение ΔY3 выбирается во втором периоде, а приращение ΔY4 - в третьем периоде.

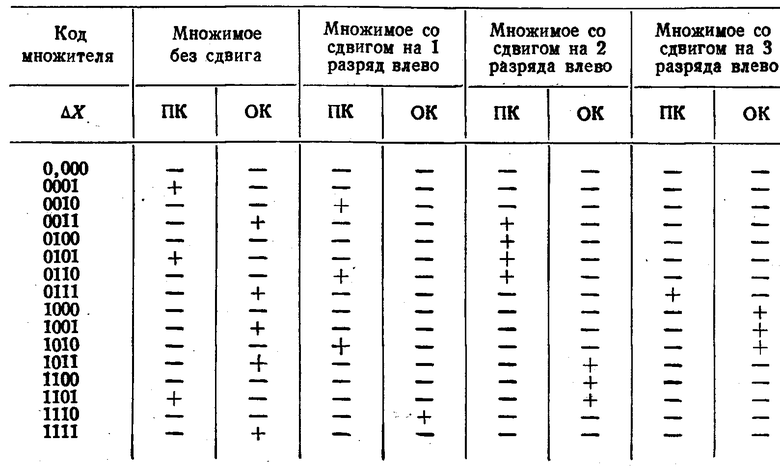

В четвертом разряде регистра 6 записывается признак перемены знака на выходе (i-1)-интегратора. Этот признак поступает на вход установки в единицу триггера 105. В зависимости от состояния этого триггера приращение ΔS с выхода сумматора 66 записывается в регистр 103 либо в прямом коде (работает вентиль 106), либо в дополнительном коде (работают вентиль 107 и схема «НЕ» 108). Приращение ΔХ с выхода вентилей 109-112 или вентилей 113-116 поступает на схему умножения. Умножение на приращение АХ выполняется согласно следующей таблице:

Знаки в таблице означают, что данное значение множимого подается на сумматор 65. Например, при ΔХ=1,101 на сумматор 65 подается прямой код множимого без сдвига и обратный код множимого, сдвинутого на два разряда влево.

Данная таблица реализуется схемой, выключающей схемы задержки 135-137, схемы «НЕ» 138 и 139 и вентили 140-147. Управление этой схемой осуществляется выходными шинами дешифратора 148. Регистр 149 служит для промежуточного хранения ΔX.

Коды Y и S поступают из регистра 8 в начале первого периода работы г-интегратора. Вентили 45, 46 и триггер 47 служат для выделения начального импульса (масштаба) в коде Y. Триггер 47 управляет также выдачей содержимого сдвигающего регистра 68, которое подается на вход сумматора 63 для образования нового значения Yi,j+1=Yi,j+ΣΔY, а также на вход сумматора 64 для образования величины  На сумматор 66 поступает величина Y*·ΔХ, имеющая n+3 разряда и код S из регистра 8. С выхода сумматора 66 младшие n разрядов поступают в устройство 1, а в регистр 103 записываются знак и старшие три разряда. В случае, если регистров вычислительного устройства оказывается недостаточным для хранения приращений, содержимое накопительных регистров может быть записано в устройство 1. В освободившиеся регистры либо записывают приращения, выработанные в предыдущей итерации, либо эти регистры остаются свободными в качестве оперативных регистров хранения.

На сумматор 66 поступает величина Y*·ΔХ, имеющая n+3 разряда и код S из регистра 8. С выхода сумматора 66 младшие n разрядов поступают в устройство 1, а в регистр 103 записываются знак и старшие три разряда. В случае, если регистров вычислительного устройства оказывается недостаточным для хранения приращений, содержимое накопительных регистров может быть записано в устройство 1. В освободившиеся регистры либо записывают приращения, выработанные в предыдущей итерации, либо эти регистры остаются свободными в качестве оперативных регистров хранения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ МОДЕЛИ | 1967 |

|

SU223472A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Цифровой интегратор | 1975 |

|

SU637833A1 |

| Стереоавтограф | 1960 |

|

SU147841A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU294156A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1968 |

|

SU219911A1 |

Комбинированная цифровая вычислительная машина, содержащая оперативное запоминающее устройство, постоянное запоминающее устройство, арифметическое устройство, включающее сумматоры, накопительные регистры, регистры частного-множителя, вентили выборки приращений, схему выделения масштаба, вентили передачи прямого я дополнительного кода подынтегральной функции, устройство управления, включающее вентили передачи и устройство ввода-вывода, отличающаяся тем, что, с целью повышения ее быстродействия, она содержит четыре идентичных вычислительных канала, выходы регистра частного-множителя и накопительного регистра которых соединены через вентили выборки с первыми входами сумматоров и через вентили выборки приращений независимой переменной - со схемой умножения, а также через вентили выборки приращений подынтегральной функции, регистр и пять схем задержки - с первым входом сумматора формирования суммы приращений, выход которого через промежуточный регистр связан со вторым входом этого сумматора, выход промежуточного регистра соединен с регистром сдвига, выход которого подключен через схему задержки к первому входу сумматора первого канала и через вентили прямого и дополнительного кода - ко второму входу сумматора второго канала, выход сумматора первого канала подсоединен к первому входу сумматора второго канала, а выход сумматора второго канала соединен со схемой умножения, выходы схемы умножения связаны с первым и вторым входом сумматора третьего канала, выход которого подключен к первому входу сумматора четвертого канала, а выход сумматора четвертого канала через вентили прямого и дополнительного кода соединен с регистром хранения приращений интеграла.

Авторы

Даты

1968-12-16—Публикация

1966-09-23—Подача