Изобретение относится к вычислительной технике и может быть иснользовано в цифровых управляющих машинах.

Известны многоканальные устройства для управления шаговыми двигателями, содержащие регистры для приема и хранения числа шагов двигателя и схемы коммутации обмоток шаговых двигателей в каждом канале, а также схемы местного управления, дешифрации, сравнения, сборки, счетчик и вентили.

Недостатками известных устройств управления шаговыми двигателями (ШД) являются их сложность и малая автономность по отношению к системе ввода-вывода и процессору.

Цель изобретения - сокрашение объема оборудования многоканального устройства управления шаговыми двигателями и расширение его функциональных возможностей.

Цель достигается тем, что в предлагаемом устройстве вместо цриемных регистров и коммутаторов обмоток ШД в каждом канале и общего счетчика эталонной частоты исиользованы счетчик каналов, общий для всех каналов счетчик обработки числа шагов и общая схема коммутации обмоток ШД. Эти элементы устройства связаны с оперативной памятью и схемой местного управления таким образом, что обеспечивается управление шаговыми двигателями в режиме разделения времени. Кроме того, предлагаемое устройство содержит регистр занятости каналов, число разрядов которого соответствует числу каналов устройства. Каждому каналу соответствует ячейка в оперативной памяти и разряд (триггер)

регистра занятости каналов. Иаличие механизма анализа занятости каналов (регистра занятости каналов, схемы поразрядного сравнения и схемы управления) в совокупности с принятой структурой управления обеспечивает

возможность запуска освободившихся каналов в каждом цикле работы рассматриваемого устройства (в интервале между любыми двумя шагами двигателя), т. е. высокую скорость вывода информации.

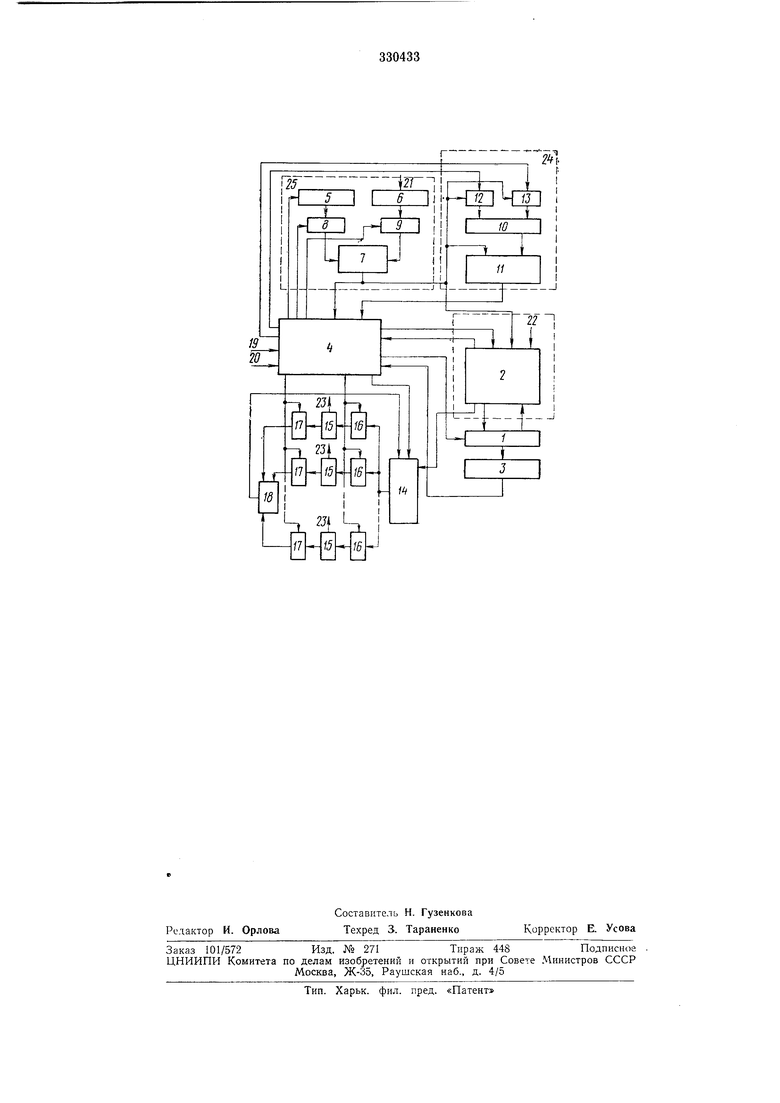

На чертеже представлена структурная схема предлагаемого устройства.

В состав многоканального устройства для управления шаговыми двигателями входят счетчик / отработки числа шагов, единичные входы и выходы которого связаны с блоком 2 оперативной памяти машины; схема 5 сравнения с нулем; схема 4 местного управления; счетчик 5 каналов; регистр 6 адресов каналов; дешифратор 7 номеров каналов, вентили

5 S и 9 коммутации адресов каналов; регистр 10 занятости каналов; схема // поразрядного сравнения сигналов; вентили установки 2 и сброса 13 регистра занятости каналов; схема 14 коммутации обмоток шаговых двигателей; регистры 15 кодовых комбинаций; вентили

записи 16 и считывания 17 кодовых комбинаций и собирательные схемы 18.

Устройство принимает из центрального процессора сигналы по шине 19, соответствующие командам вывода информации через данное многоканальное устройство, сигналы по шине 20 эталонной частоты, код адреса канала но шине 21, код числа шагов ШД по шине 22 и выдает кодовые комбинации по шпне 23 на силовые усилители ШД. Схема 24 анализа занятости каналов содержит регистр занятости каналов, схему поразрядного сравнения и вентили установки и сброса регистра занятости каналов.

Схема 25 дешифрации номера канала содержит счетчик каналов, регистр адресов каналов, дешифратор номеров каналов и вентили коммутации адресов каналов.

Сигналы, поступающие на вход схемы 4 местного управления по шине 20 (либо генерируемые схемой 4), задают цикл (период Т работы устройства. Частота следования этих импульсов не должна быть выше предельно допустимой частоты отработки шагов для самого медленнодействующего ШД, обслуживаемого данным Jcтpoйcтвoм. Время обслуживания одного ШД соответствует такту работы устройства многоканального управления. За время одного такта осуществляются либо прием и запись величины кода поворота ШД в блок оперативной памяти, либо смена кодовой комбинации одного ШД.

Одним многоканальным устройством управления можно обслужить п шаговых двигателеи, п - . Соответственно число разрядов регистра занятости канала и число ячеек оперативной памяти для такого устройства равно п.

В каждом такте работы устройства содержимое счетчика 5 каналов через венти пи S подается на дешифратор 7. Сигналы с дешифратора 7 сравниваются схемой 11 с сигналами с соответствующих входов регистра 10.

Если в сравниваемом /-ом разряде регистра 10 записан нуль, т. е. i-я ячейка памяти пуста и г-й канал свободен, то по сигналу со схемы 11 и при наличии сигнала по шине 19, соответствующего обращению центрального процессора к устройству управления ШД, схема 4 вырабатывает последовательность импульсов, необходимую для записи кода числа шагов из процессора в t-ю ячейку блока оперативной памяти. При этом прохождение кода адреса со счетчика 5 через вентили 8 блокикируется, а с регистра 6 через вентили 9 разрещается сигналами со схемы 4; код числа шагов с шины 22 записывается в блок 2 по адресу из регистра 5, и в соответствующий разряд регистра 10 через вентили 12 записывается единица.

Если в г-ом разряде регистра 10 записана единица, то по сигналу сравнения со схемы 11 содержимое f-й ячейки блока 2, кроме знакового разряда, считывается в счетчик I. Знаковый разряд подается на схему 14. Схема 4 местного управления формирует импульс запуска схемы 14 и соответствующие i-му каналу импульсы управления вентилями 16 и 17. Схема 14 принимает кодовую комбинацию из

0 i-ro регистра 15 через соответствующие вентили 17 и собирательные схемы 18, формирует новую кодовую комбинацию и возвращает ее через вентили 16 в t-й регистр 15.

Регистры 15 совместно со схемой 14, вентилями 16, 17 и схемами сборки 18 вынолняют функцию коммутации обмоток ШД и служат для обеспечения включения обмоток секций ШД на все время между управляющими импульсами со схемы 4 независи.мо от длитель0 ности последних.

Содержимое счетчика / корректируется (уменьщается на единицу), анализируется (сравнивается с нулем) схемой 3 и возвращается в прежнюю ячейку.

5 Если схема 3 вырабатывает нризнак нуля, то -й разряд регистра 10 сбрасывается (признак занятости t-ro канала стирается). В конце каждого такта работы устройства корректируется (увеличивается на единицу) содержимое счетчика каналов. Счетчик каналов обеспечивает последовательную адресацию каналов в каждом цикле работы устройства.

Ввод информации в блок 2 (запуск свободного канала) осуществляется в тех тактах, в которых не обслуживаются щаговые двигатели, т. е. в тактах, соответствующих разрядам регистра 10, которые находятся в нулевом состоянии, при - после отработки последнего (л-го) канала. .

Предмет изобретения

Многоканальное устройство для управления шаговыми двигателями, содержащее счетчик отработки числа шагов, соединенный со схемой сравнения и схемой местного управления, которая связана со схемой дешифрации номера канала, вентилями записи и считывания кодовых комбинаций, отличающееся тем,

что, с целью расширения функциональных возможностей и сокращения объема оборудования, она содержит схему анализа занятости канала, соедииенную со схемой дешифрации номера канала и схемой местного управления,

схему коммутации обмоток щаговых двигателей, соединенную со входом устройства и схемой местного управления, при этом единичные входы всех разрядов счетчика отработки числа шагов соединены со входами устройства, а

единичные выходы - с выходами устройства, счетный вход счетчика соединен с выходом схемы местного управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления п-шаговыми двигателями | 1983 |

|

SU1144183A1 |

| Многоканальное устройство для управления шаговыми двигателями | 1987 |

|

SU1481715A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМИ ДВИГАТЕЛЯМИ | 1971 |

|

SU292141A1 |

| Коммутатор для управления шаговым двигателем | 1987 |

|

SU1471175A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для измерения ошибок позиционирования шагового электродвигателя | 1990 |

|

SU1697254A1 |

| Многоканальное устройство для управления шаговыми двигателями | 1981 |

|

SU993212A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

| Устройство для программного управления шаговым двигателем | 1981 |

|

SU1012207A1 |

Даты

1972-01-01—Публикация