(54) УСТРОЙСТВО ДЛЯ КОНТР9ЛЯ ДВИЖЕНИЯ ТРАНСПОРТНОЮ СРЕДСТВА ПРИ ПЕРЕХОДЕ С ОДНОГО ПУТИ НА ДРУГОЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный распределитель импульсов | 1976 |

|

SU656209A1 |

| Устройство динамической памяти | 1972 |

|

SU611299A1 |

| ФОРМИРОВАТЕЛЬ ОДИНОЧНОГО СИГНАЛА | 1971 |

|

SU318162A1 |

| Устройство для выделения одиночного сигнала | 1976 |

|

SU648487A2 |

| Динамическая ячейка памяти | 1974 |

|

SU720512A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА АДРЕСОВ НА «МЕНЬШЕ»,«РАВНО» | 1969 |

|

SU249763A1 |

| ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА | 1965 |

|

SU171171A1 |

| Реверсивный счетчик | 1980 |

|

SU907813A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1973 |

|

SU372692A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

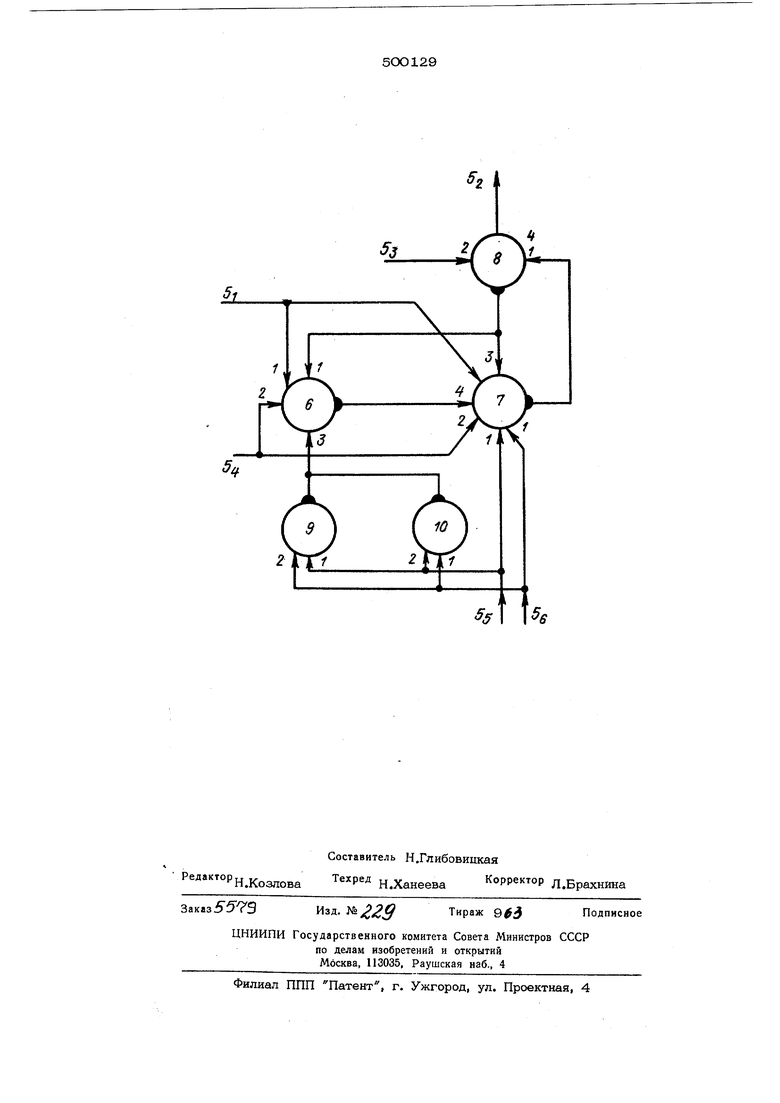

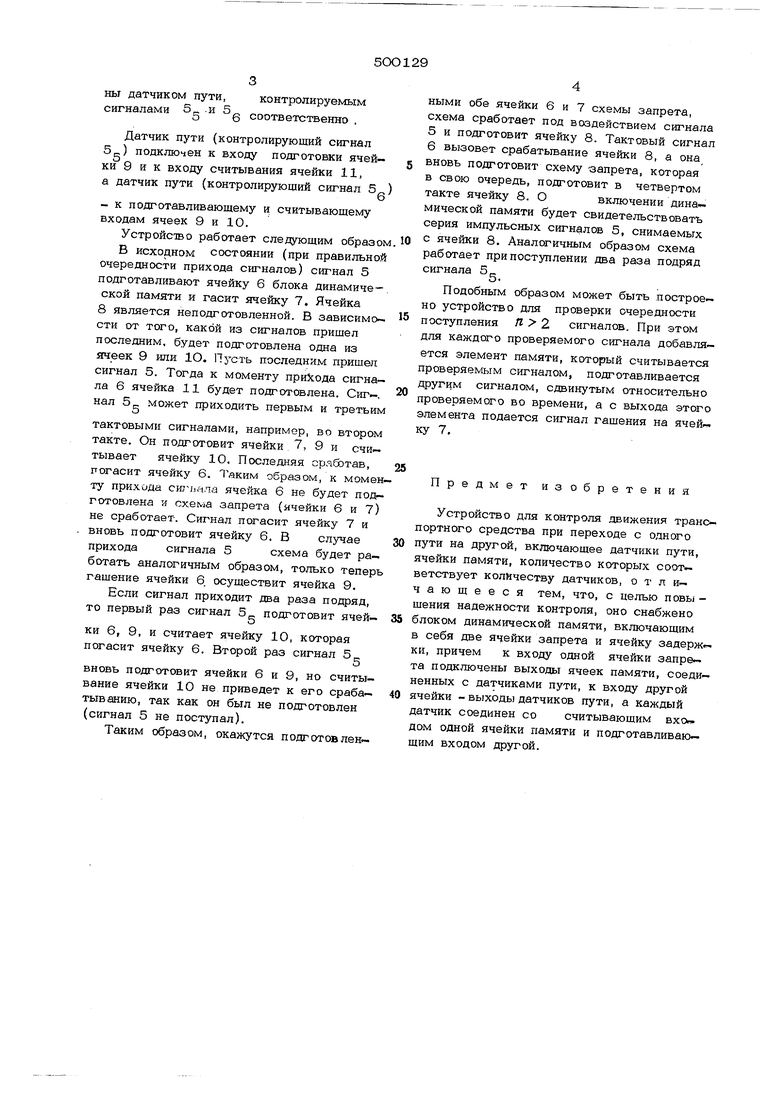

Изобретение касается устройства управ ления конвейерными устансеками и может быть использовано в различных устрс&ствё автоматики циклическ яо действия, где требуется контроль поступления сдвинутых во времени сигналов,, Известные устройства контролируют пр вильность прихода сигналов только; одног датчика (датчика входа), но могут дополнены так, чтобы контролироватьоба датчика. Однако известные устройства при ; срабатьГвании формируют одиночный импуль а для приема этого импульса и включения схемы сигнализации и защиты требуются дополнительные устройства. Цель.;: предлагаемого изобретения пчжышенйе надежности контроля движения транспс)тного средства. Это доствдается тем, что устройство снабжено блоком динамической памяти, включающим в себя две ячейки запрета и ячейку задержки,-причем к входу одной ячейки sanpSiTa подключены выходы ячеек памяти, соеди ненных с датчиками пути7 к I входу другой ячейки - выходы датчика пути, а каждый датчик соединен со считы-; вающим : входом одной ячейки памяти и . подготавливающим входом другой. . На чертеже показана функциональная схема устройства для контроля движения транспортното средства при переходе с одна1 о пути на другой, построенная на ферриттранзисторных ячейках. На чертеже приняты следующие обозна чения: 1« вход подготовки; 2 - вход считьтания, 3 - вход , гашения, 4 - aiHTw : тер транзистора элементбв. Позицией 5 обозначены тактсжые сигналы (индекс указывает на условный порядок сигнала в тактовом цикле). Блок динамической памяти построен на схемы запрета (ячейки 6 и 7) и элементе задержки (ячейка 8). В;;ход схемы запрета подключен к входу 2 подготовки ячейки 8, выход которой соединен с входами подготовки ячеек 6 и 7. К входу гашения ячейки 6 подключены выходы дополнительных элементов памяти (ячейки 9 и 10), а входы подготовки ячейки 7 соедпненьг датчиком пути, ко нтролируемым сигналами с 6 соответственно . Датчик пути (контролирующий сигнал 5) подключен к входу подготовки ячейки 9 и к входу считывания ячейки И, а датчик пути (контролирующий сигнал 5 - к подготавливающему и считывающему входам ячеек 9 и 10. Устройство работает следующим образом В исходном состоянии (при правильной очередности прихода сигналов) сигнал 5 подготавливают ячейку б блока динамиче- ской памяти и гасит ячейку 7. Ячейка 8 является неподготовленной. В зависимо- сти от того, какой из сигналов прищел последним, будет подготовлена одна из ячеек 9 или Ю. Пусть последним пришел сигнал 5. Тогда к моменту привода сигнала 6 ячейка 11 будет подготовлена. Сиг-, нал 5 может приходить первым и третьим тактовыми сигналами, например, во втором такте. Он подготовит ячейки 7, 9 и считывает ячейку 10. Последняя срябЬтав, погасит ячейку 6. Таким образом, к момен ту прихода сшчаала ячейка 6 не будет под готовлена и схема запрета (ячейки 6 и 7) не сработает. Сигнал погасит ячейку 7 и вновь подготовит ячейку 6. В случае прихода сигнала 5схема будет работать аналогичным образом, только тепер гашение ячейки 6 осуществит ячейка 9, Если сигнал приходит два раза подряд, то первый раз сигнал 5 подготовит ячейки 6, 9, и считает ячейку 10, которая погасит ячейку 6. Второй раз сигнал 5 вновь подготовит ячейки 6 и 9, но считывание ячейки 10 не приведет к его сраба- тыванию, так как он был не подготовлен (сигнал 5 не поступал). Таким образом, окажутся подготовленными обе ячейки 6 и 7 схемы запрета, схема сработает под воздействием сигнала 5и подготовит ячейку 8. Тактовый сигнал 6вызовет срабатьгоание ячейки 8, а она вновь подготовит схему -запрета, которая в свою очередь, подготовит в четвертом такте ячейку 8. Овключении динамической памяти будет свидетельствовать серия импульсных сигналов 5, снимаемых с ячейки 8. Аналогичным образом схема работает при поступлении два раза подряд сигнала 5 Подобным образом может быть построено устройство для проверки очередности поступления П 2 сигналов. При этом для каждого проверяемого сигнала добавляется элемент памяти, который считывается проверяемым сигналом, подготавливается другим сигналом, сдвинутым относительно проверяемого во времени, а с выхода этого элемента подается сигнал гашения на ячей- ку 7. Предмет изобретения Устройство для контроля движения транспортного средства при переходе с одного пути на другой, включающее датчики пути, ячейки памяти, количество которых соответствует количеству датчиков, отличающееся тем, что, с целью повы шения надежности контроля, оно снабжено блоком динамической памяти, включающим в себя две ячейки запрета и ячейку задержки, причем к входу одной ячейки запрета подключены выходы ячеек памяти, соединенных с датчиками пути, к входу другой ячейки - выходы датчиков пути, а каждый датчик соединен со считывающим вхо дом одной ячейки памяти и подготавливающим входом другой.

5i

2

Авторы

Даты

1976-01-25—Публикация

1972-02-03—Подача