1

Изобретение относится к 1обла€ти вьиислительной техники.

Известен распределитель импульсов на ферриттранзисторных ячейках, содержащий блок управления, выполненный иа 1генераторе одиночных импульсов и динамическом триггере, распределительный регистр, каждый разряд которого содержит схему совпадения, ячейку считывания, подготовки, памяти и передачи, а также линию задержки. Этот распределитель импульсов имеет недостаточные быстродействие и надежность работы.

Цель изобретения - повышение быстродействия и повышение надежности работы распределителя.

В яредлагаемом распределителе ампульсо-в выход каждой схемы совпадения предыдущего разряда соединен со входом ячеек считывания и подготовки Последующего раЗряда распределительного регистра, вход схемы совпадения подключен к соответствующей тактовой шине, выход ячейки передачи предыдущего разряда соединен со входом ячейки считывания последующего разряда, выход ячейки передачи последнего разряда соединен через линию задержки со входом динамического триггера и ячеЙ1кой считывания первого разряда.

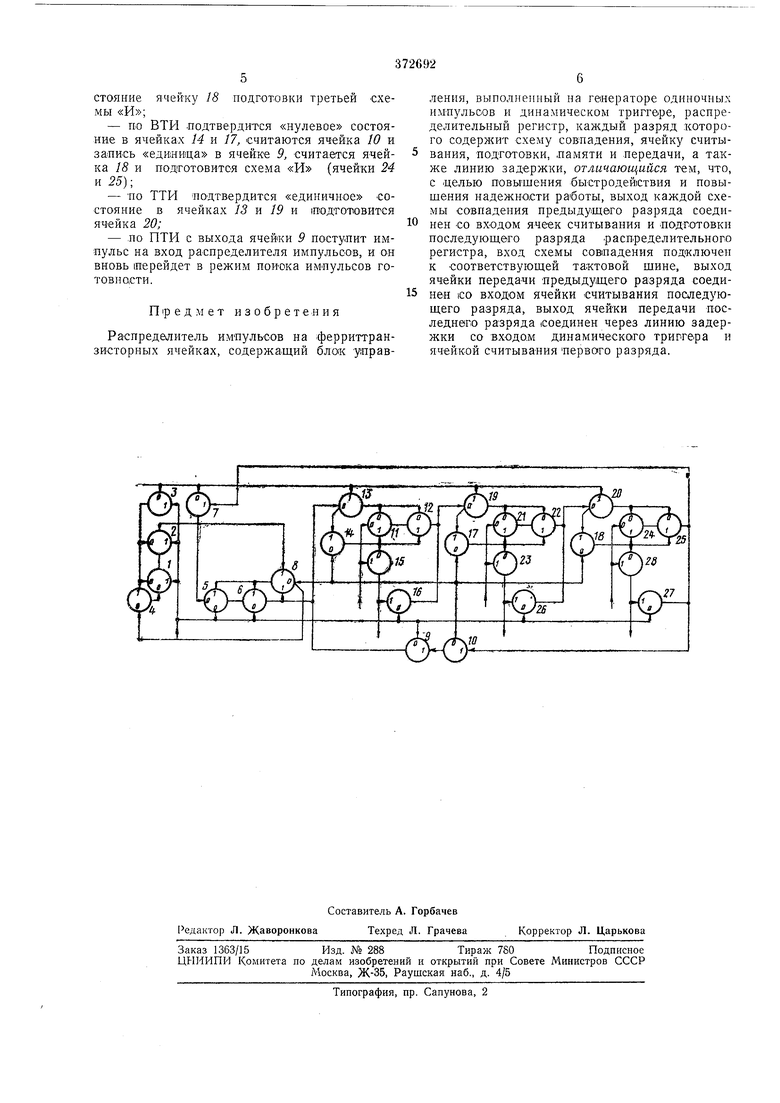

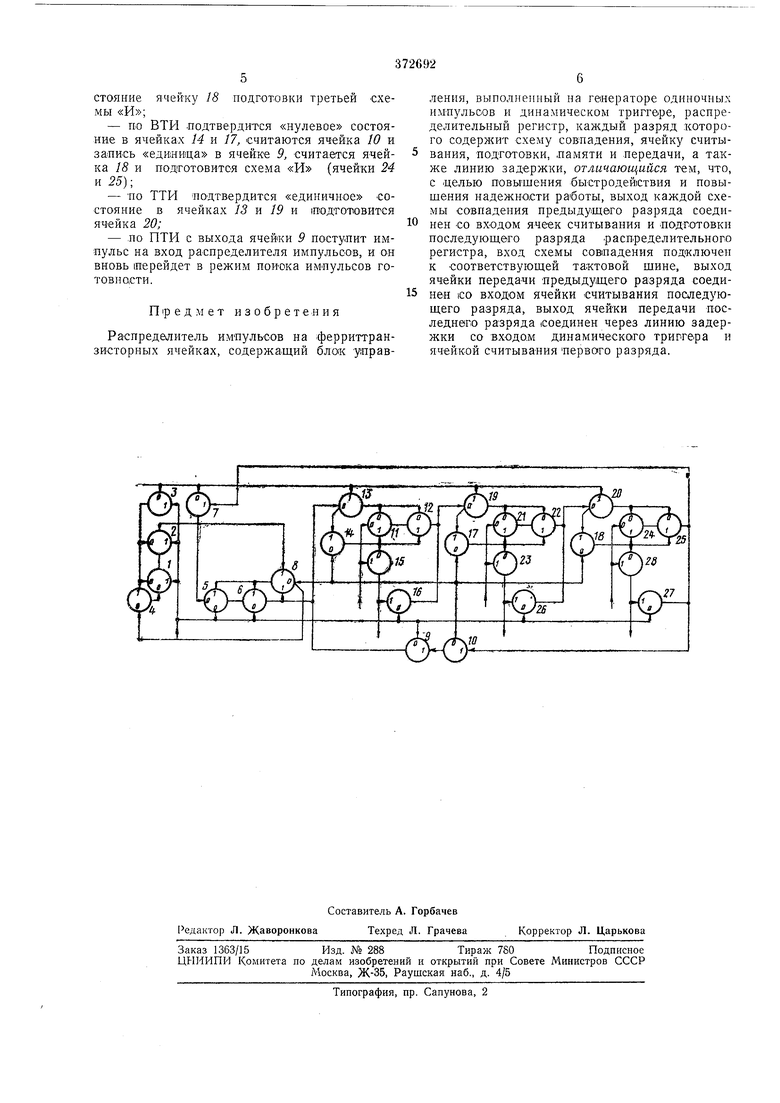

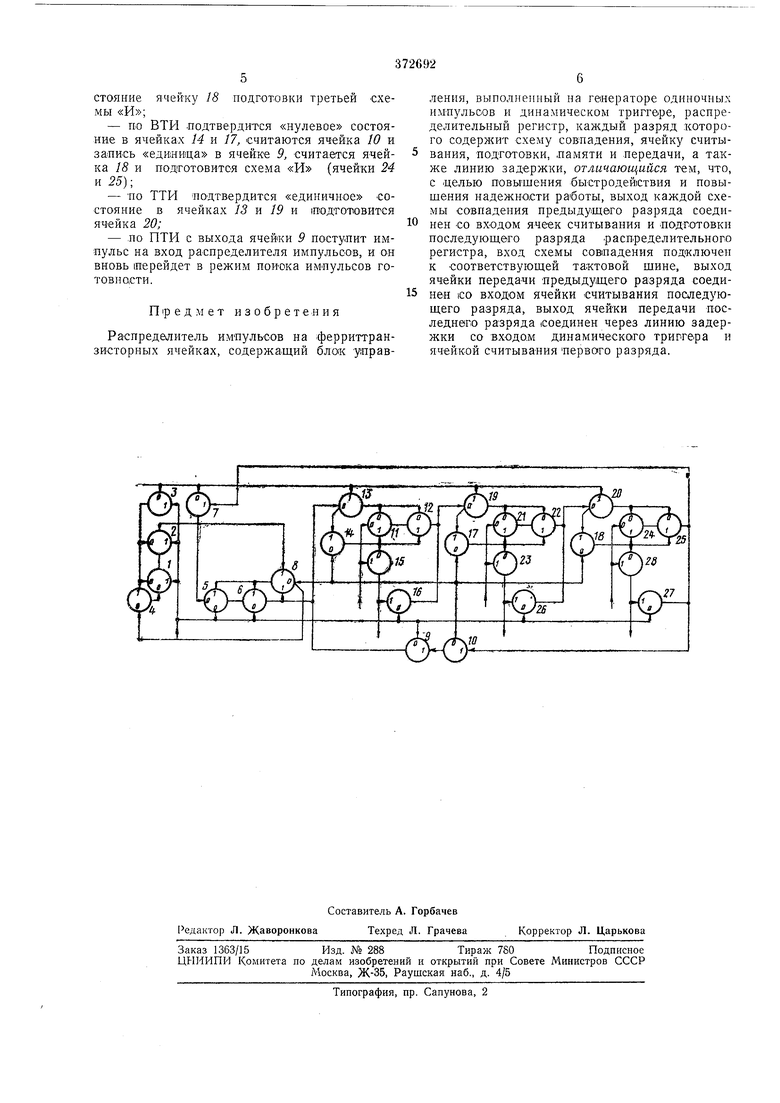

На чертеже приведена схема описываемого распределителя импульсов.

Распределитель имитульсов состоит: из блока управления, который включает в себя генератор одиночных импульсов на схеме «И (ячейки } и 2) Е двух ячейках 3 и 4, динамический триггер (ДТ) на схеме «И (ячейки 5 и 5) и ячейках 7 и 8, линии задержки на ячейках 9 и 10; трех или -более разрядного регистра, каждый разряд которого состоит (например, первый) из схемы «И (ячейки // и 12) и ячеек 13, 14, 15 и 16.

(Блок управления служит для под1готовки распределителя к режиму поиска импульсов готовности информации к выдаче и работает следующим образом:

-по первому тактовому импульсу (ПТИ) происходит подготовка схемы «И (ячейки /

и 2) и ячейки 5 генератора одиночных импульсов (динамический триггер и линия задержки пока «е работают);

-то второму тактовому импульсу (ВТИ) подтверждается «нулевое состояние в ячейке 4;

-по третьему тактовому импульсу (ТТИ) считывается ячейка 5 и с ее выхода схема «И (ячейки 1 и 2) и записывается «единичка в

ячейку 4;

-по ПТИ вновь происходит подготовка схемы «И (ячейки 1 п 2) и ячейки 3;

-по ВТИ считывается ячейка 4 и разрушает схему «И (ячейки / и 5);

- по ТТИ считывается ячейка 3 и вновь

подготавливаеТСя ячейка 4, по этому же такту считывается схема «И (ячейки / и 2) без выдачи информации; этот процесс происходит каждый тоследующий цикл, таким образом генератор одиночного импульса формирует одиночный сигнал, «оторый noiCTyinaeT на динамический триггер; по ТТИ записывается «единичка в ячейку 8 дииамичеокого триггера;

-ПО ПТИ происходит подтверждение «нулевого состояния в Схеме «И (ячейки );

-по ВТИ Считывается ячейка S и с ее выхода происходит установка в «единичное состояние схемы (ячейки 5 и 5);

-по ТТИ «подтверждается «нулевое состояние в ячейке 7;

-по ПТИ считывается схема «И (ячейки 5 и 6), с ее выхода записывается «единичка в ячейку 8 регенерации динамического триггера (ДТ), и Первый импулЬС с него поступает на вход .первого разряда распределителя, при этом по ПТИ с выхода ДТ происходит считывание ячейки /5 и с ее выхода подтверждается «нулевое состояние в схеме «И (ячейки 1} и 12) и запись в ячейку 14;

-: ПО ВТИ считывается ячейка 14 .подготовки схелш «И и с ее выхода подтверждается «нулевое состОЯиие в ячейке М статической памяти; устанавливается в «единичное состояние схема «И (ячейки 11 и 12) и по этому же такту подтверждается «нулевое состояние в ячейках 17 и 18;

1- ПО ТТИ в ячейке 7 (Подтверждается «нуль и в ячейке 13 записывается «единица, в ячейках 19 и 20 она подтверждаеТСя;

-ПО очередному ПТИ с ДТ |ПО|Стулает импульс и вновь считывает ячейку 13, с выхода ее схему «И (ячейки // и 12), с выхода первого разряда «единичка передается на ячейку 19 и считывает ее, в схеме «сИ (ячейки 21 и 22) подтверждается «нуль, а в ячейках 14, 17 записывается «единица ;

-по ВТИ считываются ячейки 14 и 17 и подготавливаются схемы совпадения на ячейках И, 12, 21 и 22, в ячейках 16, 18 и 23 подтверждается «нуль ;

-по ТТИ подтверждается «нуль в ячейке 7, «единица в ячейке 20 и происходит запись в ячейки 13 и 19;

-по очередному ПТИ импульсом с ДТ считы1ваЮТ1СЯ ячейка IS, схема «И (ячейки // и 12), ячейка 19, схема «И (ячейки 21 и 22), ячейка 20, подтверждается «нуль в схеме «И (ячейки 24 и 25) и яроисходит запись в ячейки 14, 17, 18; то каждому ПТИ подтверждается «нулевое состояние в ячейках 16, 26 и 27;

-1ПО ВТИ считывают:ся ячейки 14, 17, 18 и подготавливаются схемы «И во всех разрядах .распределителя, а также подтверждается «нуль в ячей;ках 15, 23 и 28;

-по ТТИ вновь подтверждается «нуль в ячейке 7, записываются «единицы в ячейках 13, 19 и 20;

-по следующему ПТИ импульс С ДТ считывает ячейку 13, а с ее выхода схему «И

(ячейки 11 и 12), с выхода первого разряда импульс поступает на ячейку 19, считывает ее, одновременно считывается схема «И (ячейки 21 и 22), и передает «единицу в третий разряд, где считывается ячейка 20, с ее выхода схема «И (ячейки 24 и 25) и с выхода последнего разряда происходит запись в ячейки 7 и 10, одновременно восстанавливается «единица в ячейках 14, 17 и 18;

- 1ПО ВТИ считываются ячейки 14, 17 и 18, подготавливаются схемы «И (ячейки 11 я 12; 21 и 22; 24 и 2-5), подтверждается «нуль в ячейках 15, 23 к 28 - «единица передвигается из ячейки 10 в ячейку 9, «единица перезаписывается в схему «И (ячейки 5 и 5);

-по ТТИ считывается ячейка 7 и «разрушается схема «И (ячейки 5 и б), Подготавливаются ячейки считывания схем «И (ячейки 13, 19 и 20);

- по очередному ПТИ импульс со схемы ДТ не поступает, считывается ячейка 5 и с ее выхода на вход распределителя импульсов (ячейки 13 и 14) поступает очередной импульс; на этом режим подготовки заканчивается и начинается режим поиска импульсов готовности информации к считыванию.

Режим обнаружения импульса готовности и выдачи соответствую1щего импульса опрюса следующий: импульсы готовности (ИГ) поступают в соответствующий разряд распределителя (возможно одновременное поступление импульсов ГОТОВНОСТИ во все разряды) и заПоминаются в ячейках 15, 23 и 28.

Предположим, что во второй .разряд распределителя синхронно с ТТИ посту1пил ИГ, разрушивший схему «И (ячейки 21 и 22), и запомнился в ячейке 23, тогда:

ПТИ с ячей-ки 9 на ячейки 13 и 14 поступит импульс и считает ячейку 13, с выхода ее считает схему «И (ячейки // и 12) и перейдет -во второй разряд распределителя, считает ячейку 19, с выхода которой считает схему «И (ячейки 21 и 22) без выдачи инфармации, т. е. произойдет останов на том разряде распределителя, в который поступил импульс готовности; по этому же такту произойдет запись «единицы в ячейки 14 и 17;

-по ВТИ считаются ячейки 14 и 17, произойдет подготовка первой и второй схем «И,

что исключит пропуск поступающих по стохостическому закону ИГ, подтвердится «нулевое состоя1ние в ячейках 10 w. 15 vi с ячейки 23 на устройство, выдавшее ИГ, поступит импульс опроса (ИО), при этом произойдет подготовка ячейки 26 передачи;

-по ТТИ подготовятся ячейки 13 и 19, подтвердится «единица в ячейке

- по ПТИ подтвердится «нулевое ,состоякие в ячейках 16 и 27, считает1ся ячейка 26 передачи и с ее выхода импульс поступит на третий .разряд, где считает ячейку 20, с ее выхода схему «И (ячейки 24 и 25), с выхода схемы «И поступит на ячейку / импульс с выхода ячейки 25 установит в «единичное состояние ячейку 18 подготовки третьей схемы

-гю ВТИ подтвердится «нулевое состояние в ячейках 14 и 17, считаются ячейка 10 и запись «еди1НИ1ца в ячейке 9, считается ячейка 18 и подготовится схема «И (ячейки 24 и

-ПО ТТИ подтвердится «единичное состояние в ячейках 13 и 19 и ююдтотювится ячейка 20;

-ло ПТИ с выхода ячейки 9 поступит импульс на вход распределителя импульсов, и он вновь перейдет в режим поиска импульсов готовности.

П ip е д м е т изобретения

Распределитель импульсов на ферриттранзисторных ячейках, содержащий блок уиравления, выполненный на генераторе одиночных импульсов и динамическом триггере, распределительный регистр, каждый разряд которого содержит схему совпадения, ячейку считывания, подготовки, .памяти и передачи, а также линию задержки, отличающийся тем, что, с делью гговышения быстродействия и повышения надежности работы, выход каждой схемы совпадения предыдущего разряда соединен со входом ячеек считывания и подготовки последующего разряда .распределительного регистра, вход схемы совпадения подключеп к соответствующей тактовой щине, выход ячейки передачи предыдущего разряда соединен ico входом ячейки считывания последующего разряда, выход ячейки передачи последнего разряда соединен через линию задержки со ВХОДО.М динамического триггера и ячейкой считывания первого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| ЦИФРОВАЯ ПНЕВМОГИДРАВЛИЧЕСКА: ПРОГРАММНО-СЛЕДЯЩАЯ СИСТЕМА | 1971 |

|

SU428359A1 |

| Электронные вторичные часы с цифровой индикацией | 1983 |

|

SU1170417A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Многоканальное устройство для сбора и обработки информации | 1988 |

|

SU1524078A1 |

Даты

1973-01-01—Публикация