1

Изобретение относится к импульсной технике.

Известен логический элемент «И--ИЛИ/И- ИЛИ-НЕ, содержащий переключатели тока, которые образуют две логические ступени, причем инверсные выходы переключателей тока первой ступени подключены к базам входных транзисторов переключателя тока второй ступени.

Цель изобретения - уменьшение величины управляющего сигнала и получение возможности управлять величиной запаса помехоус1СТОЙЧИВОСТИ.

Для этого в предлагаемом логическом элементе прямые выходы переключателей тока первой ступени подключены к базе опорного транзистора переключателя тока второй ступени, а коллекторные резисторы ибазы опорных транзисторов переключателей тока первой ступени подключены через дополнительный резистор к шине питания.

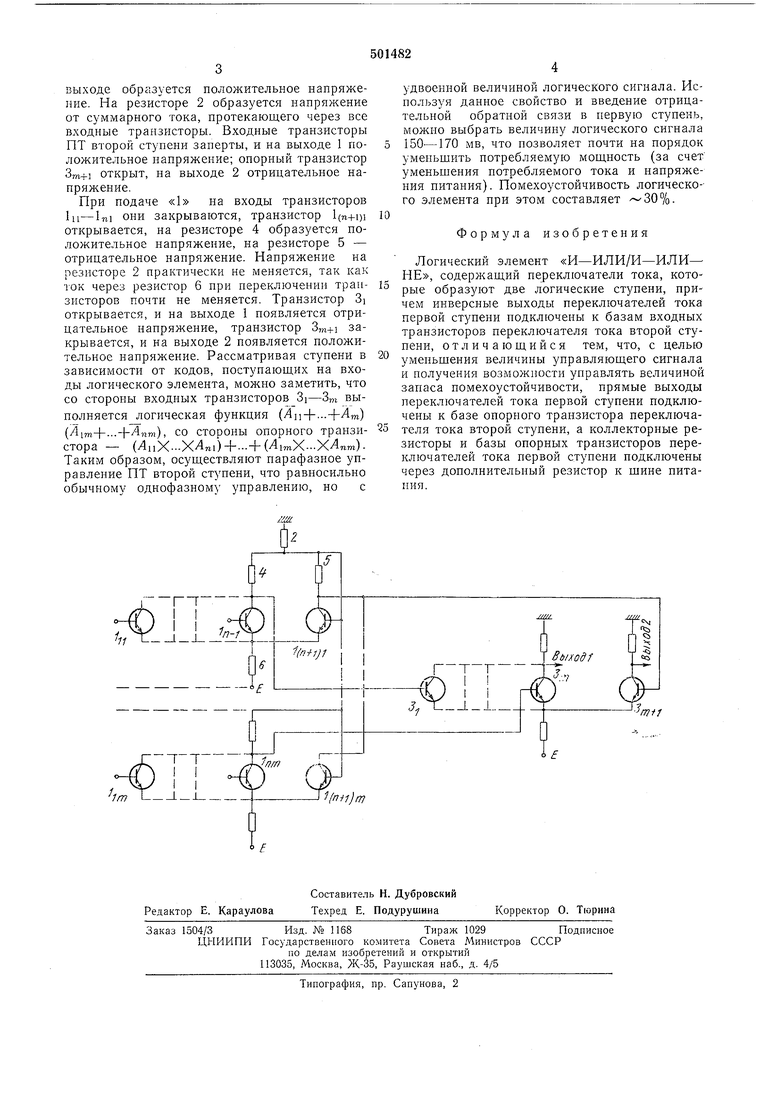

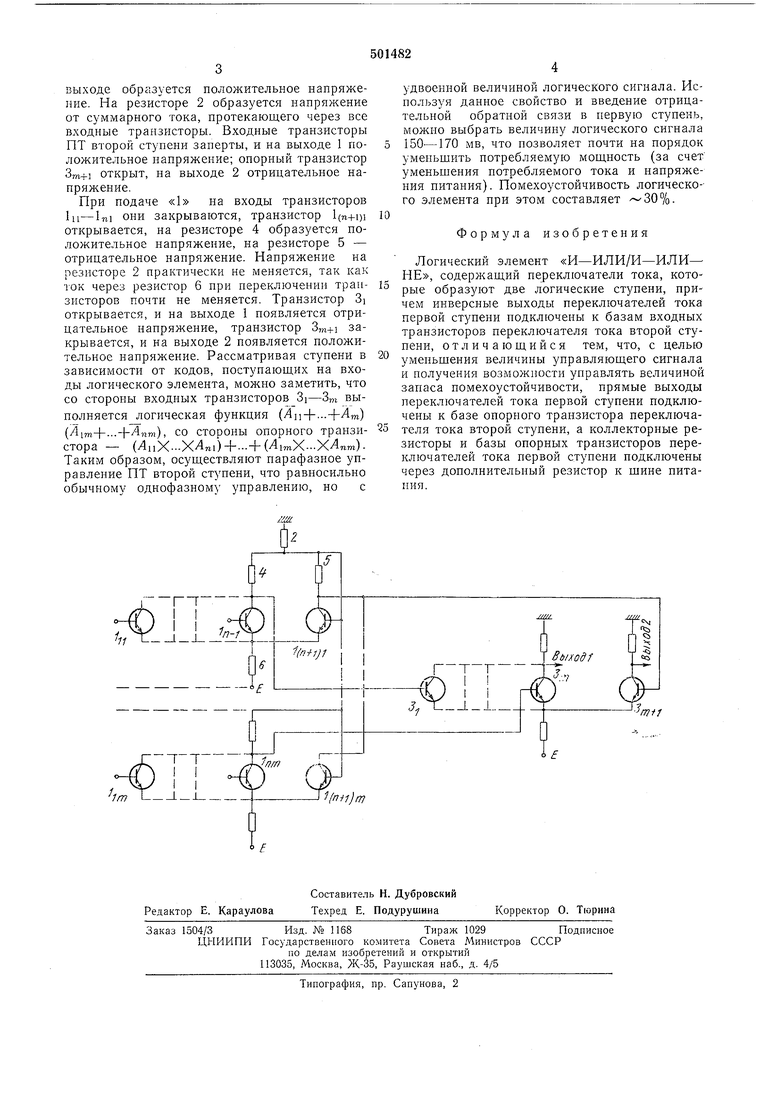

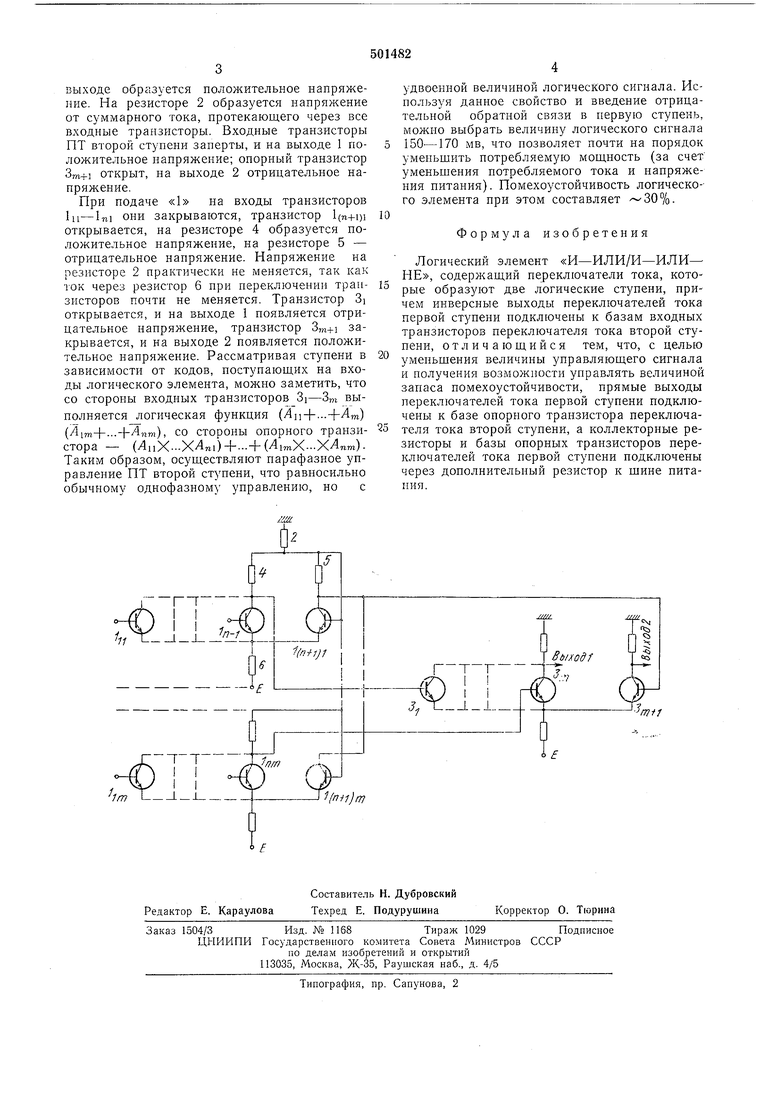

На чертеже приведена схема предлагаемого логического элемента.

Первая логическая ступень «И состоит из т дифференциальных усилителей на п входов (транзисторы , 1(7г+:)т). Базовьш входы опорных транзисторов 1(7г+)1 - l(7i+l)m ДИфференциальных усилителей подключены к общему резистору 2, объединяющему коллекторные цепи транзисторов, что устраняет необходимость использования специального оцорного источника. При этом меняется величина логического перепада напряжения, и опорное напряжение всегда устанавливается в середине между его уровнями.

При количестве входов , чтобы выравнять запасы помехоустойчивости по уровням «О и «1, опорное напряжение можно сместить в положительную сторону.

Вторая логическая ступень «ИЛИ состоит из переключателя тока (ПТ) на т входов. Рассматривая изменение направления тока в эмиттерной точке ПТ в зависимости от кодов, поступающих на входы логического элемента, можно заметить, что со стороны входных транзисторов ПТ выполняется логическая функция (Au + .-.+Anl) (Aim + --- + Anm),

со стороны опорного транзистора - (АпХ..-ХЛп1+...+ (А1тХ-ХЛпт). Таким образом, осуществляется парафазное управление схемой ПТ, что равносильно обычному однофазному управлению, но с удвоенной величиной логического сигнала.

Устройство работает следующим образом.

В исходном состоянии на все входы ПТ первой ступени поданы сигналы логического «О. При этом их входные транзисторы открыты, и на инверсных выходах образуются отрицательные напряжения, опорные транзисторы закрыты, и на прямом объединенном

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| Микромощный логический элементи-или/и-или-HE | 1979 |

|

SU832725A1 |

| Параллельный аналого-цифровой преобразователь | 1989 |

|

SU1762409A2 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1989 |

|

SU1676100A1 |

| Логический элемент и-или-и/и-или-и-не | 1980 |

|

SU907805A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1718270A1 |

| Комплементарный логический элемент и-или/и-или-не | 1978 |

|

SU718929A1 |

| ФОРМАЛЬНЫЙ НЕЙРОН | 1973 |

|

SU375792A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Быстродействующий микромощный логический элемент и-или/и-или-не | 1977 |

|

SU624369A1 |

Авторы

Даты

1976-01-30—Публикация

1973-12-17—Подача