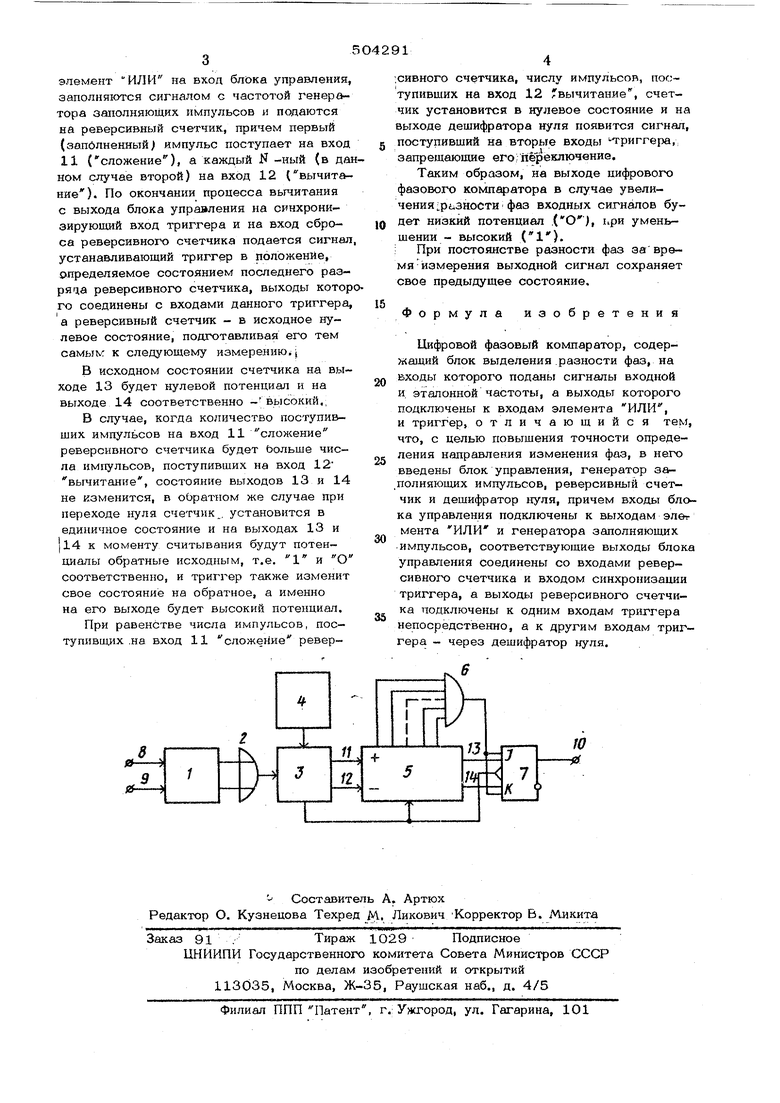

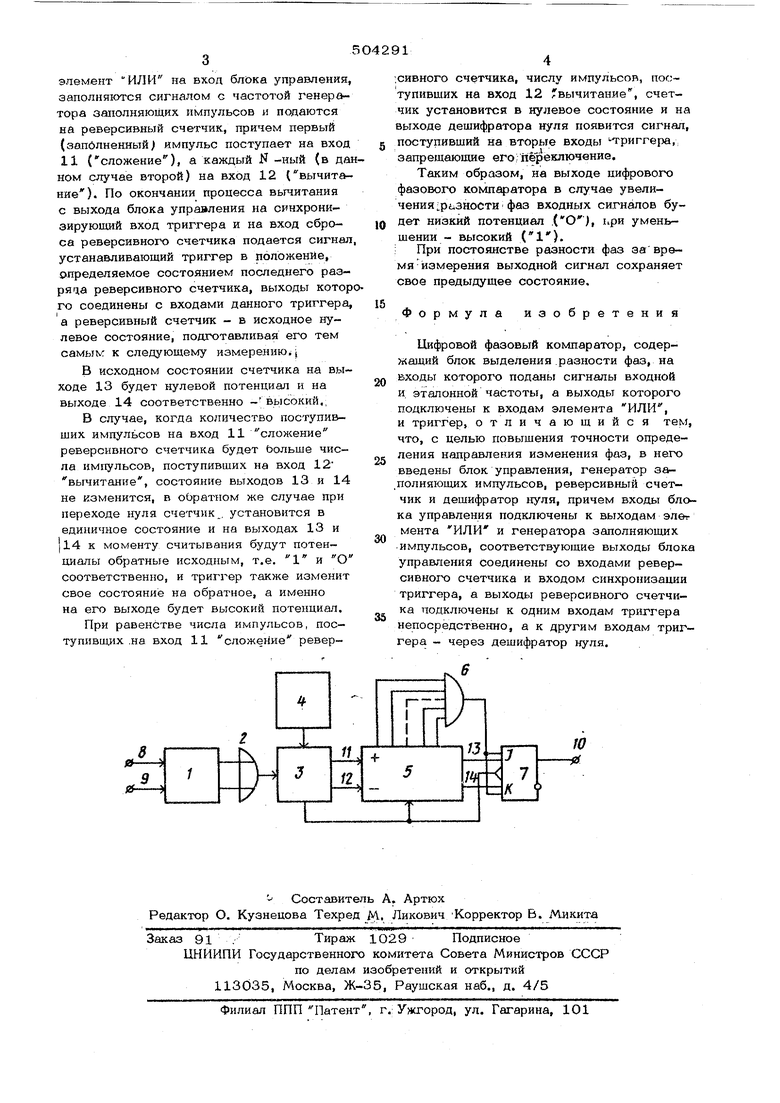

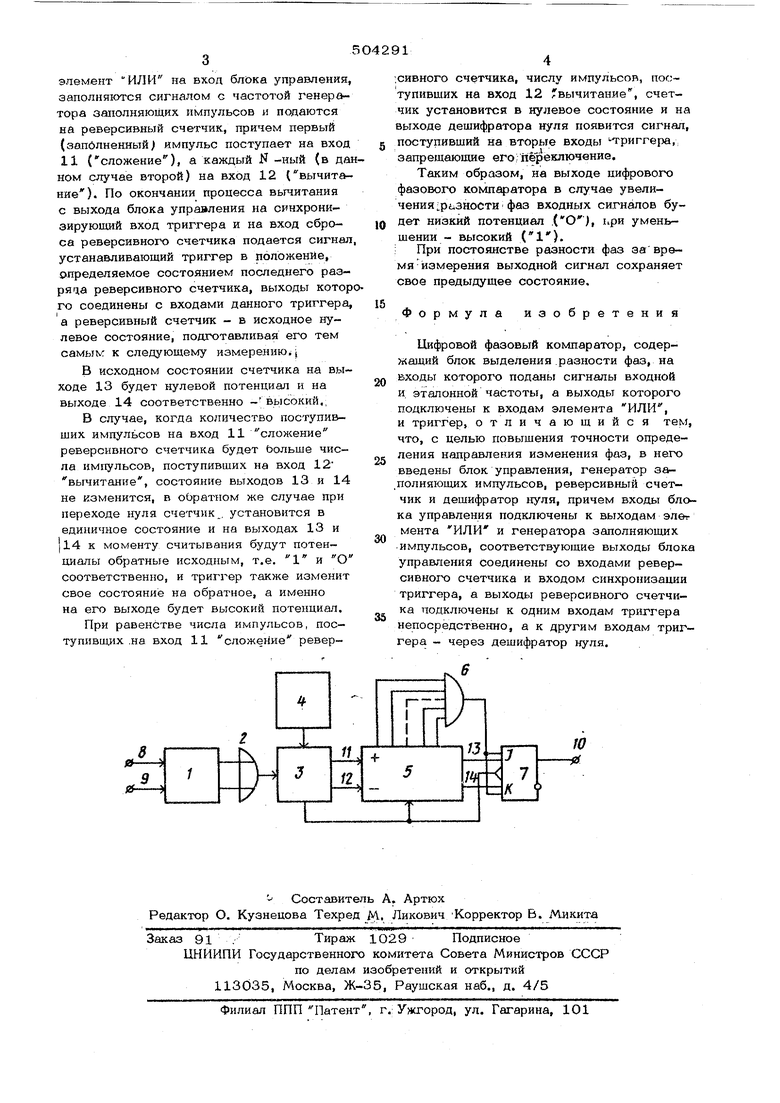

элемент ИЛИ на вход бл&ка управления, заполняются сигналом с частотой генератора зшюлняющих импульсов и подаются на реверсивный счетчик, причем первый {запблненный) импульс поступает на вход 11 (сложение), а каждый N -ный (в данном случае второй) на вход 12 (вычитание). По окончании процесса вычитания с выхода блока управления на синхронизирующий вход триггера и на вход сброса реверсивного счетчика подается сигнал устанавливающий триггер в положение, определяемое состоянием последнего раэряг а реверсивного счетчика, выходы которго соединены с входами данного триггера, а реверсивный счетчик - в исходное нулевое состояние, подготавливая его тем самым к следующему измерению i

В исходном состоянии счетчика на выходе 13 будет нулевой потенциал и на выходе 14 соответственно -высокий,,

В случае, когда количество поступивших импульсов на вход 11 реверсивного счетчика будет Ьольше числа импульсов, поступивших на вход 12 вычитание, состояние выходов 13 и 14 не изменится, в обратном же случае при переходе нуля счетчик. установится в единичное состояние и на выходах 13 и |14 к моменту считывания будут потенциалы обратные исходным, т.е. 1 и О соответственно, и триггер также изменит свое состояние на обратное, а именно на его выходе будет высокий потенциал.

При равенстве числа импульсов, пос- туш1вш.их .на вход 11 сложение ревер;сивного счетчика, числу импульсов, поотупивщих на вход 12 вычитание, счетчик установится в нулевое состояние и на выходе дешифратора нуля появится сигнал поступивший на вторые входы триггера, запрещающие его/переключение.

Таким образом, на выходе цифрового фазового компаратора в случае увеличения р зности фаз входных сигналов будет низкий потенциал .(О), кри уменьшении - высокий (I), i При постоянстве разности фаз за время измерения выходной сигнал сохраняет свое предыдущее состояние.

Формула изобретения

Цифровой фазовый компаратор, содержащий блок выделения .разности фаз, на входы которого поданы сигналы входной и, эталонной частоты, а выходы которого подключены к входам элемента ИЛИ, и триггер, отличающийся тем что, с целью повышения точности определения направления изменения фаз, в не.го введены блок управления, генератор за.полняющих импульсов, реверсивный счетчик и дешифратор нуля, причем входы блока управления подключены к выходам элвг мента ИЛИ и генератора заполняющих импульсов, соответствующие выходы блок упраагшния соединены со входами реверСИВН01ХЭ счетчика и входом синхронизации триггера, а выходы реверсивного счетчика подключены к одним входам триггера непосредственно, а к другим входам триггера - через дешифратор нуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство дискретного управления фазой генератора | 1974 |

|

SU586400A1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Устройство для управления трехфазным выпрямителем | 1988 |

|

SU1529377A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Преобразователь перемещений в код | 1983 |

|

SU1111188A1 |

| Устройство для интегрирования функций | 1984 |

|

SU1242993A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ РЕАКТИВНОЙ МОЩНОСТИ | 1991 |

|

RU2007814C1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1035629A1 |

| Устройство для управления двухтактным преобразователем напряжения | 1987 |

|

SU1624635A1 |

Авторы

Даты

1976-02-25—Публикация

1974-04-17—Подача