Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для функционального преобразования информации, представленной величинами узловых ординат интерполируемой функции.

Известен линейный интерполятор, содержащий декодирующую матрицу резисторов, вход которой подключен к первому входу интерполятора, а выходы соединены с первыми входами соответствующих переключателей аналоговых сигналов, вторые входы которых подключены ко входам приращения аргумента интерполятора; первые выходы переключателей аналоговых сигналов соединены с шиной нулевого потенциала, а вторые выходы - со входом операционного усилителя с резистором в цепи отрицательной обратной связи. Известный интерполятор характеризуется низкой точностью воспроизведения функций и малым быстродействием, ограниченным уровнем 100 - 200 кГц.

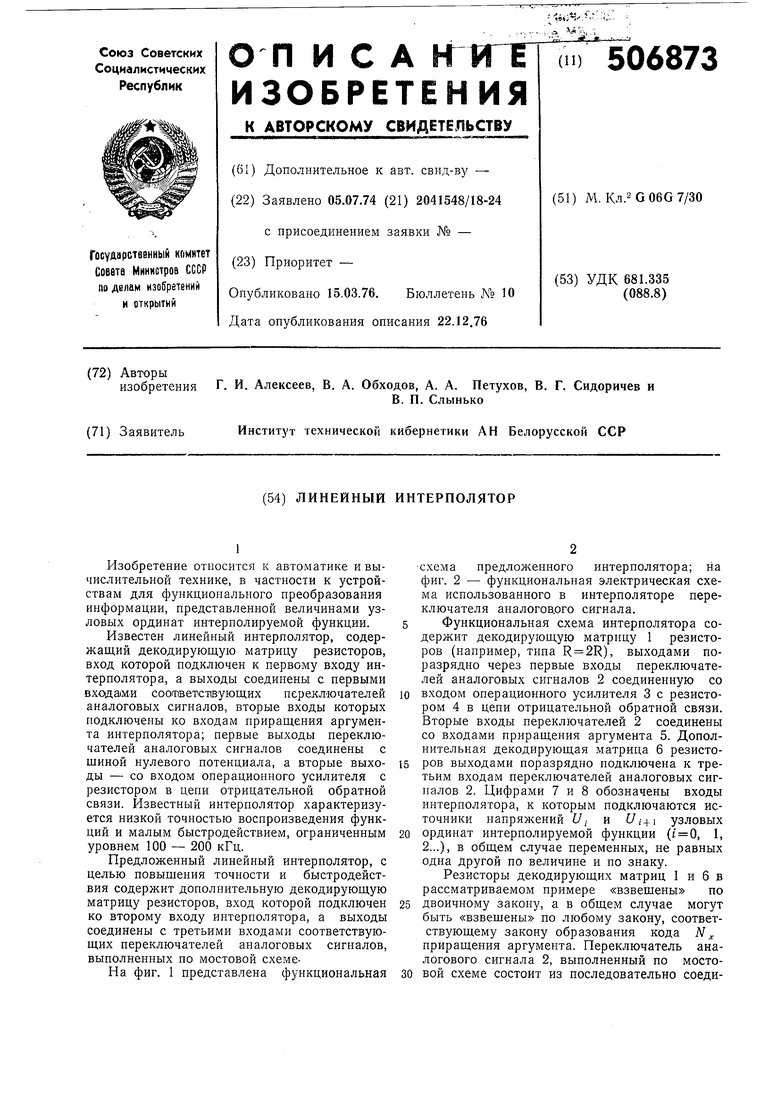

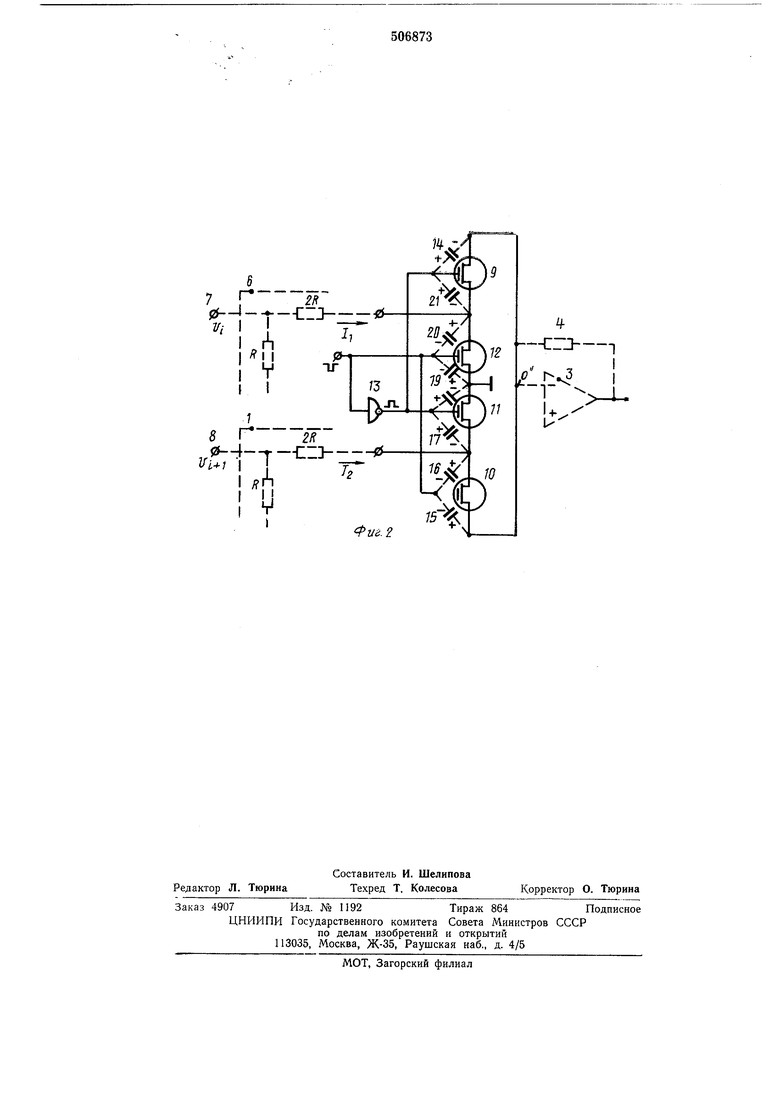

Предложенный линейный интерполятор, с целью повышения точности и быстродействия содержит дополнительную декодирующую матрицу резисторов, вход которой подключен ко второму входу интерполятора, а выходы соединены с третьими входами соответствующих переключателей аналоговых сигналов, выполненных по мостовой схемеНа фиг. 1 представлена функциональная

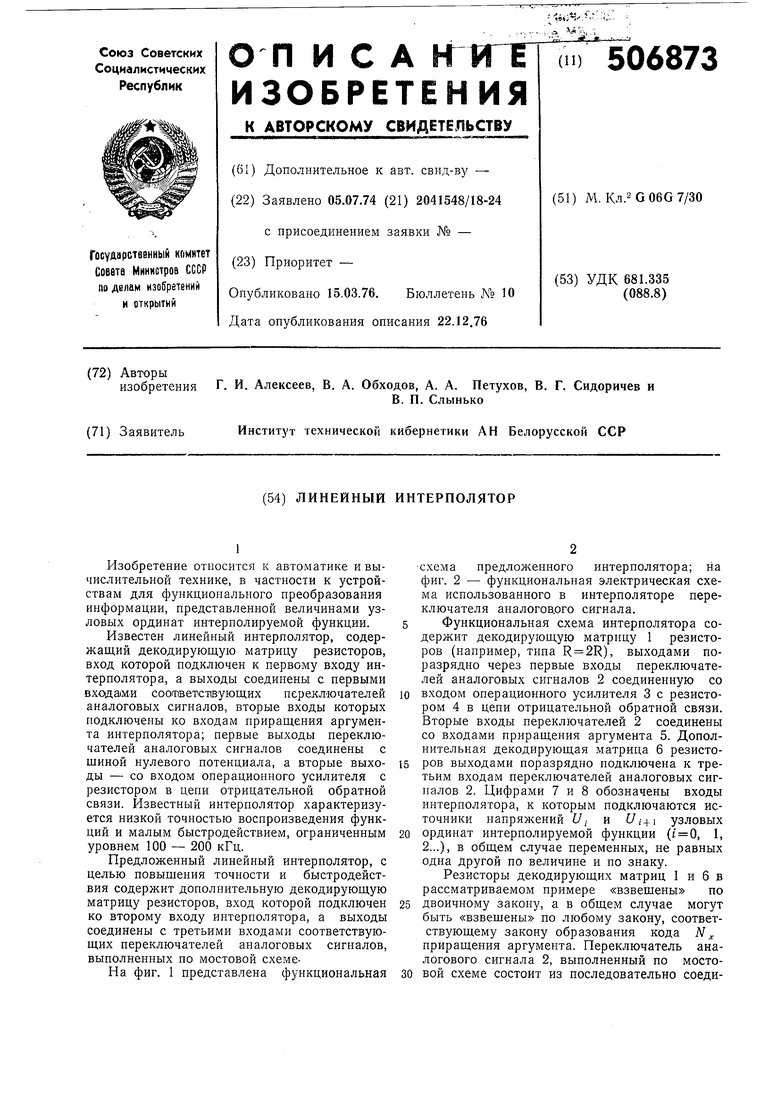

схема предлолсенного интерполятора; на фиг. 2 - функциональная электрическая схема использованного в интерполяторе переключателя аналогов.ого сигнала.

Функциональная схема интерполятора содержит декодирующую матрицу 1 резисторов (например, типа R 2R), выходами поразрядно через первые входы переключателей аналоговых сигналов 2 соединенную со

входом операционного усилителя 3 с резистором 4 в цепи отрицательной обратной связи. Вторые входы переключателей 2 соединены со входами приращения аргумента 5. Дополнительная декодирующая матрица 6 резисторов выходами поразрядно подключена к третьим входам переключателей аналоговых сигпалов 2. Цифрами 7 и 8 обозначены входы интерполятора, к которым подключаются источники напряжений U и f/j+i узловых

ординат интерполируемой функции (f 0, 1, 2...), в общем случае переменных, не равных одна другой по величине и по знаку.

Резисторы декодирующих матриц I и 6 в рассматриваемом примере «взвешены по

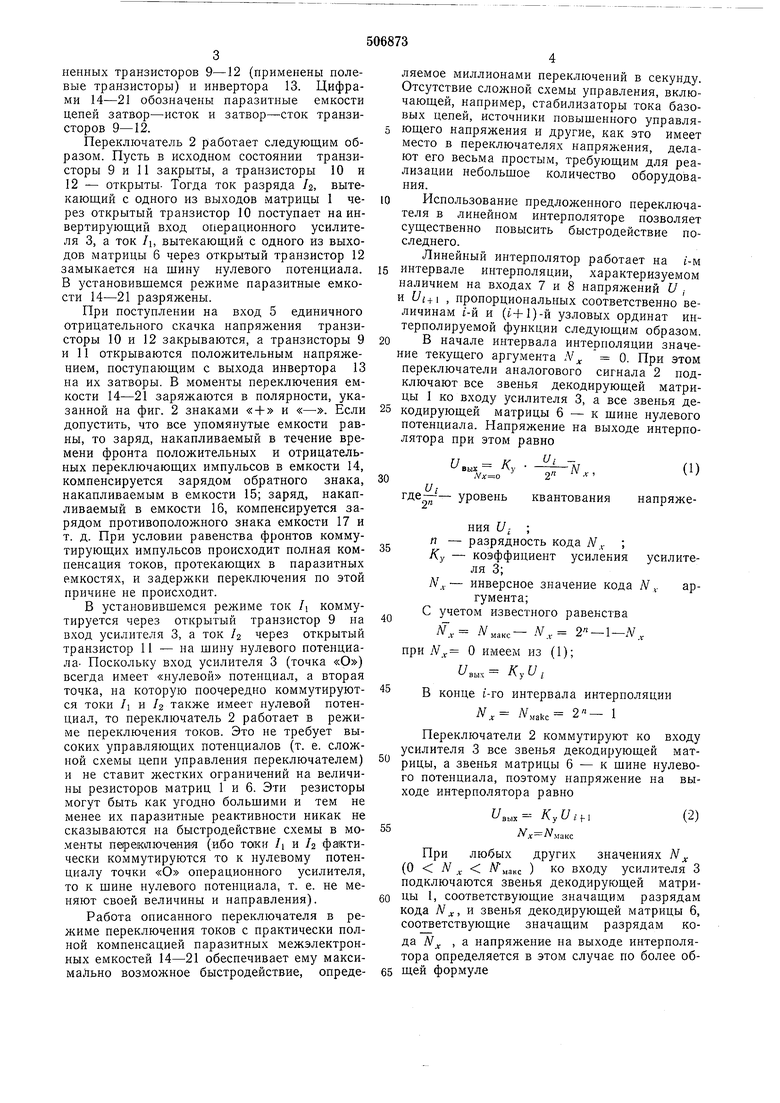

двоичному закону, а в общем случае могут быть «взвешены по любому закону, соответствующему закону образования кода Af приращения аргумента. Переключатель аналогового сигнала 2, выполненный по мостовой схеме состоит из последовательно соединенных транзисторов 9-12 (применены полевые транзисторы) и инвертора 13. Цифрами 14-21 обозначены паразитные емкости цепей затвор-исток и затвор-сток транзисторов 9-12.

Переключатель 2 работает следующим образом. Пусть в исходном состоянии транзисторы 9 и И закрыты, а транзисторы 10 и 12 - открыты. Тогда ток разряда /а, вытекающий с одного из выходов матрицы 1 через открытый транзистор 10 поступает на инвертирующий вход операционного усилителя 3, а ток /1, вытекающий с одного из выходов матрицы 6 через открытый транзистор 12 замыкается на шину нулевого потенциала. В установившемся режиме паразитные емкости 14-21 разряжены.

При поступлении на вход 5 единичного отрицательного скачка напряжения транзисторы 10 и 12 закрываются, а транзисторы 9 и 11 открываются положительным напряжением, поступающим с выхода инвертора 13 на их затворы. В моменты переключения емкости 14-21 заряжаются в полярности, указанной на фиг. 2 знаками « + и «-. Если допустить, что все упомянутые емкости равны, то заряд, накапливаемый в течение времени фронта положительных и отрицательных переключающих импульсов в емкости 14, компенсируется зарядом обратного знака, накапливаемым в емкости 15; заряд, накапливаемый в емкости 16, компенсируется зарядом противоположного знака емкости 17 и т. д. При условии равенства фронтов коммутирующих импульсов происходит полная компенсация токов, протекающих в паразитных емкостях, и задержки переключения по этой причине не происходит.

В установившемся режиме ток 1 коммутируется через открытый транзистор 9 на вход усилителя 3, а ток /г через открытый транзистор 11 - на шину нулевого потенциала- Поскольку вход усилителя 3 (точка «О) всегда имеет «нулевой потенциал, а вторая точка, на которую поочередно коммутируются токи /1 и /2 также имеет нулевой потенциал, то переключатель 2 работает в режиме переключения токов. Это не требует высоких управляющих потенциалов (т. е. сложной схемы цепи управления переключателем) и не ставит жестких ограничений на величины резисторов матриц 1 и 6. Эти резисторы могут быть как угодно большими и тем не менее их паразитные реактивности никак не сказываются на быстродействие схемы в моменты негрекяючениЯ (и,бо токи 1 и /а фактически коммутируются то к нулевому потенциалу точки «О операционного усилителя, то к шине нулевого потенциала, т. е. не меняют своей величины и направления).

Работа описанного переключателя в режиме переключения токов с практически полной компенсацией паразитных межэлектронных емкостей 14-21 обеспечивает ему максимально возможное быстродействие, определяемое миллионами переключений в секунду Отсутствие сложной схемы унравления, включающей, например, стабилизаторы тока базовых цепей, источники повышенного управляющего напряжения и другие, как это имеет место в переключателях напряжения, делают его весьма простым, требующим для реализации небольшое количество оборудования.

Использование предложенного переключателя в линейном интерполяторе позволяет существенно повысить быстродействие последнего.

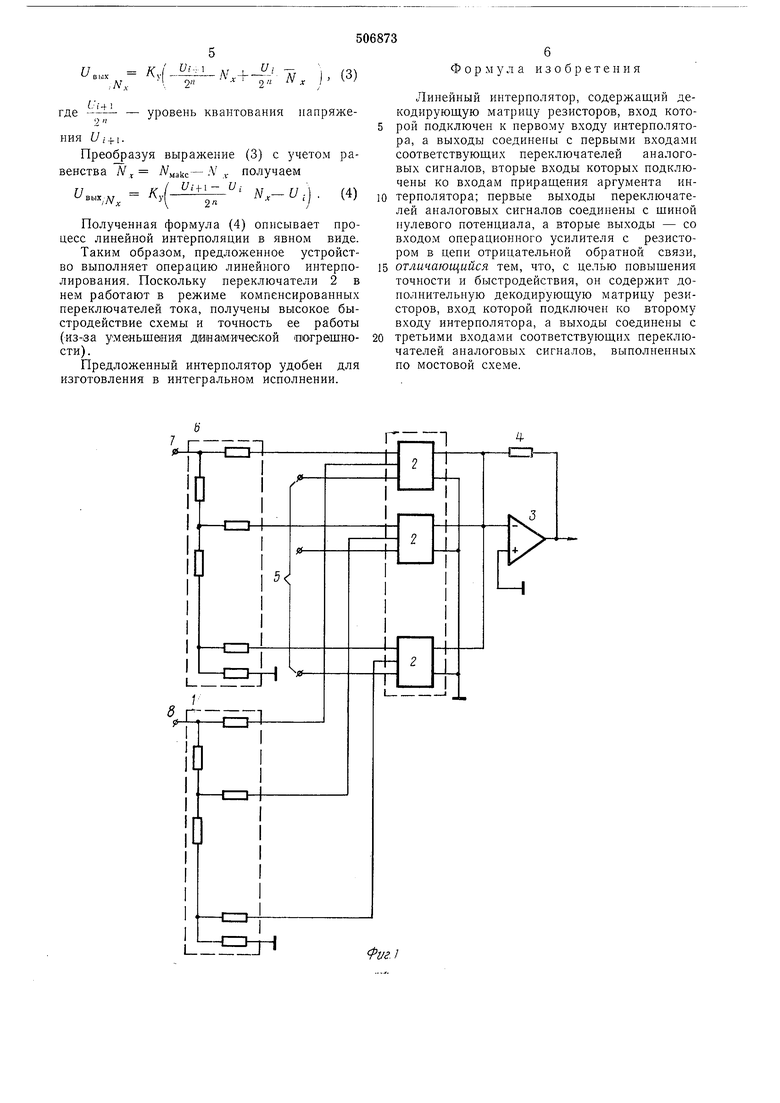

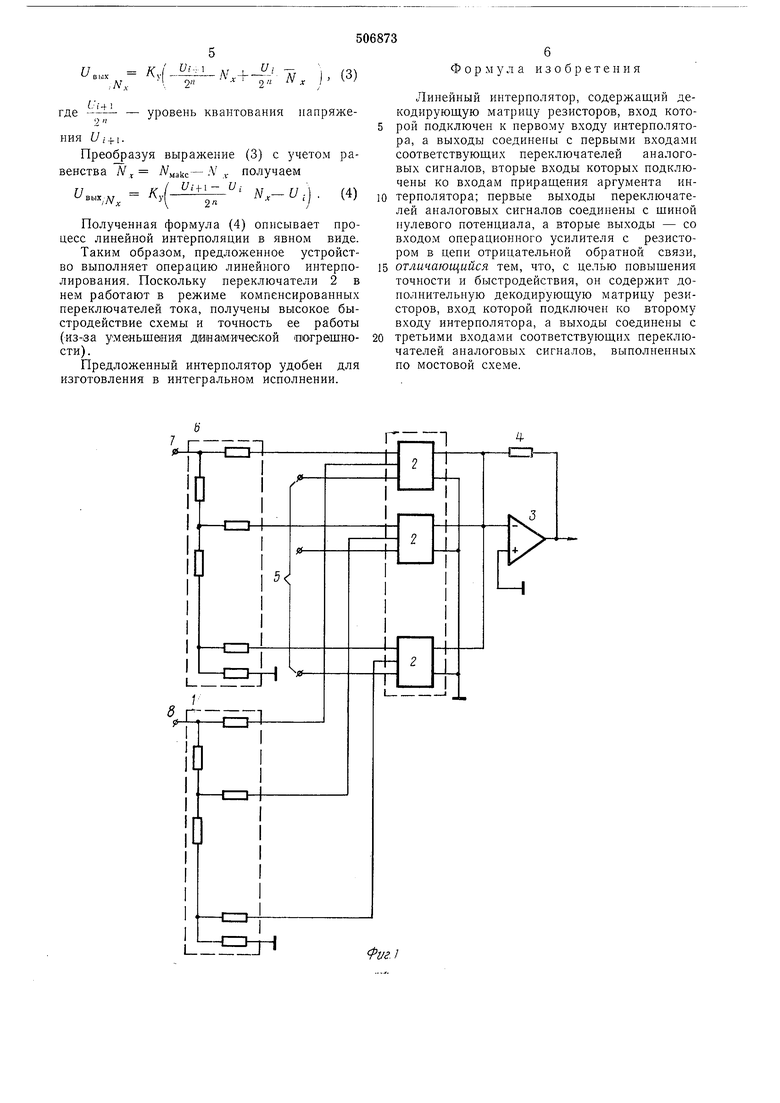

Линейный интерполятор работает на t-м интервале интерполяции, характеризуемом наличием на входах 7 и 8 напряжений И ,Ui , пропорциональных соответственно величинам г-й и (i-f 1)-й узловых ординат интерполируемой функции следующим образом. В начале интервала интерполяции значеие текущего аргумента ,V Q. При этом переключатели аналогового сигнала 2 подключают все звенья декодирующей матрицы I ко входу усилителя 3, а все звенья декодирующей матрицы 6 - к шине нулевого потенциала. Напряжение на выходе интерполятора при этом равно

(1 -.,

t/Bb,X Ку

(1) 2

уровень

квантования напряжения U- ;

л - разрядность кода N ; Ку - коэффициент усиления усилителя 3;

Лд. - инверсное значение кода N,. аргумента;Q С учетом известного равенства

N., V,,,,e- N, 2-l-.V., при N О имеем из (1);

ВЫ. KyU

Sт-1

В конце 1-то интервала интерполяции /V /V , 1

Make 1

Переключатели 2 коммутируют ко входу усилителя 3 все звенья декодирующей матрицы, а звенья матрицы 6 - к шине нулевого потенциала, поэтому напряжение на выходе интерполятора равно

t/Bb,x Ayf//fi(2)

.,s,K

При любых других значениях N . (О N N,sKc ) ко входу усилителя 3 подключаются звенья декодирующей матриЦы 1, соответствующие значащим разрядам кода N, и звенья декодирующей матрицы 6, соответствующие значащим разрядам кода N. , а напряжение на выходе интерполятора определяется в этом случае по более об5 щей формуле iil. vf где ---- - уровень квантования напряжения t/i + i. Преобразуя выражение (3) с учетом равенства N Л/Makc- Л л- получаем f//fi- и i iV.-t/,-l Полученная формула (4) описывает процесс линейной интерполяции в явном виде. Таким образом, предложенное устройство выполняет операцию линейного интерполирования. Поскольку переключатели 2 в нем работают в режиме компенсированных переключателей тока, получены высокое быстродействие схемы и точность ее работы (из-за умеиьшения динам ической иогрешности). Предложенный интерполятор удобен для изготовления в интегральном исполнении. 6 Формула изобретения Линейный интерполятор, содержаш,ий декодирующую матрицу резисторов, вход которой подключен к первому входу интерполятора, а выходы соединены с первыми входами соответствующих переключателей аналоговых сигналов, вторые входы которых подключены ко входам приращения аргумента интерполятора; первые выходы переключателей аналоговых сигналов соединены с шиной нулевого потенциала, а вторые выходы - со входом операционного усилителя с резистором в цепи отрицательной обратной связи, отличающийся тем, что, с целью повышения точности и быстродействия, он содержит дополнительную декодирующую матрицу резисторов, вход которой подключен ко второму входу интерполятора, а выходы соединены с третьими входами соответствующих переключателей аналоговых сигналов, выполненных по мостовой схеме.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1979 |

|

SU849241A1 |

| Интерполятор | 1981 |

|

SU987634A1 |

| Функциональный преобразователь | 1979 |

|

SU805350A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1429173A1 |

| Многоканальный коммутатор аналоговых сигналов | 1982 |

|

SU1034183A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU943853A1 |

| Устройство цифроаналогового преобразования | 1987 |

|

SU1524180A1 |

| Функциональный преобразователь | 1983 |

|

SU1145353A1 |

| Усилитель с управляемым коэффициентом усиления | 1980 |

|

SU907557A1 |

.l

Авторы

Даты

1976-03-15—Публикация

1974-07-05—Подача