Изобретение относится к электронной технике и может быть использовано в приборах и узлах для обработки или преобразования аналоговой информации

Целью изобретения является повьпие- ние точности, стабильности и быстродействия устройства.

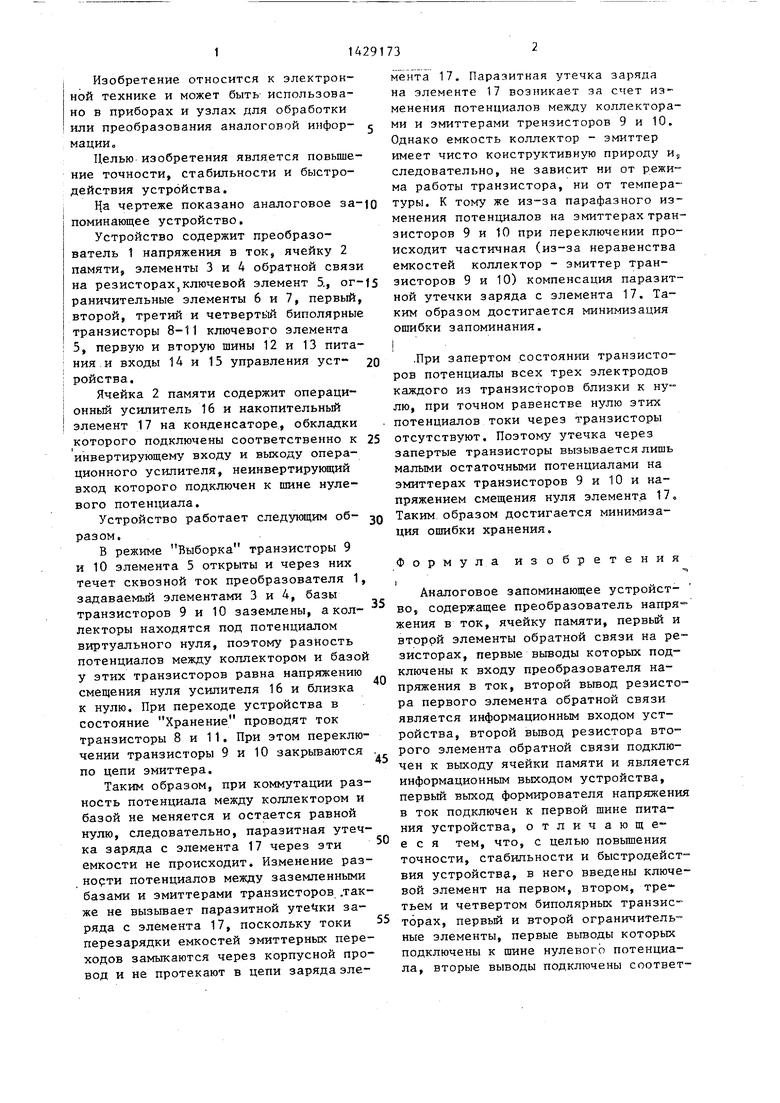

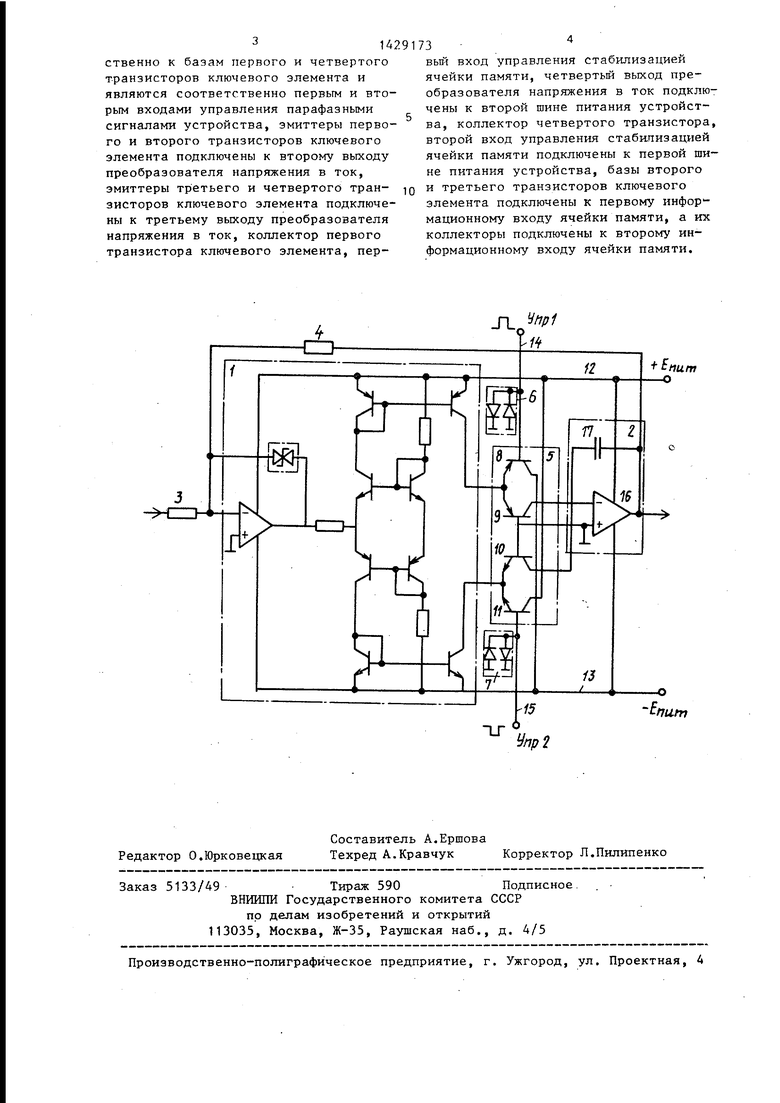

Ца чертеже показано аналоговое запоминающее устройство.

Устройство содержит преобразователь 1 напряжения в ток, ячейку 2 памяти, элементы 3 и 4 обратной связи на резисторах,ключевой элемент 5., ограничительные элементы 6 и 7, первый, второй, третий и четверт1;1й биполярные транзисторы 8-11 ключевого элемента 5, первую и вторую шины 12 и 13 питания и входы 14 и 15 управления устройства.

Ячейка 2 памяти содержит операционный усилитель 16 и накопительньй элемент 17 на конденсаторе, обкладки которого подключены соответственно к инвертирующему входу и выходу операционного усилителя, неинвертирукмций вход которого подключен к шине нулевого потенциала.

Устройство работает следующим образом.

В режиме Выборка транзисторы 9 и 10 элемента 5 открыты и через них течет сквозной ток преобразователя 1, задаваемый элементами 3 и 4, базы транзисторов 9 и 10 заземлены, а коллекторы находятся под потенциалом виртуального нуля, поэтому разность потенциалов между коллектором и базой у этих транзисторов равна напряжению смещения нуля усилителя 16 и близка к нулю. При перекоде устройства в состояние Хранение проводят ток транзисторы 8 и 11. При этом переключении транзисторы 9 н 10 закрываются по цепи эмиттера.

Таким образом, при коммутации разность потенциала между коллектором и базой не меняется и остается равной нулю, следовательно, паразитная утечка заряда с элемента 17 через эти емкости не происходит. Изменение раз- норти потенциалов между заземленными базами и эмиттерами транзисторов .также не вызьгоает паразитной заряда с элемента 17, поскольку токи перезарядки емкостей эмиттерных переходов замыкаются через корпусной провод и не протекают в цепи заряда элемента 17. Паразитная утечка заряда на элементе 17 возникает за счет изменения потенциалов между коллекторами и эмиттерами трензисторов 9 и 10. Однако емкость коллектор - эмиттер имеет чисто конструктивную природу и, следовательно, не зависит ни от режима работы транзистора, ни от темпера0 туры. К тому же из-за парафазного изменения потенциалов на эмиттерах транзисторов 9 и 10 при переключении происходит частичная (из-за неравенства емкостей коллектор - эмиттер тран5 зисторов 9 и 10) компенсация паразитной утечки заряда с элемента 17. Таким образом достигается минимизация ошибки запоминания. I

0 -При запертом состоянии транзисторов потенциалы всех трех электродов каждого из транзисторов близки к ну лю, при точном равенстве нулю этих . потенциалов токи через транзисторы

5 отсутствуют. Поэтому утечка через запертые транзисторы вызывается лишь малыми остаточными потенциалами на эмиттерах транзисторов 9 и 10 и напряжением смещения нуля элемента 17.

Q Таким образом достигается минимизация ошибки хранения.

Формула изобретения

I

Аналоговое запоминающее устройство, содержащее преобразователь напряжения в ток, ячейку памяти, первьй и вторрй элементы обратной связи на резисторах, первые выводы которых подключены к входу преобразователя напряжения в ток, второй вьгеод резистора первого элемента обратной связи является информационным входом устройства, второй вьгоод резистора второго элемента обратной связи подключен к выходу ячейки памяти и является информационным выходом устройства, первый выход формирователя напр51жения в ток подключен к первой шине питания устройства, отличающееся тем, что, с целью повьш1ения точности, стабильности и быстродействия устройства, в него введены ключевой элемент на первом, втором, тьем и четвертом биполярных транзис- 5 торах, первый и второй ограничительные элементы, первые выводы которых подключены к шине нулевого потенциала, вторые выводы подключены соответ5

0

5

0

314

ственно к базам первого и четвертого транзисторов ключевого элемента и являются соответственно первым и вторым входами управления парафазными сигналами устройства, эмиттеры первого и второго транзисторов ключевого элемента подключены к второму выходу преобразователя напряжения в ток, эмиттеры третьего и четвертого тран- зисторов ключевого элемента подключены к третьему выходу преобразователя напряжения в ток, коллектор первого транзистора ключевого элемента, пер

3

-V

вьш вход управления стабилизацией ячейки памяти, четвертый выход преобразователя напряжения в ток подключены к второй шине питания устройства, коллектор четвертого транзистора, второй вход управления стабнпизацией ячейки памяти подключены к первой шине питания устройства, базы второго и третьего транзисторов ключевого элемента подключены к первому инфор - мационному входу ячейки памяти, а их коллекторы подключены к второму информационному входу ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Ячейка памяти для регистра сдвига | 1974 |

|

SU1327186A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| ЯЧЕЙКА ПАМЯТИ НА БАЗЕ ТОНКОСЛОЙНОЙ НАНОСТРУКТУРЫ | 2010 |

|

RU2444806C2 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1991 |

|

RU2020614C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

Изобретение относится к электронной технике и может быть использовано в приборах для обработки или преобразования аналоговой информации. Цель изобретения - повьппение точности, стабильности и быстродействия устройства. Поставленная цель достигается за счет устранения влияния коммутации ключевого элемента на утечку заряда с запоминающего элемента (уменьшение погрешности запоминания) и устранения токов утечки ключевого элемента (уменьшение погрешности хранения) . Быстродействие устройства по- вьш1ается за счет малого времени коммутации токовых переключателей и использования запоминающего элемента меньшей емкости. 1 ил. СЛ

-f/

nutn

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника | |||

| - М.: Мир, 1983, с.286, рис.17-19 | |||

| Аналоговое запоминающее устройство | 1980 |

|

SU881866A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-07—Публикация

1987-01-30—Подача