Изобретение относится к автоматике и вычислительной технике, в частности, к устройствам восстановления формы сигналов, заданных своими значениями, в дискретные момент времени. Известен интерполятор, содержащий суммируницие интеграторы, ключи, запоминающие элементы и сумматоры (1, Недостатками интерполятора являются пониженная точность и сложн(5сть конструктивной реализации. Известен также интерполятор, содержащий генератор импульсов, счетчик, ключи, операцио ный усилитель, интеграторы, сумматор и блок памяти узловых даачений функции и ее про иэводной 2. Шдостаткок данного интерполятора является ограниченная область применения. Наиболее близким к предлагаемому является интерполятор, содержащий выходаой суммирующий интегратор, элемент задержки, соединенный входом с пшной тактовых импульсов, и регистры, первый из которых подключ информациойными входами к информациоша 1

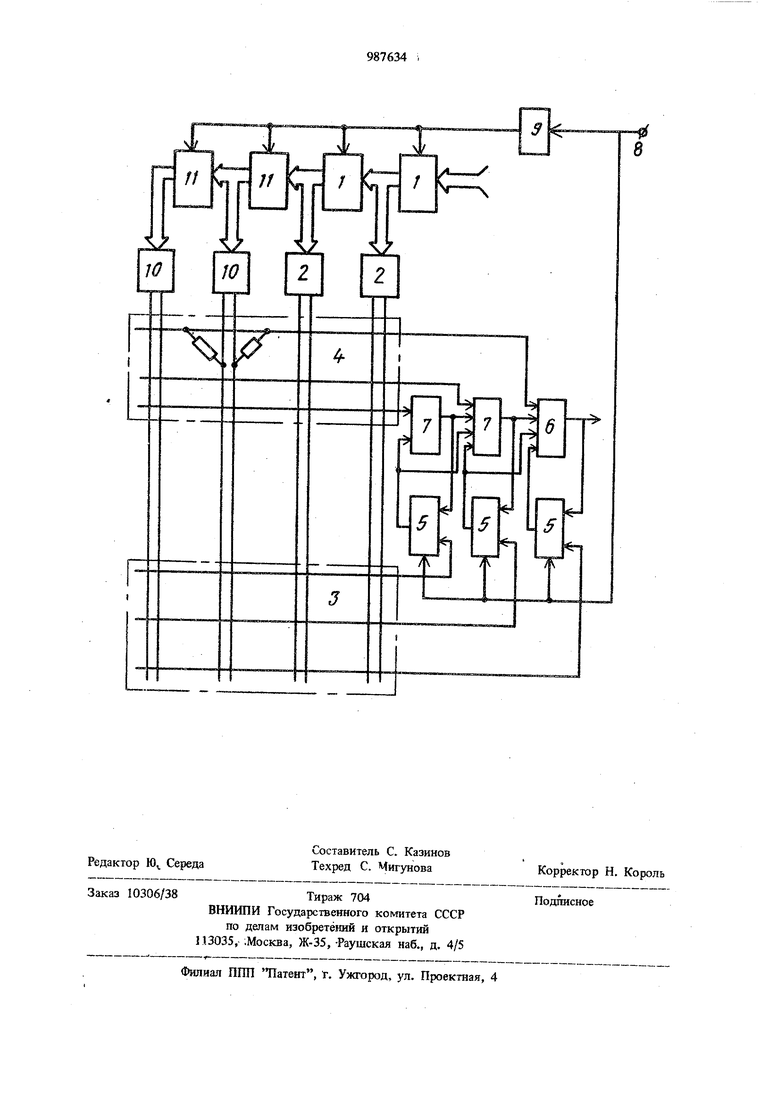

(54) ИНТЕРПОЛЯТОР входам интерполйтора, а выходамн - к входампервого цифро-аналогового преобразователя и к информационным входам второго регистра, соеданенного выходами с входами второго цифро-аналогового преобразователя, причем выходы цифро-аналоговых преобразователей ..,,. подключены к входам выходного суммирующего интегратора, а входы обнуления регистров соединены непосредственно или через элемент задержки сашиной тактовых импульсов 3. Недостатком этого устройства является пониженная точность интерполяции. Цель изобретения - повьпление точности интерполяции. Указанная цепь достигается тем, что в интерполятор, содержащий выходной суммирующий нтегратор, элемент задержки, соединенный входом с ошшй тактовых импульсов, и регистры, пертый из которых подключен информационными входами к информационным входам интертолятора, а выходами к входам первого цифро-аналогового преобразователя и к ийформационным входам второго регистра, соединенного выходами с входами второго 3 98 цифро-аналогового преобразователя, дополнител но введет (п-1) суммирующих интеграторов (где п - степень интерполирующего полинома), п усилителей слежения хранения, две матря ць весовых резисторов, (п-2) цифро-аналоговых преобразователей и (п-2) регистров, перBbrii из которых соединен информационными входами с выходами второго основного регистра, информационные входы каждого i-ro ( - п - 2)1 дополгательного penicтра под1слючены к выходам (i-1) -го Дополнительного регистра, а выходы каждого допоЛ-. ннтельного регистра соединены с выxoдa vш соответствующего дополнительного цифро-аналогового преобразователя, причем прямые и инверсные выходы основных и дополнительных цифро-аналоговых преобразователей подключены к входам двух матриц весовых резисторов, выходы первой из которых соединены с первыми информационными входами усилителей слежения - хранения, а выходы второй матрицы весовых резисторов подключены к первым входам выходного и дополнительных суммирующих интеграторов, причем каждый i-и (} i п - 1)1 дополгаиельный суммирующий интегратор соединен вторым и третьим входами с выходами i-ro и (i-1)-го усилителей слежения-хранения, а четвертым входом с выходом (i-1)-го дополнительного суммируюпдего интегратора и с вторым информационным входом (i-1)-го усилителя слежеНИИ -хранения, а выходной суммирующий интегратор-: по.пхлючен выходом и вторым входом соответствеино к второму информационному входу и выхо,пу п-го усилителя слежения - хра пения, третьим входом к выходу (п-1)-го усилителя слежения-хранения, а четвертым входом к выходу (n-l)-ro дополнительного суммирующего интегратора и к второму инфор мацио шому входу (п-1)-го усилителя слеже1шя-хранения, причем управляющие входы усилителей слежсння-хранения соединены с шиной тактовых импульсов, а выход злемента задержки подключен к управляющим входам регастроВоНа чертеже изображена блок-хсема предлагаемого интерполятора (для случая ). Устройство содержит два основных регистра 1, два основных цифроаналоговых преобразователя 2, первую и вторую матрицы 3 и 4 весовых резисторов, п усилителей 5 слежения хране1шя, выходной суммирзтощий интегратор 6, (п-1) дополнительных суммирзтощих. интеграторов 7, щину 8 тактовых импульсов, злемент 9 задержки, (п-2) дополнительных вдф}ю-аналоговых прео(5разователя 10 и (п-2) дополнительных регистра 1L Первый из основ ных регистров 1 подключен информационными входами к информационным входам интерполя4тора, а выходами - к входам первого основного цифро-аналогового преобраз9вателя 2 и к информационным входам вторюго основного регистра 1, соединенного выходами с входами входного основного цифро-аналогового преобразователя 2. Первый, из дополнительных регистров 11 соединен информационными входами с выходами второго основного регистра 1, информационные входы каждого i-ro ( n - 2) дополнительного регистра 11 подключены к выходам (|-1)-го дополнительного регистра И, а выходы каждого из регистров Ц соединены с выходами соответствующего дополнительного цифро-аналогового преобразователя 10. Прямые и инверсные выходы цифро-аналоговых преобразователей 2 и 10 подключены к входам матриц 3 и 4 весовых резисторов, выходы первой 3 из которых соединены с первыми информационными входами усилителей 5 слежения-хранения. Выходы второй матрицы 4 под1ключены к первым входам выходного суммирующего интегратора 6 и дополнительных суммирующих интеграторов 7. Каждый. i-й ( 1 - i i П - 1) допол1штельньш суммирующий интегратор 7 соединен вторым и третьим входами с выходами i-ro и (-1)-го усилителей 5 слежения-хранения, а четвертым входом с выходом (i-1)-го интегратора 7 и с вторым информационным входом (1-1)-го усилителя 5. Уг равляющие входы всех усилителей 5 подключены к пшне 8 ввода тактовых импульсов и к входу злемента 9 задержки, выход которого соединен с управляющими входами регистров 1 и 11. Выходной суммируюгций интегратор 6 подключен выходом к вторым входам соответственно к второму информационному входу и выходу п-го усилителя 5, третьим входом - к выходу (п-1)-го усилителя 5, а четвертым входом к выходу (n-l)-ro интегратора 7 и к второму информационному входу (п-1)-го усилителя 5. Интерполятор работает следующим образом. Каждый такт начинается подачей на шину 8 стробирующего импульса, по заднему фронту которого злемент 9 задержки формирует управляющий импульс. Этот импульс вызывает сдвиг информации в цепочке регистров 1 и 11 и прием внешней информации в первый из регистров (в том случае, когда каждый из регистров вьшолнен по двухтактной схеме на основном и буферном регистрах, элемент 9 задержки может быть исключен из состава интерполятора). Цифровые значений преобразуются цифре- , аналоговыми преобразователями 2 и 10 и аналоговую форму и поступают на входы матриц 3 и 4. 1%зисторы в матрицах подключаются к прямому и инверсному выходу цифре-аналогового преобразователя в зависимости от знака соответствующего элемента матрицы. Матрица 4 формирует токи, пропорциональные разнос ти между коэффициентами разложения . интерполируемого сигнала по степеням полинома в текущем такте работы и напряжениями, которые действовали на выходах интеграторов 6 и 7 в начале текущего такта. Эти токи поступают на первые суммируюище (токовые) входы интеграторов 6 и 7 и начинается процесс интерполяции. (Сигналы имеющие размер ность напряжений с других входов интегратора через весовые резисторы поступают на токовый вход, где происходит суммирование токов). Первая матрица 3 вычисляет значения напряжений, которые действуют на входе каждого ин тегратора 6 и 7. к концу текущего такта. Сигна лы с выходов этой матрицы поступают на первые информационные входы усилителей 5, на вторые входы которых подаются напряжения с выходов интеграторов 6 и 7. Разность этих напряжений в конце такта становится равной напряжению ошибки на выходе каждого интегратора, которая может явиться следствием дрей фа нуля интеграторов, воздействия помех и дру гах случайных факторов. Каждый усилитель 5 представляет, собой с)гммирушщйй операционный усилитель с электронным ключем, управляемым стробирующим импульсом и заПомш{ающей емкостью на выходе. Он служит для запоминания ахвшитуда ощибки в конце каждого такта работы. Напряжение ощибки с выхоДа усилителя 5 подается в противофазе на вход соответствую щего интегратора и в следующем такте начинает ся процесс исправления ошибки. Кроме того это же напряжение подается и на вход следующего йуммирующего интегратора, поэтому в начале следующего такта на его входе происходит компенсация ощибки. Таким образом, за счет . действия цепи импульсной коррекции, содержащей усилитель 5 слежения -хранения происходит постоянная корректировка и компенсация погрещности. В рассматриваемом случае (п-3) функция, задаваемая своими выборками в четырех точках аппроксимируется поэтйномом третьей степени. На выходе интерполятора воспроизводится каждый раз средний, наибсшее .точный участок аппроксимирующего полинома. Таким образом, пре;ша.гаемый интерполятор по сравнению с известным позволяет повысить точность восстановления функции за счет уменьшения ъщття ощябок и яомех на работу устройства и использования аппроксимирующих полиномов более высокого порядка. Формула изобретения Интертолятор, coдepзkaщий выходаой суммирующий интегратор, элемент задержки , соединенный входом с пгаиой Тактовых импульсов, и регистры, первый из которых подключен информационными входами к информационным входам интерполятора, а выходами к входам первого цифроаналогового преобразователя и к информационным входам второго регистра, соединенного выходами с входами второго цифроаналогового преобразователя, отличающийся тем, что, с целью повьпиення точности интерполяции, в него дополнительно введены (п-1) суммирующих интеграторов (где п - степень интерполирующего полннома), п усилителей слежения. хранения, две мат1жцы весовых резисторов, (п-2) цифроаналоговых преобразователей и (п-2) регистров, первый из которых соеданен информаигионными входами с выходами второго основного регистра, . информационные входы каждого i-ro 2 $ i (п-2) дополнительного регистра подключены к выходам (i-1)-го дополнительного регистра, а выходы каждого дополнительного регистра соединены с входами соответствующего дополнительного цифроаналогового преобразователя, причем прямые и инверсные выходы основных и дополнительных цифроаналоговых преобразователей подключены к входам двух матриц весовых резисторов,.выхода первой из которых соединены с первыми информационными входами усилителей слежения - хранения, а выходы второй матрицы весовых резисторов подключены к первым входам выходного и дополнительных суммирующих интеграторов, прячем каждый ни {1 i (п-1) дополнительный суммирующий интегратор соединен вторым и третьим входами с выходами i-ro и (i-1)-го усилителей слежения-хранения, а четвертым входом с выходом (i-1)-го дополнительного суммирующего интегратора и с вторым информационным входом (i-1)-го усилителя слежения-хранения, а выходной суммирующий интегратор подключен выходомг| и вторым входом соответственно к второму ииформационному входу и выходу п-го усилителя слеженияхранения, третьим входом к выходу (п-1)-го усилителя слежения-хранения, а четвертым входом к выходу (п-1 )-го дополнительного суммир)тощего интегратора и к второму информационному входу (п-1)--го усилителя слежения-хранения, причем управляющие входы усилителей слежшия- хранения соединены с щиной тактовых импульсов, а выход элемента задержки подключен к )травляюишм входам регистров. }1сто шики информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 765821, кл. G 06 G 7/30, 1978. 2.Авторское свидетельство СССР N 851425, кл. G 06 G 7/30, 1978. 3. Авторское свидетельство СССР N 404097, ел. G 06 G 7/28, 1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1983 |

|

SU1142848A1 |

| Интерполятор | 1986 |

|

SU1334167A1 |

| Полиномиальный интерполятор | 1988 |

|

SU1522245A1 |

| Функциональный преобразователь | 1980 |

|

SU879603A1 |

| Функциональный преобразователь | 1980 |

|

SU940169A2 |

| Цифро-аналоговый преобразователь с автоматической коррекцией нелинейности | 1980 |

|

SU951692A1 |

| Аналого-цифровая вычислительная система | 1987 |

|

SU1509955A1 |

| Устройство для автоматического управления (его варианты) | 1984 |

|

SU1249481A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

| Устройство для автоматического измерения шумов | 1987 |

|

SU1479896A1 |

Авторы

Даты

1983-01-07—Публикация

1981-04-17—Подача